# LCTPC DAQ Software

Gilles De Lentdecker (Brussels)

Ulf Mjornmark (Lund)

• ]

#### DAQ currently in use

- ALTRO

- AFTER

- TDC

- Muros2 for Timepix

- Silicon Envelope

#### Status:

- All systems are standalone

- All systems have local online monitoring tools

- Converters to LCIO exist for all data formats

- Offline reconstruction with MarlinTPC has started for all systems

- In the following I will focus on the ALTRO system

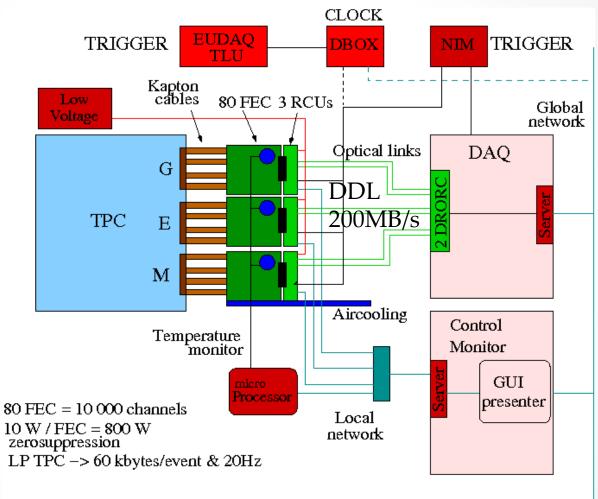

# Current ALTRO DAQ HW (Ulf)

Reminder, the readout is based on the ALICE system:

Some features:

FEC = Front End Card (modified, programmable amplifier)

RCU= Readout Control Unit (modified trigger/clock inputs

DRORC = Data ReadOut Receiver Card

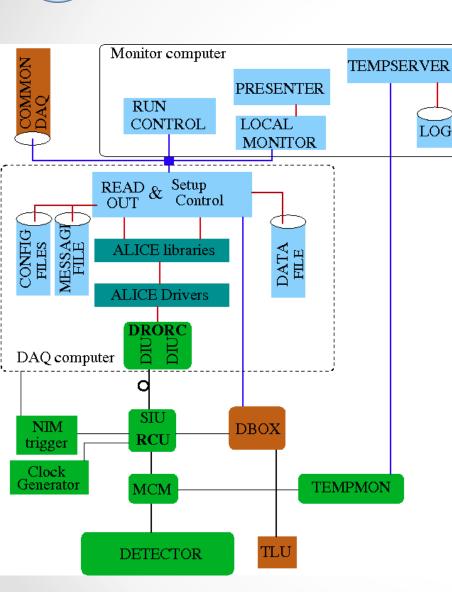

## Current ALTRO DAQ SW (Ulf)

Low level software: ALICE drivers and libraries to communicate with the DRORC and the FEC through DDL

- DAQ software: plain C-code (based on ALICE code)

- Control: JAVA GUI

- Monitor: ROOT

- Brown boxes = still missing:

- TLU (EUDAQ)/DBOX: events lost

- No interface to a common DAQ

WHAT WOULD BE THE COMMON DAQ?

# Hardware scenarios

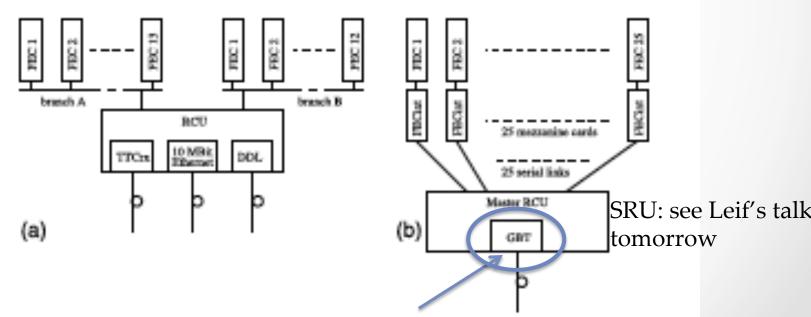

### ALICE HW developments

- As other LHC experiments, ALICE and its TPC will undergo several upgrades, the earliest will be minor (e.g no change to detector & FEC), the latest (>2018) will be major (new TPC)

- Although LCTPC is developing its sALTRO FEC, we can take advantage of the ALICE upgrades:

- First upgrade:

- Replace RCU+SIU+DCS (bus-architecture) by new SRU (star-network), development from RD51 SRS (Scalable Readout System)

GBT and Versatile link -> micro-TCA based development by CERN

#### ALICE HW developments

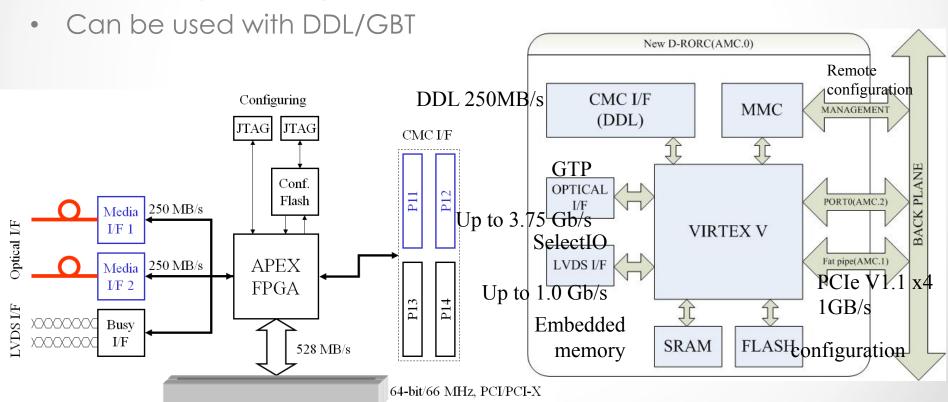

- ALICE is also working on the development of a new DRORC with up to 12 links per PC slot.

- the future DDL link will have a bandwidth of 10 Gb/s and that the I/O bus used will be PCIe with a bandwidth of 1 GB/s per lane.

7

#### Brussels proposal

- sALTRO should be backward compatible with current system

- Implement a new DRORC on an micro-TCA Advanced Mezzanine Card (AMC); I/O bus used will be PCIe

- Keep current RCU+SIU

- DAQPC replaced by micro-TCA carte

# DAQ Software scenarios

#### DAQ SW scenarios

- From the previous section, it is clear that we will remain strongly linked to ALICE HW, therefore the current DAQ software which is continuously updated by Ulf is well suited for LPTPC test beams

- However, one of the task of AIDA (WP8.6.2) is to build a common DAQ system, that is missing in current system

- EUDAQ is a candidate, however we did not succeed so far to migrate the current system into EUDAQ

- In addition other candidates are proposed by other subdetectors

- o CALDAQ

- Or by outsiders like CMS

- o XDAQ

- According to AIDA project by the end of 2012, WP8.6.2 should provide a document with the technical characteristics for a common DAQ

- Bottomline: although the current LCTPC DAQ SW based on ALICE SW and libraries is Ok for the moment, we may have to migrate soon to a new framework still to be defined

- o Brussels hopes to have 0,25 FTE for that task soon

# Summary

| FEE     | ALTRO                             | sALTRO                                     |

|---------|-----------------------------------|--------------------------------------------|

| DAQHW_1 | ALICE RCU+SIU+DLL<br>+DRORC (PCI) | SRU + RD51 SRS +DRORC (PCIe)               |

| DAQHW_2 |                                   | ALICE RCU+SIU+DLL+DRORC (PCIe in microTCA) |

| DAQSW_1 | Lund system based on ALICE        | Upgrade of Lund system based on ALICE      |

| DAQSW_2 |                                   | EUDAQ/CALDAQ/XDAQ/?                        |