# Wing LDA

André Welker

Lennart Adam, Bruno Bauss, Volker Büscher, Reinhold Degele, Karl Heinz Geib, Sascha Krause, Yong Liu, Lucia Masetti, Phi Chau, Uli Schäfer, Rouven Spreckels, Stefan Tapprogge, Rainer Wanke

CALICE Collaboration Meeting DESY Hamburg, 21. March 2013

## Position of the LDA

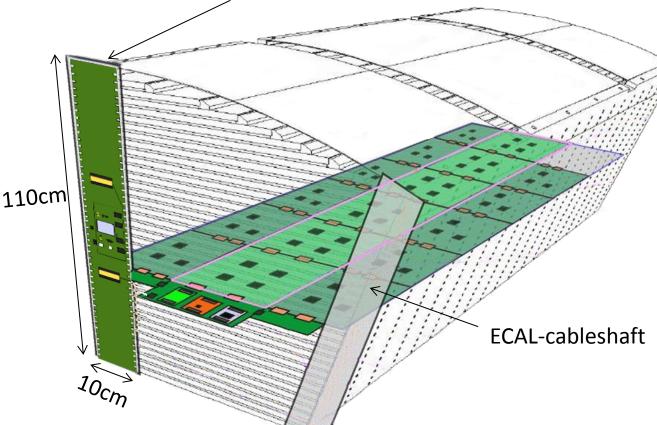

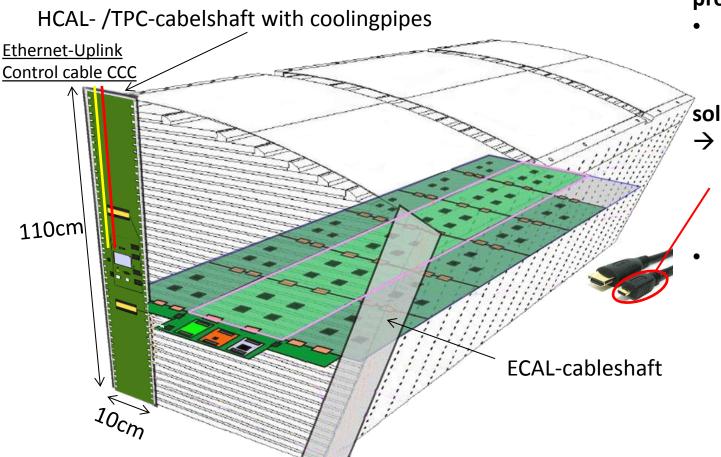

LDA integrated in the 10x10cm cableshaft:

HCAL- /TPC-cabelshaft with coolingpipes

### challenges: problems:

- LDA outside of the detector

- → 96 cables in the cableshaft

### solution/problem:

- 110 cm PCB

- → timedelay between each layer (up to 5ns)

- solution:

- on-board-electronic regulates timing differences

## Position of the LDA

### LDA integrated in the 10x10cm cableshaft:

### challenges: problems:

- Pitch between the 48 layers depends on (18/23 mm for W/Fe)

solution:

- → Smallest possible HDMI micro connector

- Now only

One Ethernet cable

One control cable

in the detector

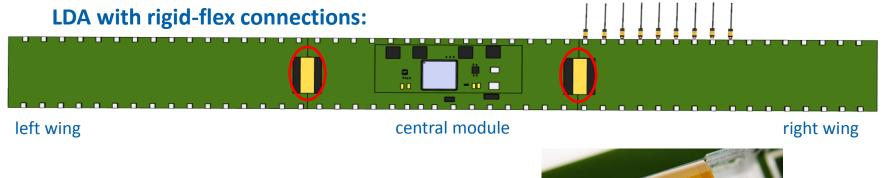

### **Active and Passive**

### LDA consists of 4 parts:

1. Three passive PCBs:

The 96 connectors are on these PCBs.

2. One active PCB:

it is a daughter module for tests and fast repairs.

### Mechanic and flexibility:

### rigid-flex connection

4

The first PCB:

1. Wing with 17 HDMI-connectors routed:

Wing-LDA

The second PCB:

2. Center PCB with 12 HDMI-connectors:

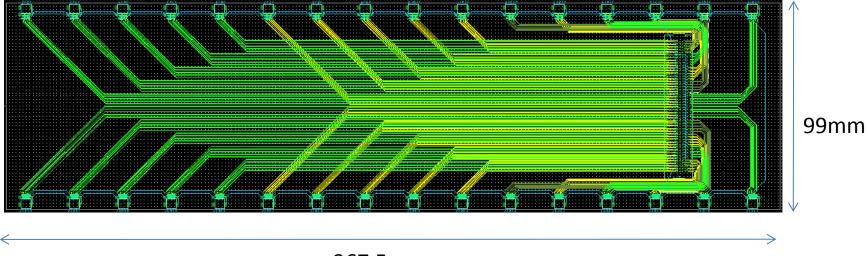

### LDA Layout

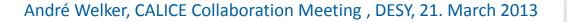

**Passive PCB:**

#### 1. Wing with 32 HDMI connectors:

367,5mm

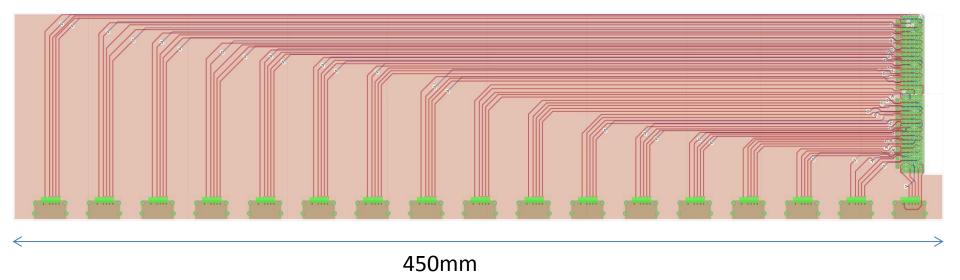

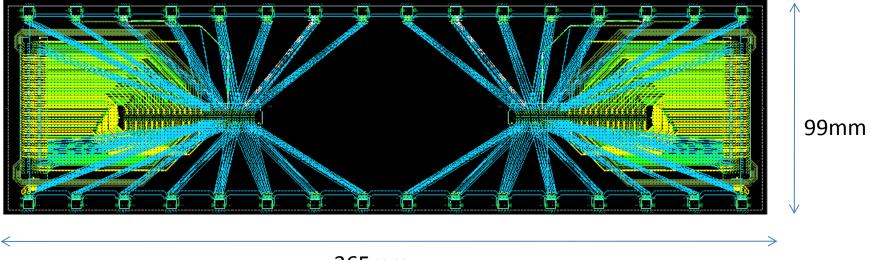

### LDA Layout

#### **Passive PCB:**

#### 2. Central module with 32 HDMI connectors:

365mm

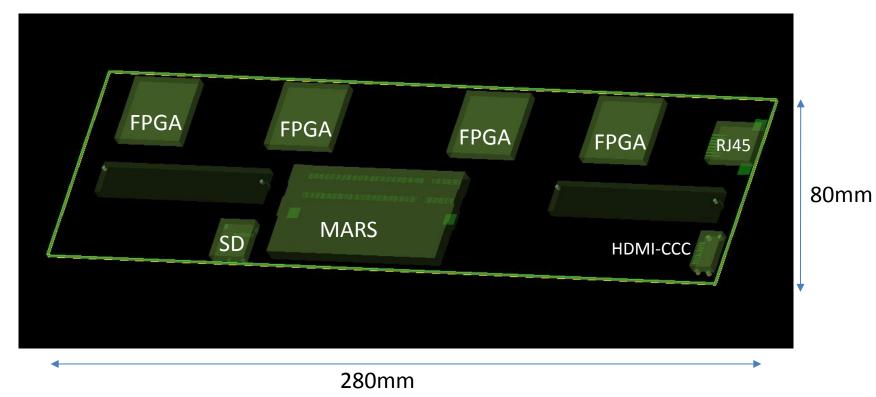

## LDA Layout

### **Active PCB:**

3. Daughter module with 4 FPGAs and a Mars module:

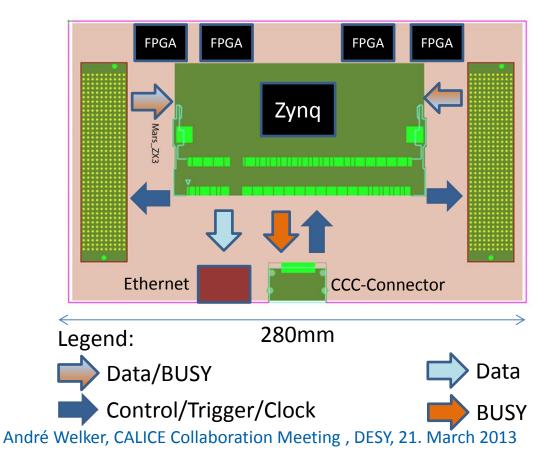

## LDA

### **Active PCB:**

### 3. FPGA daughter module

#### **Peculiarity:**

- Manages 1100 signals and sends them over the Ethernet

- Has a Zynq processor who

- has implemented an Arm9 dual core (with Linux)

- and one FPGA

- Same module as CCC

- LDA collects parallel data from 96 detector layers and leads the clock to each of them without a timing delay

- 80% of the LDA design is finished

- Order the PCBs in 1 week

- Firmware will be finished in 1 month

- Software is finished

- Ready to readout two full ILD detector segments with 48 layers each

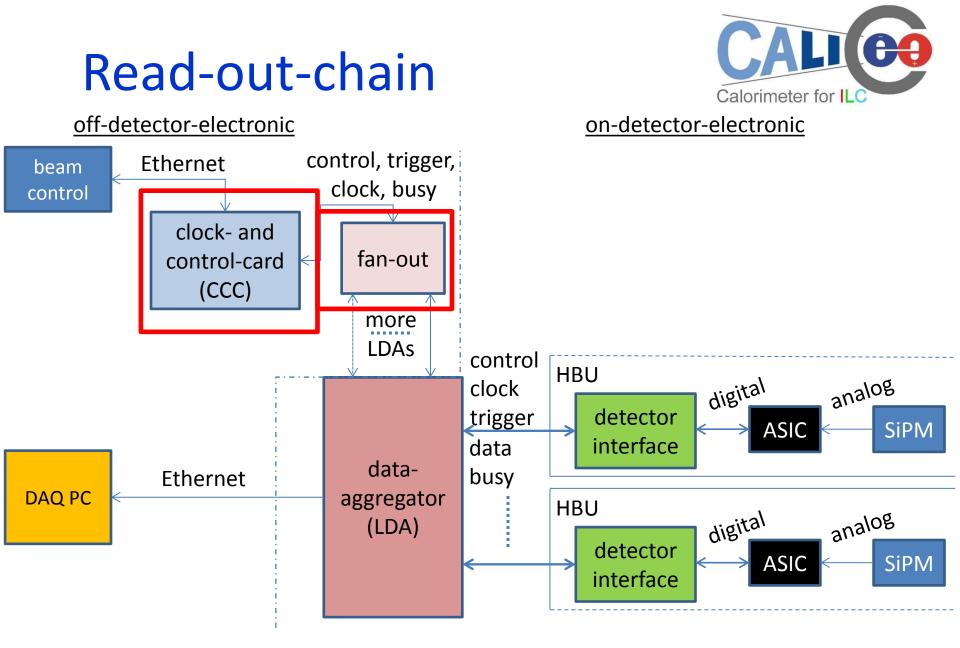

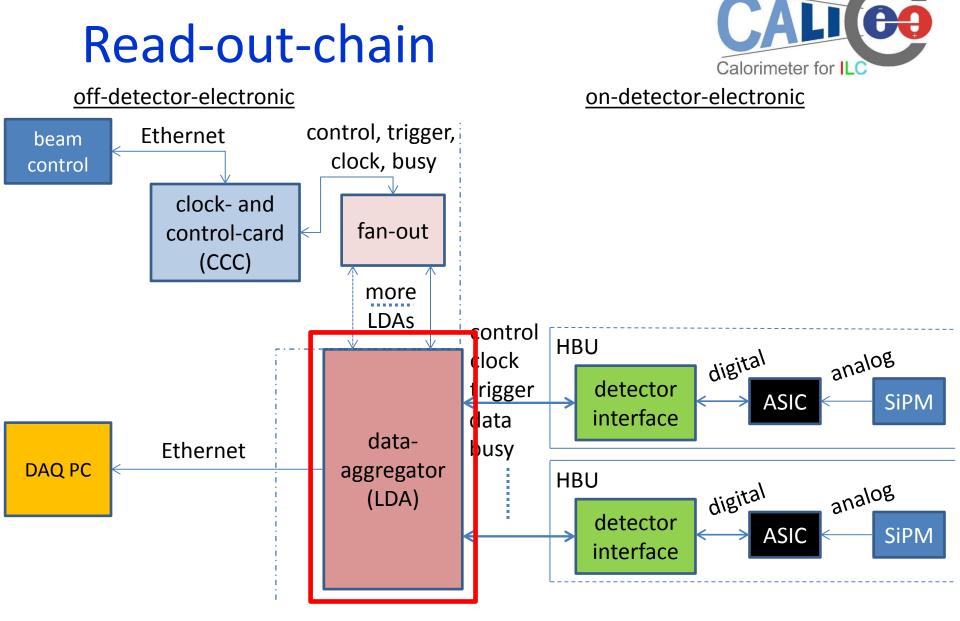

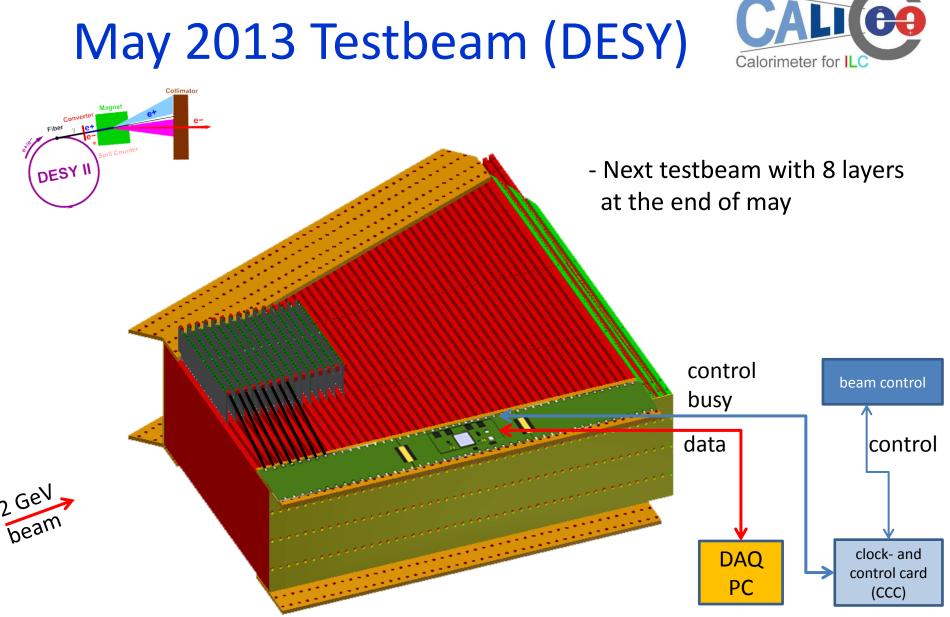

### Integration of CCC and LDA

- Steps:

- 1. Read-out data and send slow control data from the HBU layers as before over USB, but integrate the CCC for clock, trigger and busy signals

- 2. Read-out data by USB but send slow control data, clock, busy, trigger over the CCC

- 3. Integrate the LDA for data read-out instead of the USB, without interference from us in the regular data acquisition

- 4. Firmware and software will be written by us, so we don't interrupt the manpower on the DIF side

### Thank you for your

### attention!