## **Topics**

- Thin BGA

- SKIROC test board

- Software EUDAQ/xDAQ

- Finite state machine (just configure/run)

- Shipment

- DIF(/LDA) FPGA

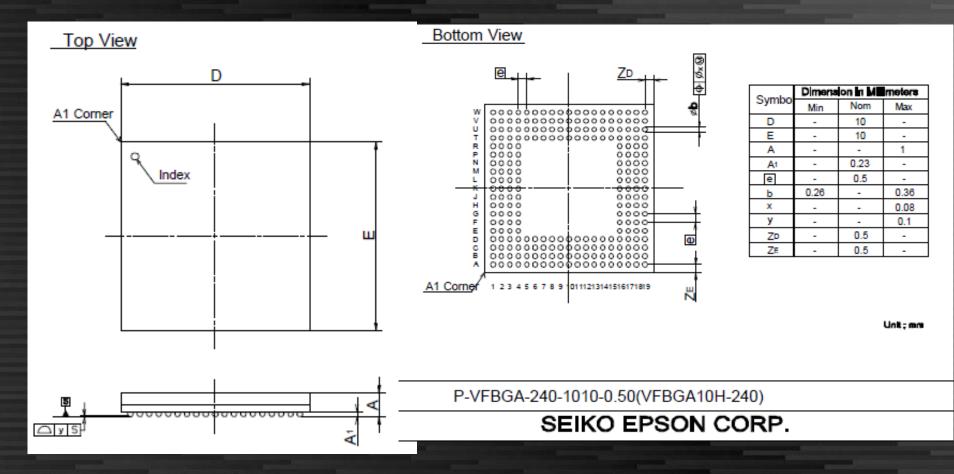

#### Thin BGA

1 mm thinkness, 240 pins (same as QFP SKIROC2) Sc people considering LCC(Leadless Chip Career) or CIB (Chip In Board)

Taikan Suehara, LLR-Kyushu meeting, 11 Apr. 2014 page 2

#### 試作デバイス仕様一覧表

2014年 4月 10日 セイコーエブソン(株) マイクロテハイス事業部

この帳票は、お客様の試作を間違い無く タイムリーに作成する為の帳票です。 趣旨をご理解の上、ご協力をお願い致します。

#### 試作内容

| 試作內容                |                                         |                           |                           |

|---------------------|-----------------------------------------|---------------------------|---------------------------|

| お客様 名               | 末原 大幹様                                  | 製品名                       |                           |

| パッケージ名称/構造          | VFBGA10H                                | Pin数<br>リード/ボールピッチ        | 240<br>0.5 mm             |

| 式作用途・目的             |                                         |                           |                           |

| デバイス支給形態            | <b>インチWF、 インチ チゥ</b> ፓጉレ                |                           | X 7.5 mm , Y 8.1 mm       |

| NFの場合、有効チゥプ<br>数    |                                         | チップ 材質<br>(チップサイス は       | Si、 Low-k、<br>その他材質       |

| ig<br>igりチップの処理方法   | 廃却、その他                                  | スクライブセンター基準)              | C WISH A                  |

| NF裏面研削              | 不要、要 μm⇒ μm                             | パッド材質<br>パッド部メタル原         |                           |

| スクライブライン幅           | μm                                      | パッド下構造                    |                           |

| パシベーション仕様           |                                         | ポリイミドコート                  | 無し、有り μ m<br>材質           |

| 最小パッドピッチ            | μm                                      | パッド開口部サイズ                 | μm                        |

| チップ図面               | 無し、有り<br>(ダイナンパー位置/表示内容 要)<br>(パッド座標 要) | WF電特不良識別                  | 無し、有り<br>インク、 レーザー、 マップ方式 |

| 結線図                 | 無し、有り                                   | ネットリスト/<br>Pin Assignment | 無し、有り                     |

| 部品のはんだ実装<br>(受動素子等) | 無し、有り                                   | はんだ実装部品の仕様                |                           |

| デバイス静電耐圧            | ٧                                       | マーク仕様                     |                           |

| 支給デバイス数             | WF 枚、デバイス 個                             | 希望完成数                     |                           |

| サンブル水準              | 無し、有り                                   | 希望納期                      |                           |

| 支給部品·部材             | 無し、有り<br>支給部品・部材仕様                      | 支給部品/<br>部材内訳             |                           |

| 御社での信頼性試験           | 無し、有り内容<br>評価日程                         |                           | 1                         |

| 環境対応                |                                         | 梱包仕様                      |                           |

| 電気特性テスト対応           | 不要、要ラストプログラム提供 無し、有り                    | 輸出法令該非判定                  | 該当、非該当<br>パラメージント 無し、有り   |

g, 11 Apr. 2014 page 3

### SKIROC test board

|         |              |   | /H . | 灵化水口 口 印识 | ++00,000 |

|---------|--------------|---|------|-----------|----------|

| 1       | 設計代(回路図作成無)  | 1 | 式    | 340,000   | ¥340,000 |

| 2       |              |   |      |           | ¥0       |

|         | 消費税抜合計額      |   |      |           | ¥340,000 |

| 1       | 設計代(回路図作成のみ) | 1 | 式    | 90,000    | ¥90,000  |

| 2       |              |   |      |           |          |

| 消費税抜合計額 |              |   |      | ¥90,000   |          |

|         |              |   |      | ·         |          |

1 EUR = 140 JPY

Design fee:

BGA with DIF connector

Schematic: 600 EUR

Layout: 2500 EUR

### SKIROC test board

| No      | 品 名 と 仕 様   | 数量 | 単位 | 単 価      | 金額       |

|---------|-------------|----|----|----------|----------|

| 1       | 8層基板        | 1  | 枚  | 21,000   | ¥21,000  |

| 2       | ネガ代         | 1  | 式  | 50,000   | ¥50,000  |

| 3       | グリーンマスク版代   | 1  | 式  | 38,000   | ¥38,000  |

| 4       | シルク印刷版代     | 1  | 式  | 38,000   | ¥38,000  |

| 5       | NCテープ代      | 1  | 式  | 15,000   | ¥15,000  |

| 6       | レーザー出力代     | 1  | 式  | 120,000  | ¥120,000 |

| 7       | 実装イニシャル     | 1  | 式  | 200,000  | ¥200,000 |

| 8       | 実装費         | 1  | 式  | 50,000   | ¥50,000  |

| 9       | 部品代         | 1  | 式  | 420,000  | ¥420,000 |

| 10      |             |    |    |          |          |

| 11      | ロット価格       |    |    |          |          |

| 12      | 8層基板 1-29枚  | 1  | 枚  | 21,000   |          |

| 13      | 8層基板 30-99枚 | 1  | 枚  |          |          |

| 14      |             |    |    |          |          |

| 15      |             |    |    |          |          |

| 消費税抜合計額 |             |    |    | ¥952,000 |          |

Initial cost: 3,500 EUR

Unit cost: 500 EUR + components (mainly socket)

#### Software

#### EUDAQ

- Not mature, may need modification on framework

- May have conflicts to ongoing projects?

- have LCIO output, no XML port

- GUI: small freedom (for run control/config)

#### xDAQ

- Mature but complicated (for me: maybe OK)

- Modification of framework difficult?

- no LCIO, have XML

Atmosphere in ILC prefer EUDAQ: maybe I can survive on it

## FSM in EUDAQ

- Configure

- Start

- Stop

No intelligent event control but may be possible to implement

# Shipment

How is it?

#### DIF FPGA

- We're thinking of contributing in FPGA part

- It's helpful to understand whole system

- It's also helpful for debugging system

- It's also helpful to combine DAQs

- Yuji may be able to go to LLR for it