## **Electronics for FCAL Detectors**

#### On behalf of the FCAL collaboration

Angel Abusleme

Pontificia Universidad Catolica de Chile

#### LCWS 2014 October 6-10, Belgrade, Serbia

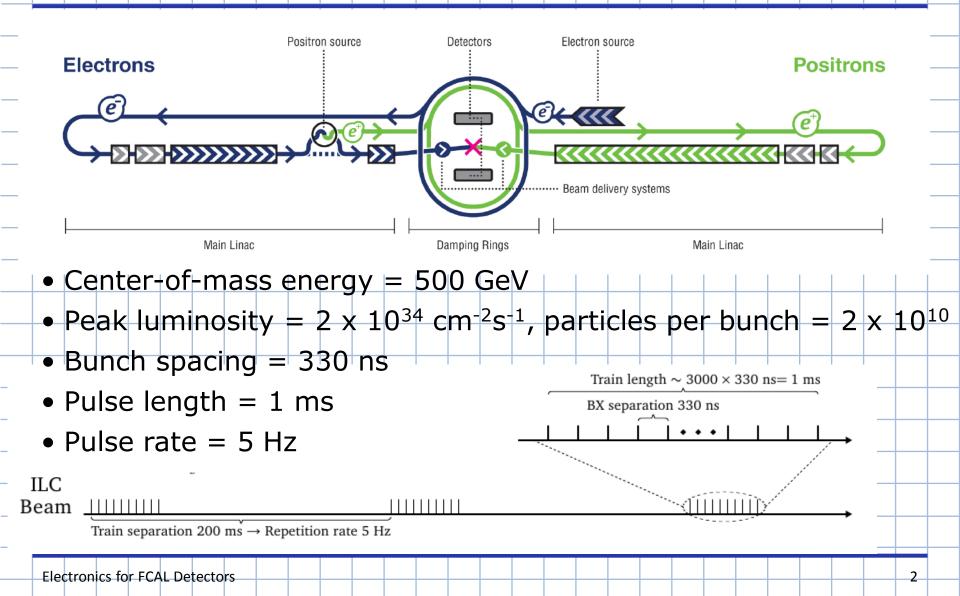

#### The ILC: Layout and beam structure

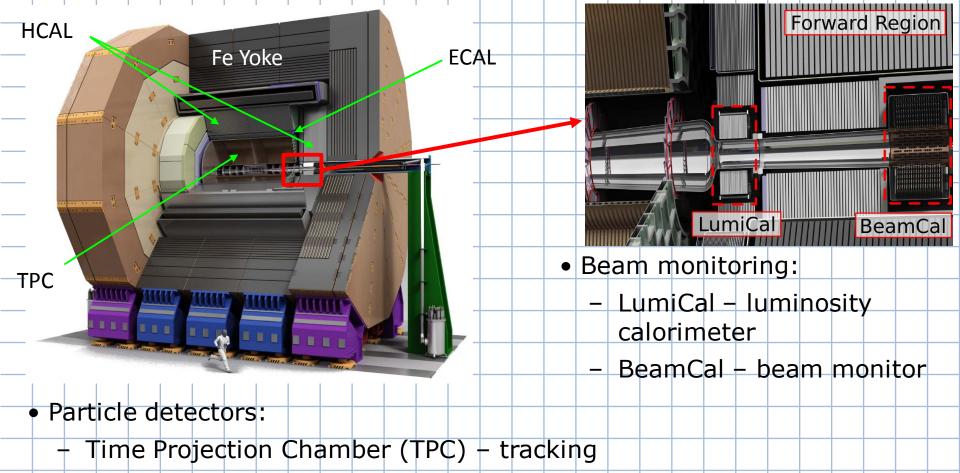

## **ILC** detector

- Electromagnetic/Hadronic Calorimetes (E/HCAL) calorimetry

- Fe Yoke muon system

## **Talk Outline**

#### Electronics for LumiCal

# AGH

DECHI

Collaboration

#### Electronics for BeamCal

## ELECTRONICS FOR LUMICAL

AGH

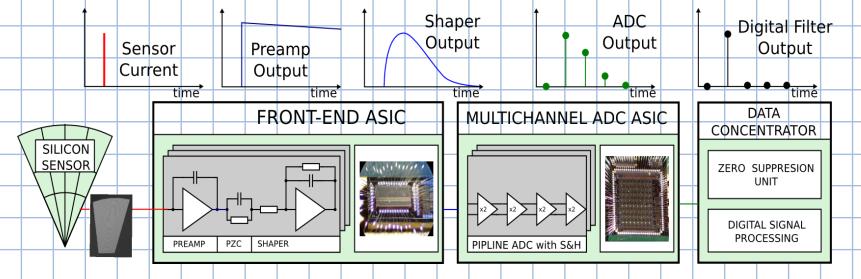

## LumiCal Readout Chain

#### •Existing LumiCal detector readout comprises:

- 8 channel front-end ASIC with preamp & CR-RC shaper Tpeak~60ns, ~9mW (AMIS 0.35um)

- 8 channel pipeline ADC ASIC, Tsmp<=25MS/s, ~1.2mW/MHz (AMS 0.35um)</li>

- FPGA based data concentrator and further readout

#### New developments for LumiCal detector readout:

- Prototype front-end ASIC in CMOS 130 nm under development... (presented at TWEPP2014)

- Prototype SAR ADC ASIC in CMOS 130 nm fabricated and working well, already presented at TWEPP2013

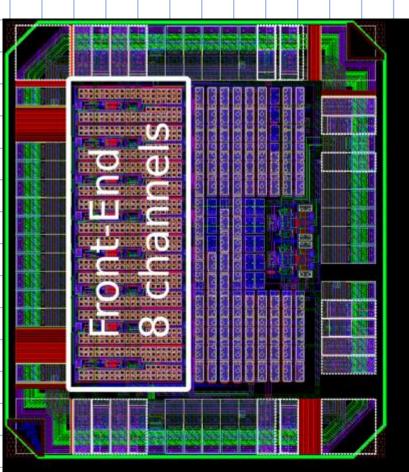

#### New 8-channel front-end in CMOS 130 nm

#### CMOS 130 nm technology

- 8 channels

- Detector capacitance Cdet ≈ 5 ÷ 50pF

- CR-RC shaping with peaking time Tpeak ≈ 50 ns

- Variable gain:

- calibration mode MIP sensitivity

- physics mode input charge up to ~6

pC

- Power pulsing

- Peak power consumption ~1.5 mW/channel

- Pitch ~140 um

- Noise: ENC ~ 1000e-@10pF

- Crosstalk < 1%

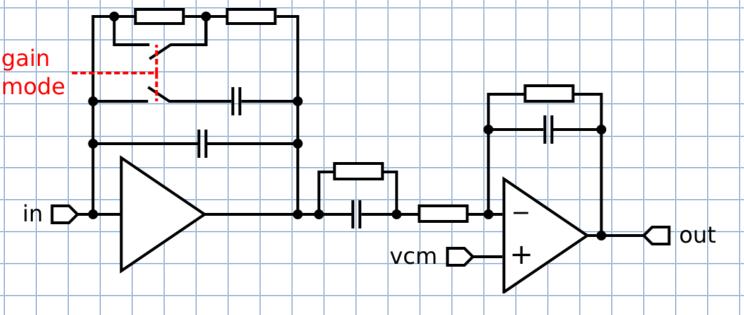

## **Analog front-end Architecture**

Preamplifier PZC+RealPole RealPole

- Two gain modes (calibration and physics) applied by switching R,C components in preamplifier feedback circuit

- Simple CR-RC pulse shaping chosen to simplify the deconvolution procedure in further Digital Signal Processing (DSP)

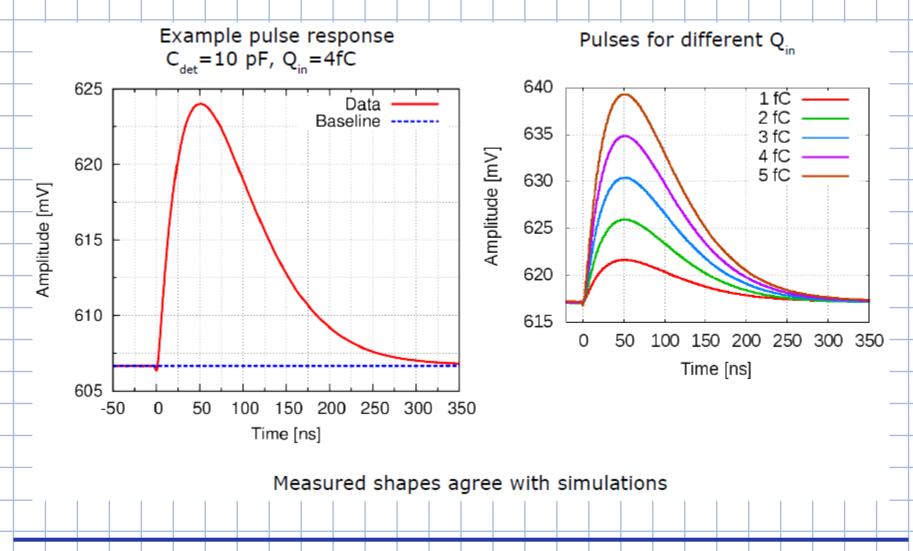

## Analog Front-End measurements Pulse response in high gain mode

#### Analog Front-End measurements:

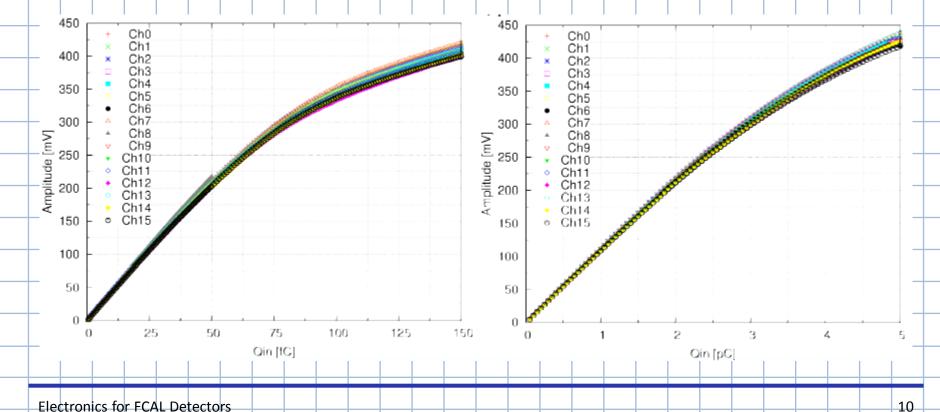

#### Linearity

- Measurements reasults with agreement with simulations

- High gain 4.2 mV/fC (4.6 mV/fC from simulations)

- varies between 4.03 to 4.37 mV/fC

- Low gain 105 mV/pC (113 mV/pC from simulations)

- varies between 101.7 to 106.4 mV/pC

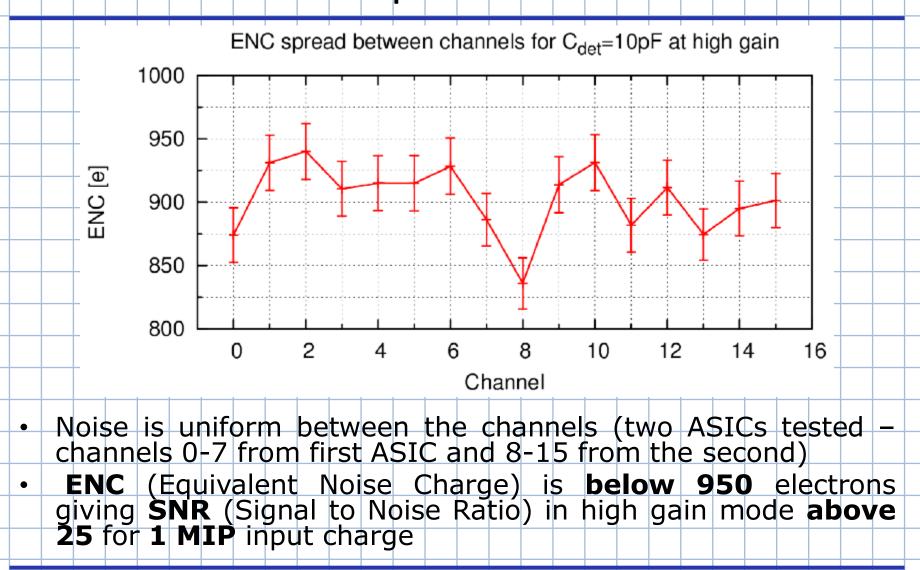

#### Analog Front-End measurements: Noise performance

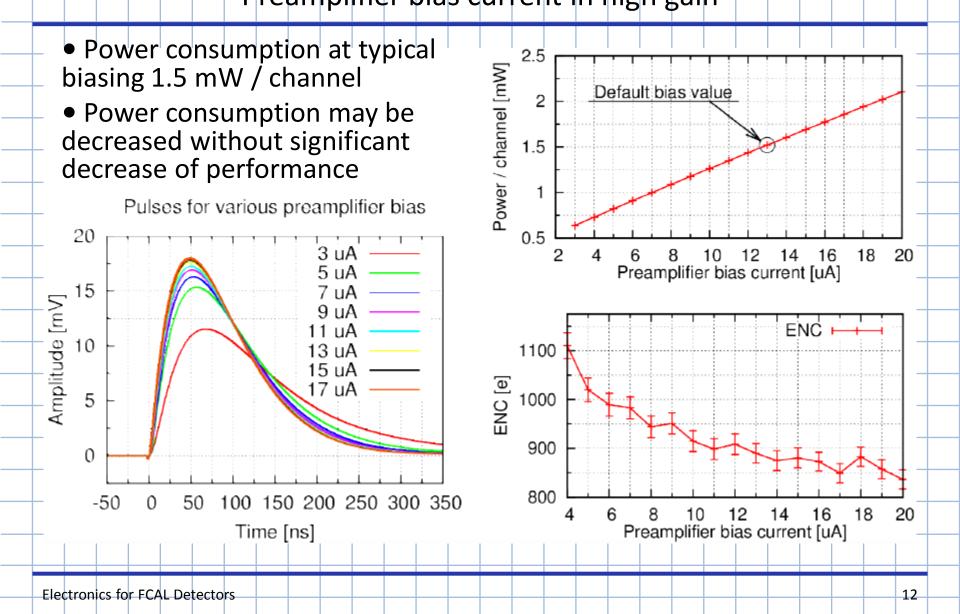

Analog Front-End measurements:

Power consumption vs performance, Preamplifier bias current in high gain

#### Analog Front-End measurements:

#### Summary

- Measurements results agree with simulations and specifications

- Pulse shape and peaking time (50ns) as excepted

- Gains in both modes differs within 10% from simulated

- Baseline spread below 25 mV

- Noise ENC at 10 pF below 1000 e-

- Crosstalk measurements:

- High gain 0.64%

- Low gain 0.80%

- Power consumption ~1.5 mW/channel can be reduced by lowering bias currents

- All parameters uniform between channels (two ASICs measured)

- Detector capacitance measurements needs to be finished...

### **ELECTRONICS FOR BEAMCAL**

Electronics for FCAL Detectors

LIF

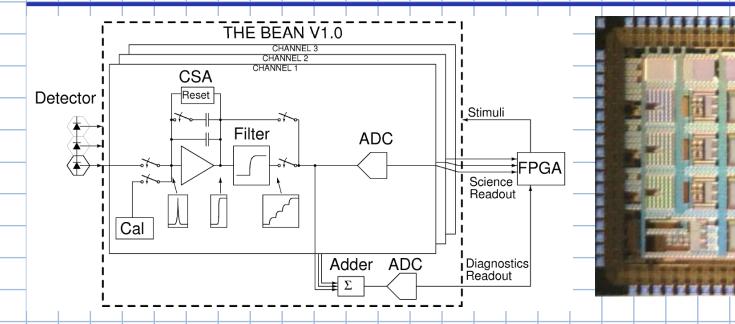

#### The Bean: 3-channel readout chain

## in 180nm (2010)

- 72 pads, 2.4mm x 2.4mm (including pads)

- 7306 nodes, 35789 circuit elements

- 360µm channel pitch (including power bus)

- 3 charge amplifiers, 4 x 10-bit, fully diff. SAR ADCs, 1 SC adder, 3 SC filters, etc.

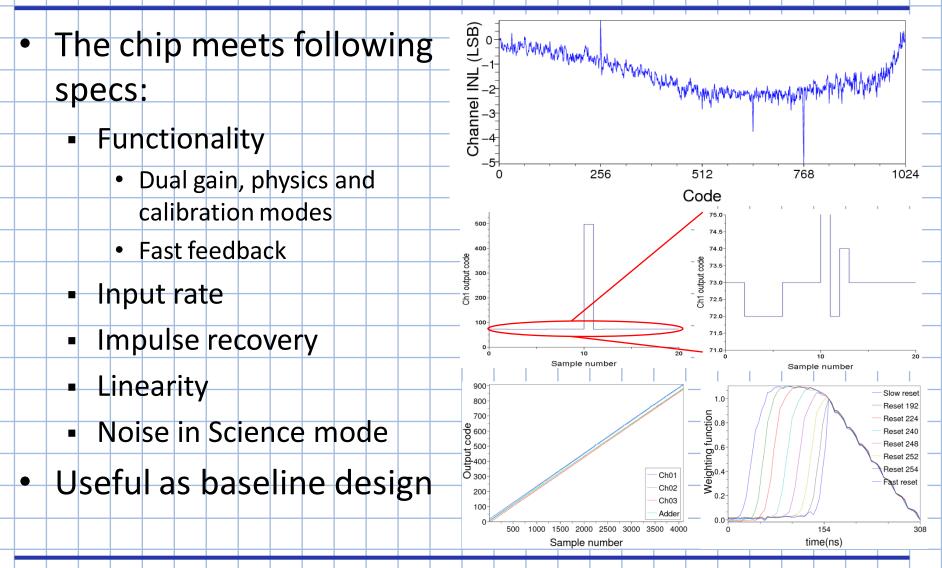

## The Bean results summary (2010)

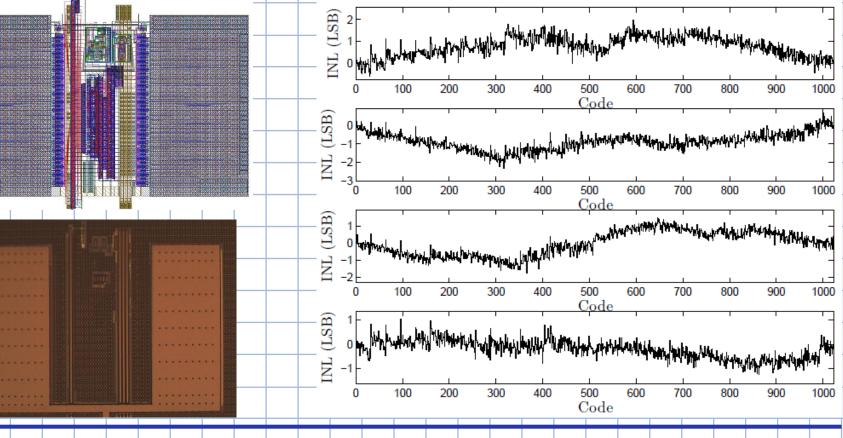

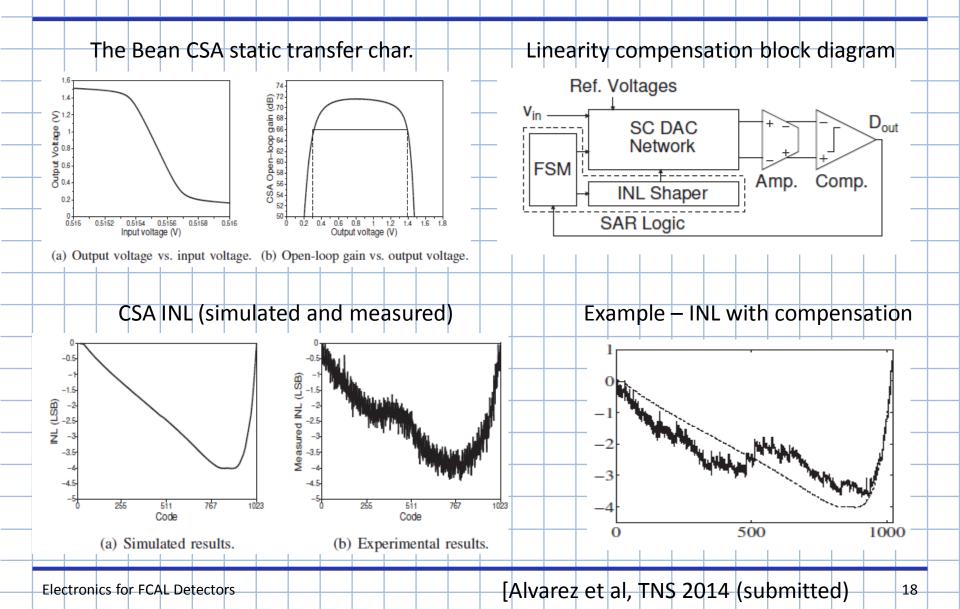

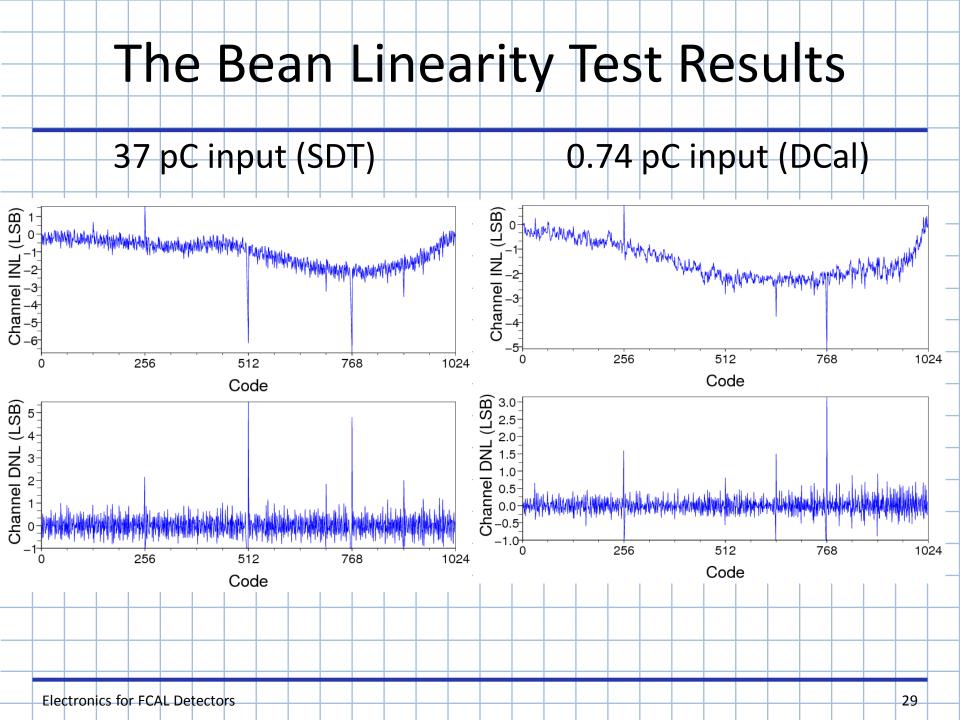

#### ADC linearity compensation (2012-2013)

ADC uses systematic process mismatch to correct nonlinearity

## Linearity compensation results

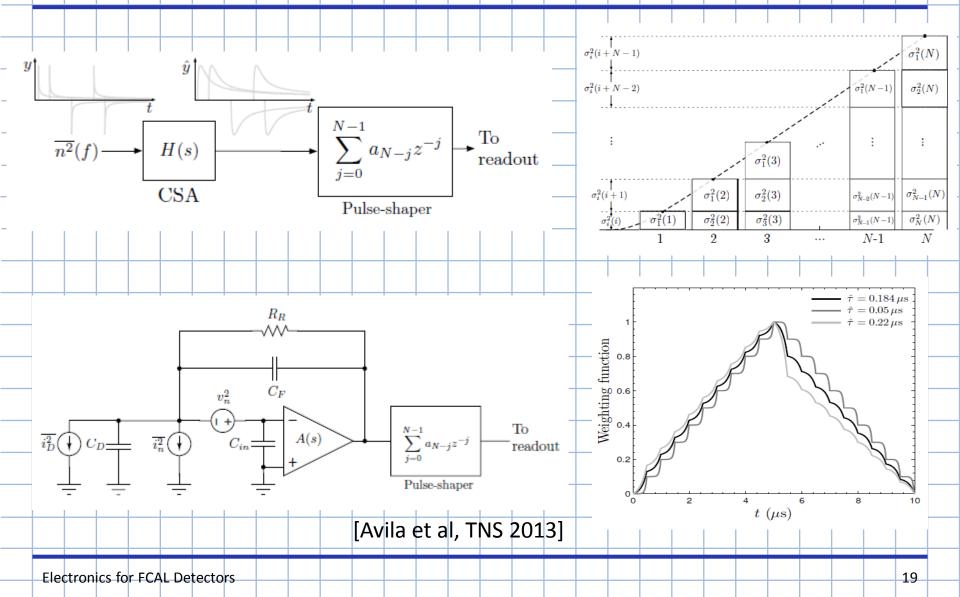

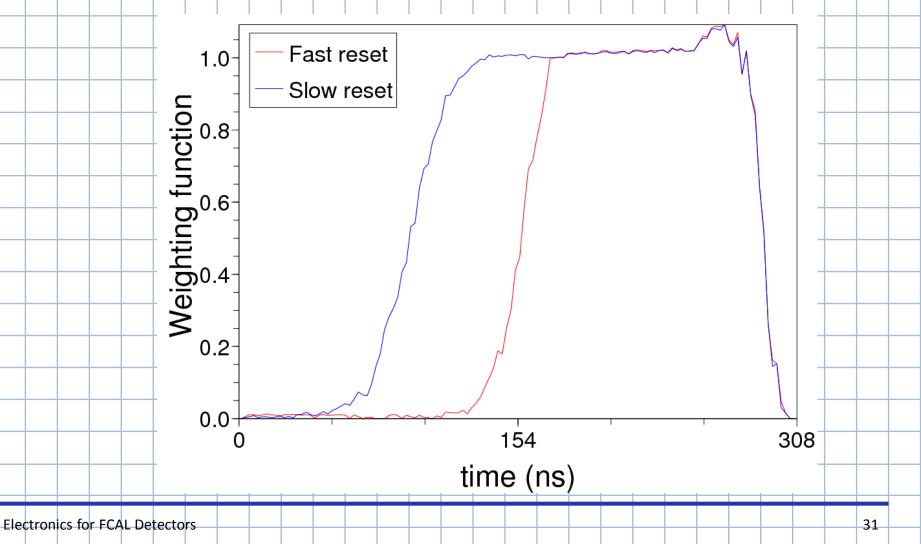

### **Arbitrary weighting function synthesis**

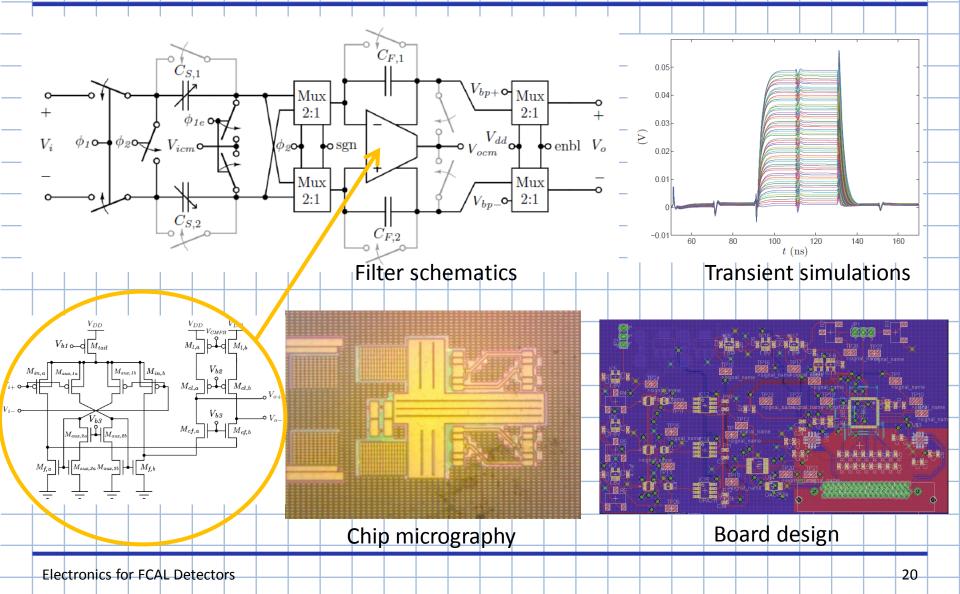

#### Chip design and fabrication (2013-2014)

## Intentionally-nonlinear ADC study

The energy resolution of a sampling calorimeter

$\delta E$

can be described as

- Required resolution of electronics is a function of the shower energy

- The bit size changes along the full scale range

- Idea: to adjust the ADC resolution according to input

- Otherwise, dynamic range specification is hard to meet

### Example: ADC Dynamic range spec

- In BeamCal, the LSB for 1GeV should be 0.2GeV

- Then, a linear ADC good for up to 1TeV needs 1000/0.2=5000 codes, or 13 bits

- However, if the ADC resolution matches the

- fundamental resolution of a sampling calorimeter,

- only 8 bits are required to represent all the

information space!

- This does not relax the front-end dynamic range

- We still want to have a linear CSA

- This is also required for fast feedback estimations

#### Linear vs. nonlinear ADC design Linear ADC Do 32C Do 64C 16C 2CB+1lines 10 ο 10 ο $V_{In \circ - \circ}$ V<sub>Ref</sub> o-o Nonlinear ADC Do C<sub>N-1</sub> $C_1$ Do C<sub>N-2</sub> $C_N$ 2<sup>B</sup> lines $V_{In \ \bullet \! \bullet \! \bullet}$ Decoder V<sub>Ref</sub> o-o

23

## To nonlinearize... or not?

#### SIZE COMPARISON BETWEEN DIFFERENT FULLY-THERMOMETER-CODED SAR ADCS.

|                                    | Capacitor Array $(C_{tot})$                        | Decoder               | Digital Core              | Comparator        | Amplifier         |

|------------------------------------|----------------------------------------------------|-----------------------|---------------------------|-------------------|-------------------|

| Standard<br>Linear                 | $c_u \cdot 2^B$                                    | $\propto 2^B L_{min}$ | $\propto B \cdot L_{min}$ | $\propto L_{min}$ | $\propto L_{min}$ |

| <br><i>s</i> -section<br>Piecewise | $c_u \cdot 2^B \sum_{i=1}^s \alpha_i 2^{\Delta_i}$ | $\propto 2^B L_{min}$ | $\propto B \cdot L_{min}$ | $\propto L_{min}$ | $\propto L_{min}$ |

| Fully<br>Nonlinear                 | $c_u \cdot \sum_{i=1}^{N_{nl}} k_i$                | $\propto 2^B L_{min}$ | $\propto B \cdot L_{min}$ | $\propto L_{min}$ | $\propto L_{min}$ |

- Tradeoff between capacitor array size and decoder size

- But 8 bits instead of 13 bits of resolution!

- Still working on this...

## **Electronics for FCAL: Summary**

#### AGH and PUC are designing electronics for FCAL

- AGH: LumiCal, current design also works for BeamCal

- PUC: BeamCal, now converging through non-standard design ideas

#### LumiCal

- Readout IC in AMS0.35 which we still want to use for multiplane tests

- 8-channel front-end in CMOS 130 nm, good for test-beam purpose and FCAL studies

- Successfully designed and tested a 10-bit SAR ADC in CMOS 130nm

- New 8 channel 10-bit SAR ADC in CMOS 130nm waiting for tests (next 2 months)

#### BeamCal

- 3-channel Readout chain in 180nm (2010), tested

- ADC linearity compensation (2012 2013)

- Arbitrary weighting function synthesis (2013 2014)

- Intentionally nonlinear ADC (ongoing work)

## **Electronics for FCAL: Future plans**

- AGH, 2015: Design and submit complete multichannel ASIC for LumiCal (or two ASICs: FE+ADC) with front-end and ADC in each channel plus various DACs, serializers etc.

- PUC, 2015: Design and test a multichannel FE and ADC

IC for BeamCal

- Synchronous and asynchronous readout

- Joint collaboration:

- Eventually converge to the same technology and process

- Share IP/fabrication runs

- Student/researcher visits

#### **BACKUP MATERIAL**

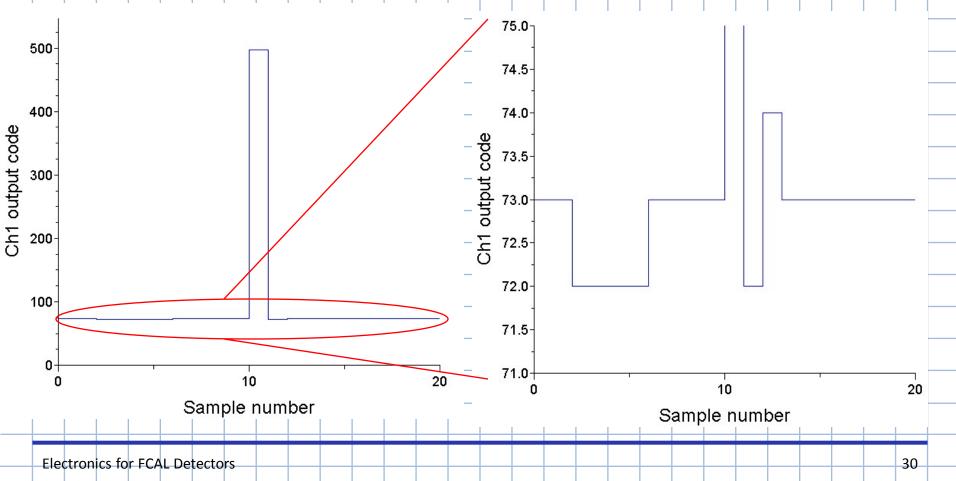

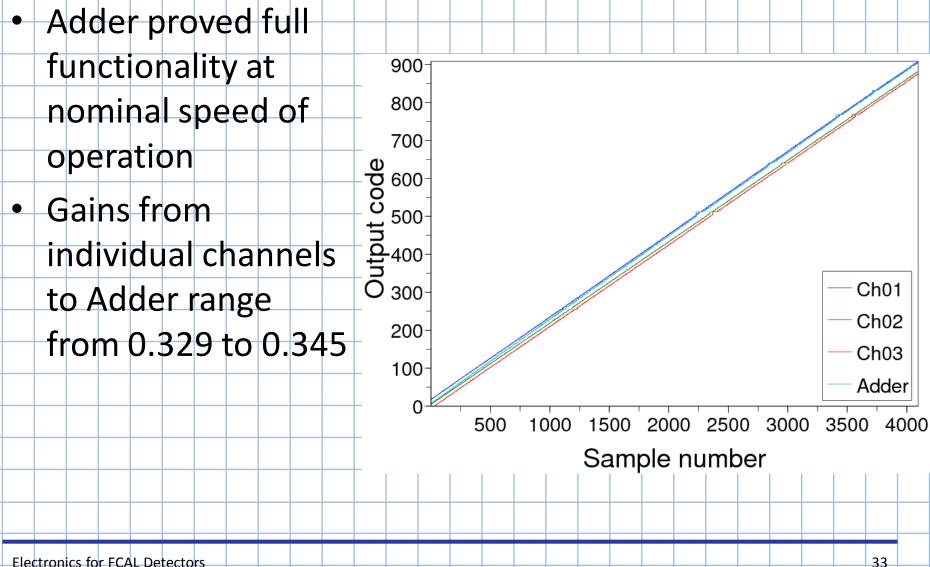

## The Bean Bandwidth test results

- Input injected on 10<sup>th</sup> cycle only

- Digital output recorded, nominal speed

#### The Bean

Weighting function measurement, SDT

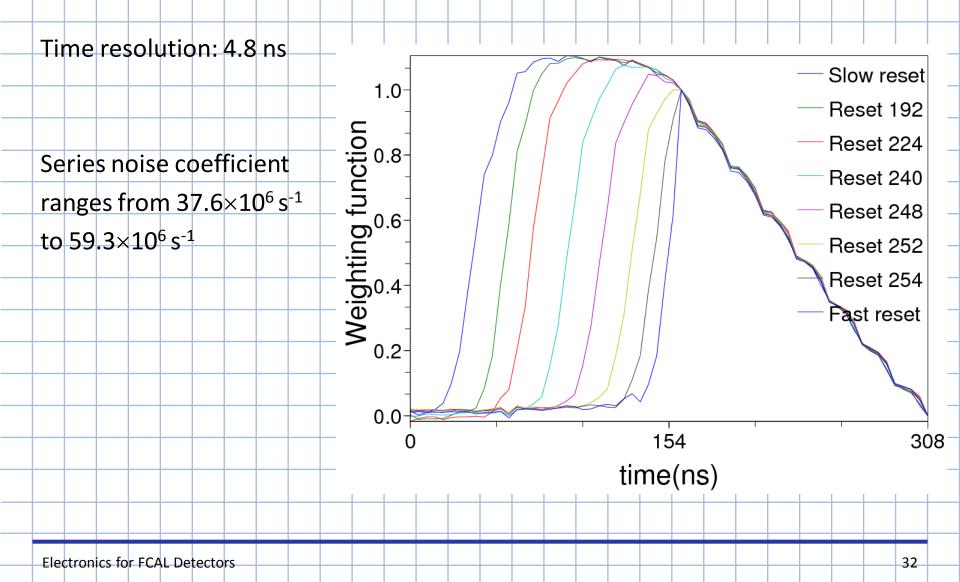

#### Time resolution: 4.8 ns

#### The Bean

#### Weighting function measurement, DCal

#### The Bean

#### Fast feedback adder measurement

## LumiCal Analog Front-End measurements:

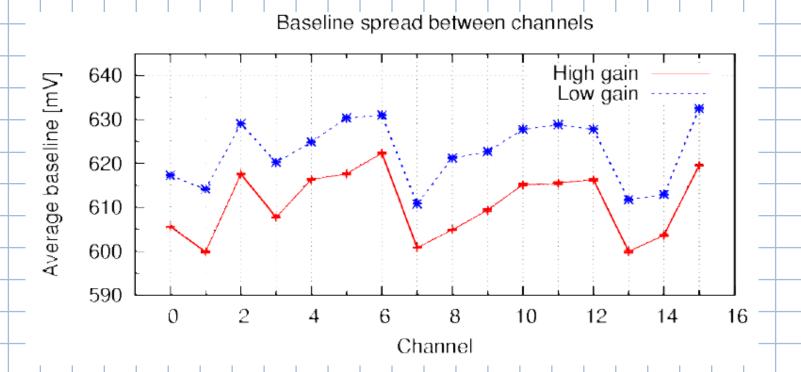

#### **Baseline spread**

- Baseline spread is below 25 mV for both gains in agreement with shaper opamp offset simulations

- Baseline spread in high gain 600 mV to 622 mV

- Baseline spread in low gain 610 mV to 633 mV

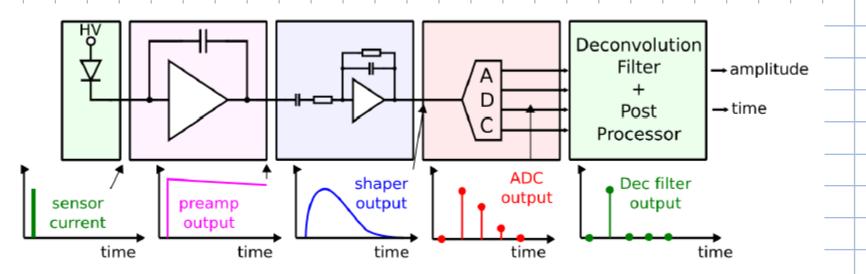

#### LumiCal readout electronics diagram -

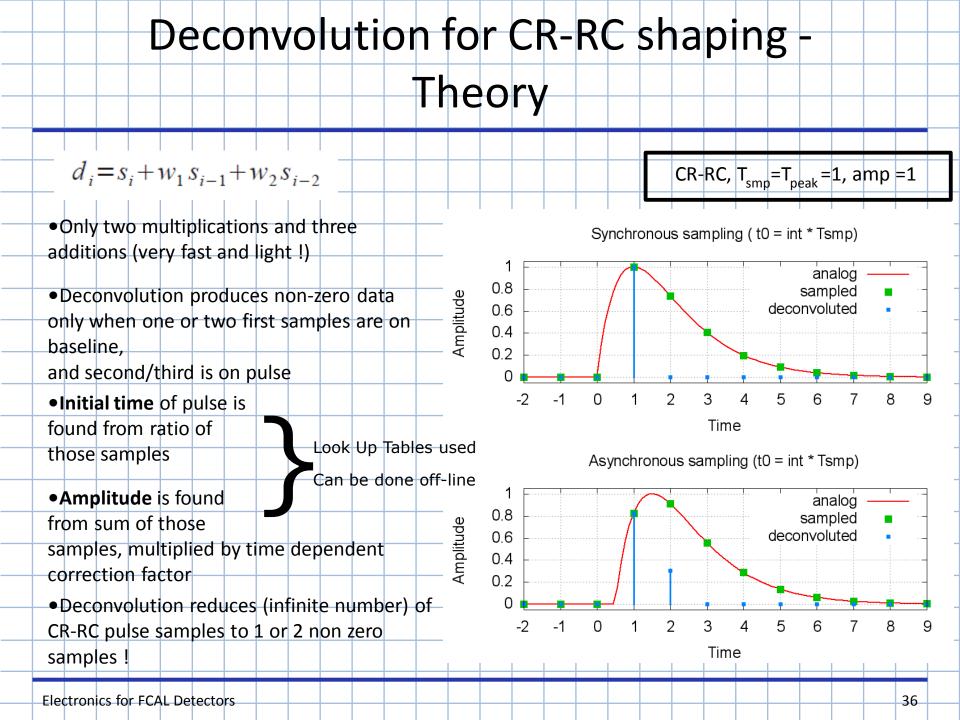

**Deconvolution theory**

Pulse at output of shaper v(t) is convolution of input signal (current from sensor – s(t)) and impulse response of readout chain h(t):

$$v(t) = \int_{-\infty}^{+\infty} h(t-x) s(x) dx$$

Using data from continuously running ADC and taking advantage of known pulse shape one can perform invert procedure – deconvolution – to get information about event time and amplitude

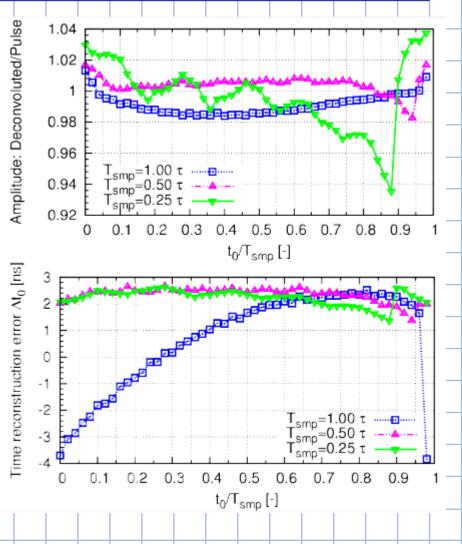

### Deconvolution for CR-RC shaping Real, averaged, FE pulses

- Real pulse (1 MIP) deconvoluted for various phase shift to between the Front-End pulse and ADC sampling

- Deconvolution done for different sampling periods (12.5, 25 and 50 ns are presented)

- Amplitude reconstruction (top plot) deconvoluted to real pulse amplitude ratio

- Error is below 2% except 12.5 ns sampling period

- Time reconstruction (bottom plot) difference between reconstructed and real pulse peak position

- Constant offset of around 2 ns except

50 ns sampling period

• S/N after deconvolution still to be measured...