#### FTD-ILD sub-detector power distribution system prototype based on Supercapacitors

I.Echevarria, M. Iglesias, A. Pradas, FJ. Piedrafita,

Dr. F. Arteche,

6-10 October 2014

- 1. Introduction

- 2.Supercapacitors

- Supercapacitors based power distribution.

- 4. FTD-ILD power group prototype —Power dissipation test results

- 5.Conclusions

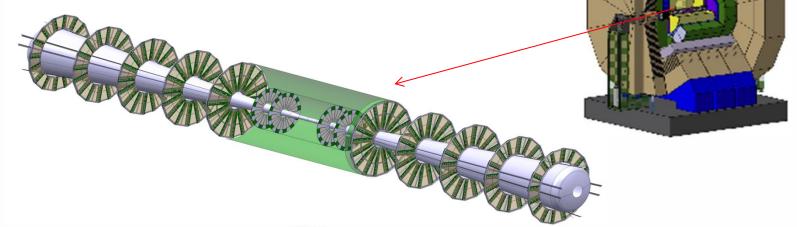

- The mstrip-FTD-ILD system is a silicon strip tracker located in the innermost part of the tracker region of the ILD.

- It consists of 10 disks.

- Each disk has 16 petals

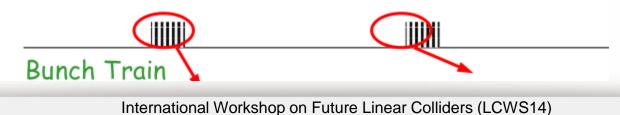

- The FTD electronics will operate synchronously (or coordinated) with ILC accelerator....

- 1 ms bunch train every 200ms (Duty cycle of 0.5%)

Belgrade, Serbia, October 2014

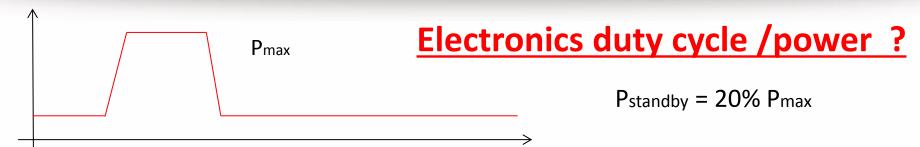

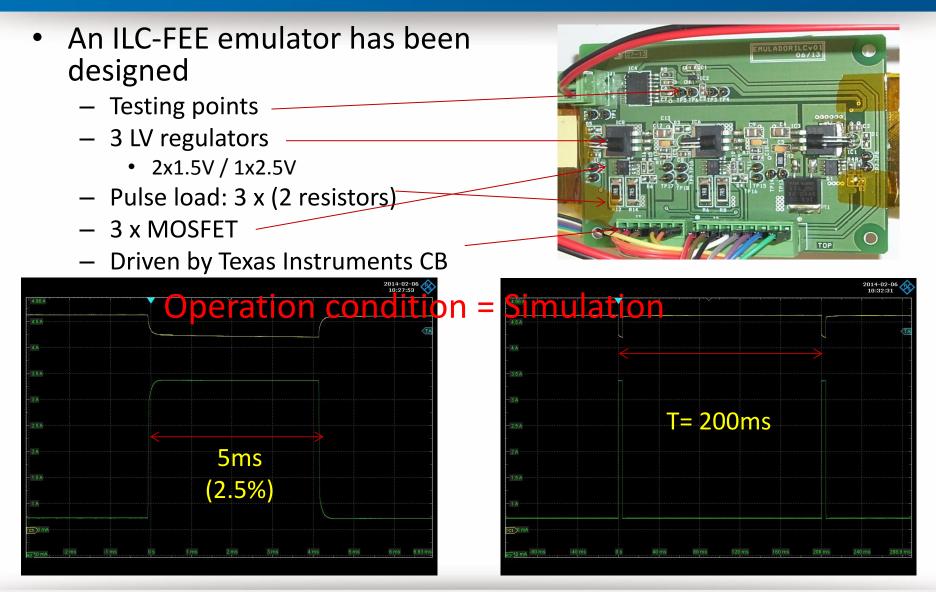

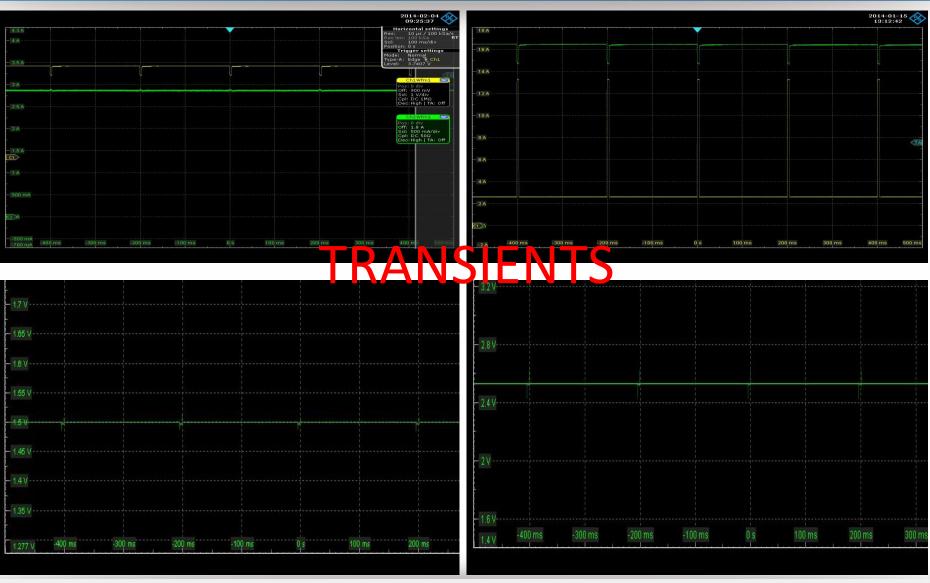

- Several conservative considerations have been assumed in the electronics operation:

- Electronics duty cycle operation (2.5% 5ms / 200ms).

- 1 ms power up / down

- 3 ms operation state to stabilize power and operate.

- It minimizes transients

- Power consumption during the standby (20% Pmax). !!!

- It is a critical parameter (100W / 20W): 22 W/cycle

- 2.5W/cycle FEE ON (11%)

- 19.5W/cycle STAND BY (89 %)

- If standby power 10W : Ptotal = 12.25 W/cycle

- If FEE operation time 2.5ms: : Ptotal=21W/cycle

- The total Strip-FTD current / power demanded is:

- Bunch crossing state 458 A (≈ 860 W)

- Stand-by state 91.6A (≈ 171W)

- System Granularity: 1/4 Petal

- Based on reliability and system design issues

|                                           | MIDDLE PITCH |           |           |           |                         |             |            |             |           |            |  |

|-------------------------------------------|--------------|-----------|-----------|-----------|-------------------------|-------------|------------|-------------|-----------|------------|--|

| FTD                                       | FTD3         |           | FTD4      |           | FTD5                    |             | FTD6       |             | FTD7      |            |  |

|                                           | INN          | OUT       | INN       | OUT       | INN                     | OUT         | INN        | OUT         | INN       | OUT        |  |

| Nº Readout                                | 33920        | 61504     | 41600     | 64224     | 45472                   | 65504       | 51232      | 67424       | 63        | 424        |  |

| Chips per petal<br>(256 ch)               | 24           |           | 26        |           | 28                      |             | 29         |             | 16        |            |  |

| Optical links per<br>petal                | 1/2          |           | 1/2       |           | 1/2                     |             | 1/2        |             | 1/2       |            |  |

| I1.5 (A) per Petal                        | 1.75/0.35    |           | 1.9/0.38  |           | 2.05/0.41               |             | 2.12/ 0.42 |             | 1.16/0.23 |            |  |

| 12.5 (A) per Petal                        | 1.05/0.21    |           | 1.13/0.23 |           | 1.22/0.24               |             | 1.27/0.25  |             | 0.7/0.14  |            |  |

| l per petal                               | 2.79         | 2.79/0.56 |           | 3.03/0.61 |                         | 3.26/0.65   |            | 3.39/0.68   |           | 1.86/0.37  |  |

| I per disk                                | 44.6         | 44.6/8.9  |           | 48.5/9.71 |                         | 52.08/10.42 |            | 54.19/10.84 |           | 29.76/5.95 |  |

| TOTAL Mstrip- FTD Current<br>(both sides) |              |           | 458 A /   | 91.6 A    | ( CMS upgrade TK elec.) |             |            |             |           |            |  |

G3

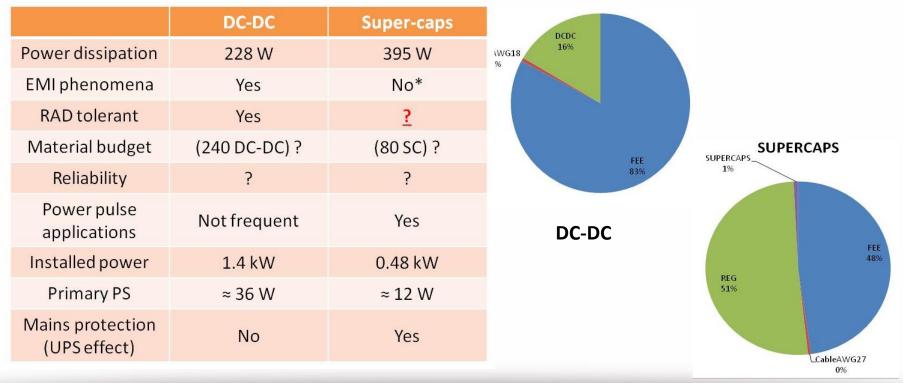

- There are several topologies that may be used for FTD.

- DC-DC-based power distribution

- Super-capacitor based power distribution

- Each of them has advantages and disadvantages.

- A detailed study was presented in LCWS 2012 Arlington (Texas)

# 2. Supercapacitors

- The most important element in SC-LV regulation option is the super-capacitor.

- It is new for HEP but not for industrial applications

- Super-capacitors are electrochemical capacitors with very high capacitance

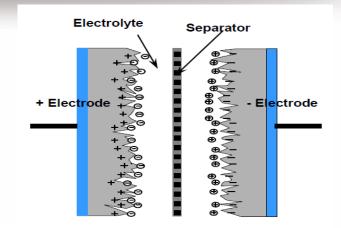

- The most common super-capacitor is the double layer capacitor.

- Double layer capacitor structure

- Electrodes: Activated Carbon

- Separator: Cellulose

- Electrolyte: Quaternary salt & acetonitrile.

- Other: Aluminum

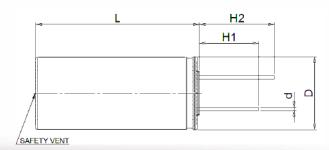

- Very light few g / size 1-3 cm

| Size  | Rated<br>Voltage | Rated<br>Capacitance | MAX<br>ESR(mΩ) | Dimension(mm) |    |   |   | Volume<br>(ml) | Weight<br>(g) |

|-------|------------------|----------------------|----------------|---------------|----|---|---|----------------|---------------|

|       | (V,DC)           | (F)                  | DC             | D             | L  | w | т | (111)          | (9)           |

| Small | 2.7              | 3                    | 55             | 8             | 20 |   |   | 1.0            | 1.5           |

|       | 2.7              | 5                    | 35             | 10            | 20 |   |   | 1.6            | 2.3           |

|       | 2.7              | 6                    | 33             | 8             | 30 |   |   | 1.5            | 2.3           |

|       | 2.7              | 10                   | 30             | 10            | 30 |   |   | 2.4            | 3.2           |

|       | 2.7              | 25                   | 25             | 16            | 25 |   |   | 5.0            | 6.5           |

|       | 2.7              | 50                   | 16             | 18            | 42 |   |   | 10.2           | 11.3          |

# 2. Supercapacitors

- There are four elements that have to be analyzed in detail for HEP applications

- Material Budget.

- It seems OK but a detailed evaluation is required

- Magnetic field issues

- Cycling issues

- Radiation issues

- Cycling issues (Reliability).

- Super-capacitor should be able to operate more that 10 million of cycles per year (DC-DC too)

- After 1e6 of full duty cycles a SC may decrease the 20% of capacitance

- <u>Radiation issues</u>

- Type of radiation: gammas & electrons

- Total dose: 1 or 2 Mrad

### 2. Supercapacitors

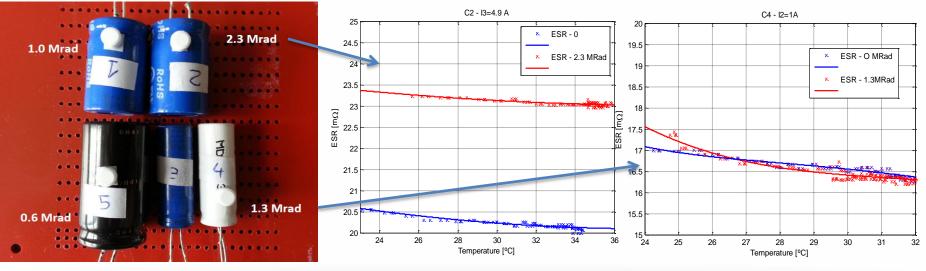

- A radiation test has been carried out in order to start the super-capacitor validation for FTD-ILD (<u>ECFA 2013</u>)

- Electrons at 20 MEV (ELBA facility University of Bonn)

- 5 super-capacitors have been tested ESR(T) & C(T)

- Different rates 3 x 10 F & 2 x 25 F

- Different companies (Maxwell, Nesscap & Panassonic)

- First results are very promising but it is still necessary a long validation process

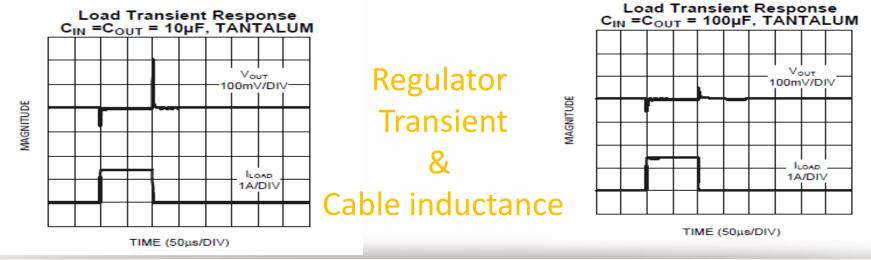

# 3. Supercapacitor based PS ITAINNOVA

- The main elements of this <u>topology</u> are:

- -Supercapacitors:

- Pulse power Transients locally

- -LV regulators:

- Stabilize FEE voltage

- -Current source :

- Controls super-capacitor voltage

### 3. Supercapacitor based PS ITAINNOVA

Belgrade, Serbia, October 2014

# 3. Supercapacitor based PS ITAINNOVA

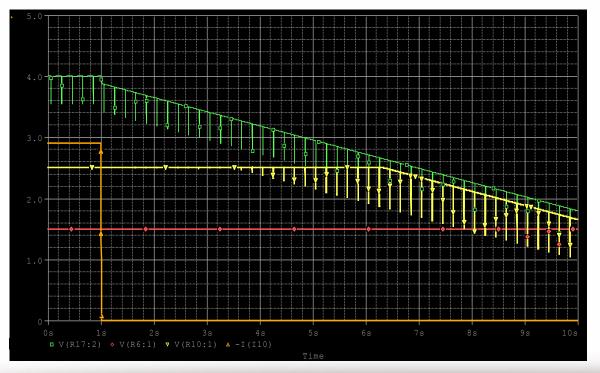

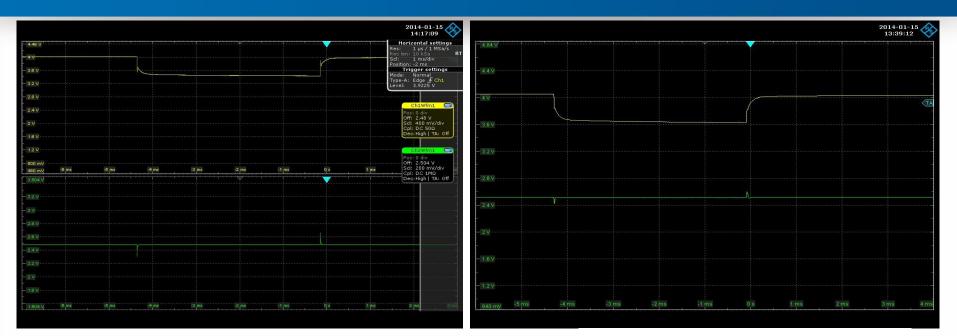

- The high capacitance has two advantages:

- It will protects the system in case mains failure Similar to UPS

- It helps shutdown the system in a controlled way.

- The dynamic response of primary power unit may be very slow

- Remote regulation of the supercap voltage will be easy

- The duration of the shut-down capability will depends on :

- Capacitance

- Voltage

#### **4. FTD-ILD power group prototype** ITAINNOVA **□**<sup>□</sup>

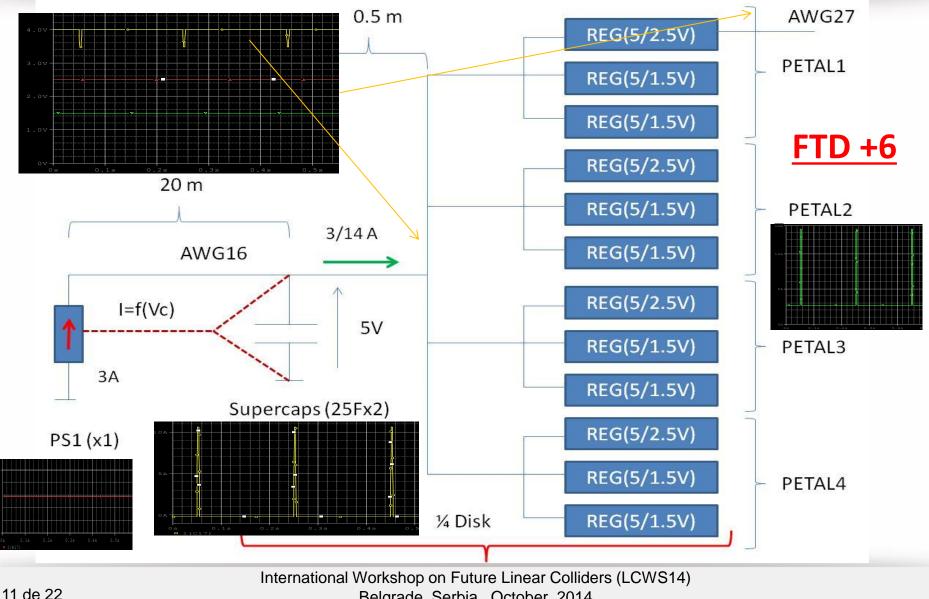

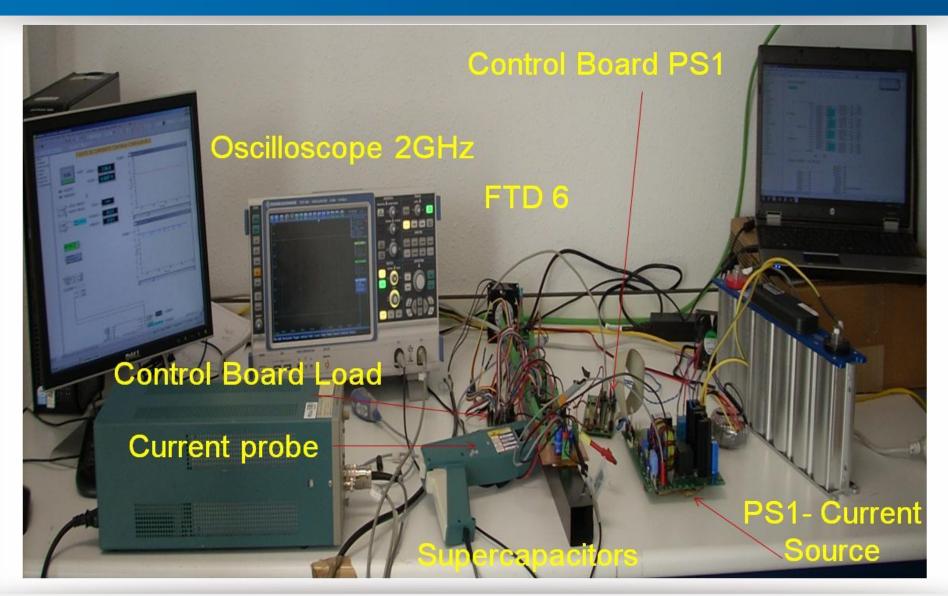

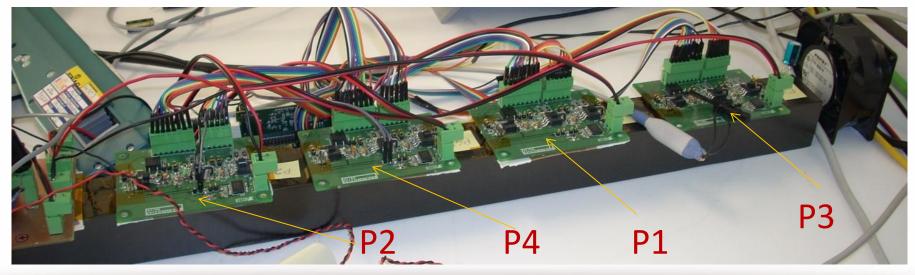

- A real prototype of 1 Group of FTD sub-detector (FTD +6) has been developed

- 4 load boards It simulates the FEE (hybrid) per petal

- 2 Super-capacitors (several distance to Dummy loads 50cm /10cm)

- 1CF structure It has been developed by FERMILAB-CMS Tracker II

- Ip=13.5A Isb =2.7A (Per petal Ip=3.4A / Isb=0.7A)

- Vsc = 4.2 V / Vinp=4V

International Workshop on Future Linear Colliders (LCWS14) Belgrade, Serbia, October 2014

16 de 22

### **4. FTD-ILD power group prototype** ITAINNOVA □<sup>□</sup>

#### <u>Major Fault – UPS capability</u>

#### **4.1 FTD-ILD power group prototype:**

#### **Power dissipation test**

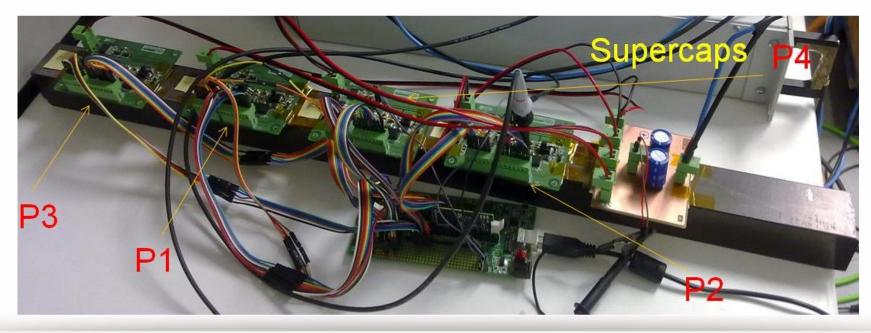

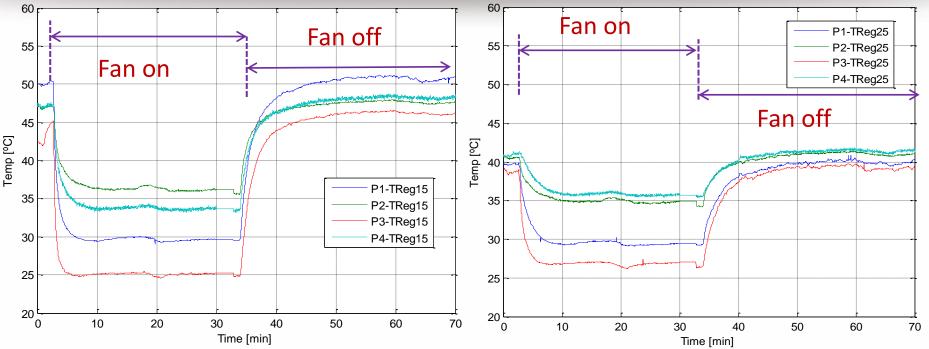

- A very simple temperature test has been performed

- Temperature sensors were installed on each board:

- One Termistor (PTC) per LV regulator

- Temperature is processed by the control board

- A fan has been installed on one side of the CF structure

- It has been switched on /off

- Systems were running more than 3 hours

- Baseline Temperature : 21ºC

#### **4.1 FTD-ILD power group prototype:**

#### **Power dissipation test**

- LVReg (1.5V) dissipates more power than LV (2.5V)

- From the point of view of electronics, "this prototype" does not need to be cooled (resistances dissipate power too)

- Not Cooled: Tmax(P1)≈51°C (ΔT ≈ 30°C) / Tmin(P3)≈ 46°C (ΔT ≈ 25°C)

- Cooled: Tmax(P2)≈34<sup>o</sup>C (ΔT ≈ 13<sup>o</sup>C) / Tmin(P3)≈ 25<sup>o</sup>C (ΔT ≈ 4<sup>o</sup>C)

- Pulsing effect is very small from the point of view temperature

# **5.** Conclusions

- A general overview of the supercapacitor based power supply distribution system for FTD-ILD has been presented

- Main characteristics and key elements have been shown

- Operation condition (regulation, pulsing, supercapacitors..)

- Supercapacitors fit quite well power pulsing requirements

- Radiation hardness shows no stoppers

- It still requires a detail analysis

- A real prototype of 1 group has been developed and tested

- Very good agreement with simulations

- Power dissipation aspects :

- From electronics point of view, this system does not need to be cooled

- The pulsing effect seems not to have a big impact

- The results are very promising but a long study of the system is required in order to define final specification