# Report from CALICE DAQ Task Force

Taikan Suehara (Kyushu University, Japan)

#### **CALICE DAQ Task Force**

- Experts' meeting discussing common DAQ

- Members

- Silicon: R. Cornat, F. Magniette, T. Suehara

- Scintillator: J. Kvasnicka, M. Reinecke

- Semi-digital HCAL: L. Mirabito, C. Combaret

- 2 years of mandate

- ~ 1 meeting per month

- 4 meetings held

# **Targets**

- Common DAQ

- Common clock and acquisition cycle (AC)

- Synchronized data taking and event matching

- Common run control

- Interface to upper control (TLU?)

- Combined testbeam

- Minimize total work by sharing tasks

# Past meetings

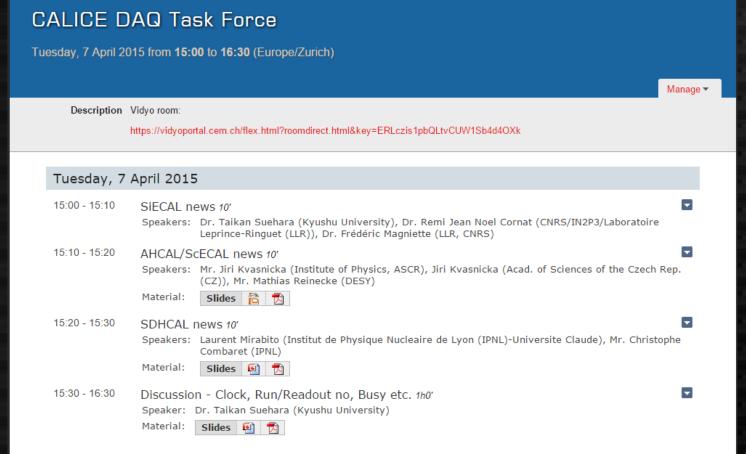

- 1. 10 Dec 2014

- Task overview

- Select coordinator

- 2. 19 Jan 2015

- Overview each subsystem

- 3. 4 Mar 2015

- Discussion on clock

- 4. 10 Apr 2015 (wo/ Si experts)

- Discussion on BX, Acq#, Run, Timestamp etc.

#### Indico

#### https://agenda.linearcollider.org/category/156/

#### **Public**

#### Master clock

- 'Master CCC' will provide clocks to each CCC

- 5 MHz is the basic clock corresponding to BX (or go into the real ILC BX period??)

- Need 50 MHz for Silicon because no PLL in Si-CCC (maybe done in master CCC)

- Scintillator and SDHCAL can produce their clock from the master clock

- Clock will be communicated via either HDMI or LEMO

# Synchronization (Tentative)

- BX synchronization

- Each detector has different inactive time after the start\_acq

- Master CCC sends start\_acq

(via either fast command or LEMO)

with configurable delay (set by PC)

to each port to synchronize livetime of each

- Busy

- Treated by Master CCC to determine stop\_acq and next start\_acq

- Should be sent from each subsystem

# Synchronization (2) (Tentative)

- Acquisition cycle (or readout cycle)

- Use AC counter from each subsystem to check the synchronization

- Start from 0 at each run

- Cross-check of 'Spill' sync by time-stamping (at lowest possible level of each subsystem)

- Run

- Common run number notation:

XXXYYYYY, XXX is the common TB number

- No limit for the run length typical run period should be O(1h) - O(1d)

### Who provides 'Master-CCC'?

- Scintillator

- Zedboard with Xilinx Zync (FPGA + ARM CPU)

(commercial, ~300 EUR/board)

- + Mezzanine (can be provided by DESY/Mainz)

- Firmware is in active development (DESY / Mainz? / possibly Kyushu?)

- SDHCAL

- No manpower

- Silicon

- **-?**

#### Software

No discussion yet

- EUDAQ

- LCIO

- etc.

Current priority to specify baseline design of hardware of common DAQ

# A few word about recent Kyushu activity

#### SKIROC2 BGA testboard

### SKIROC2 BGA testboard

- Delivered at March

- Two boards on 1<sup>st</sup> batch one is in modification

- Based on OMEGA TB

- QFP → BGA

- Two kind of sockets Ironwood & SER (jp)

- Connector for sensor

- Two interface

- Readout by OMEGA FPGA (worked last Friday!)

- Readout by Silicon DIF (not tested yet)

# DAQ activity plans in Kyushu

- Testbeam analysis (H. Hirai's talk)

- Investigate various characteristics of BGA SKIROC with the testboard

- FEB11 production (in plan)

- Combined DAQ

- Online monitor

- Automatic test of sensor/electronics

- Laser, RI (for crosstalk, gain etc.)

•