# **EUDET Beam Telescope**

**Wojciech Dulinski on behalf of JRA1**

#### Outline

- The goal: a high-precision, general purpose beam telescope

- Some limitations of solution based on existing techniques

- The beam telescope based on MAPS: novel, high precision tracking detectors

- Review of results from existing MAPS prototypes

- Telescope implementation plans and schedule

- Conclusions

# General Purpose Beam Telescope: a precision tool for testing a new generation of detectors being developed for International Linear Collider (ILC)

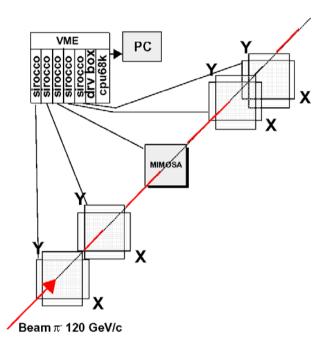

### **Existing solution: Strasbourg silicon-based beam telescope**

The beam telescope, based on high precision silicon strip detectors. The track position in the middle of the telescope is predicted with the precision of <u>~1 µm</u>

## One specific problem of proposed beam lines for ILC instrumentation testing: relatively low energy (few GeV) electrons (like at DESY)

Performance of standard (silicon strip based) beam telescope highly degraded (down to ~10µm in the center), because of multiple Coulomb scattering

- Our solution to overcome above problem: a use of a novel, high-precision, thin and pixellized tracking sensors, required by ILC and developed since several years in some laboratories

**Today, CMOS Monolithic Active Sensors** (MAPS) are mature and well adapted for this task!

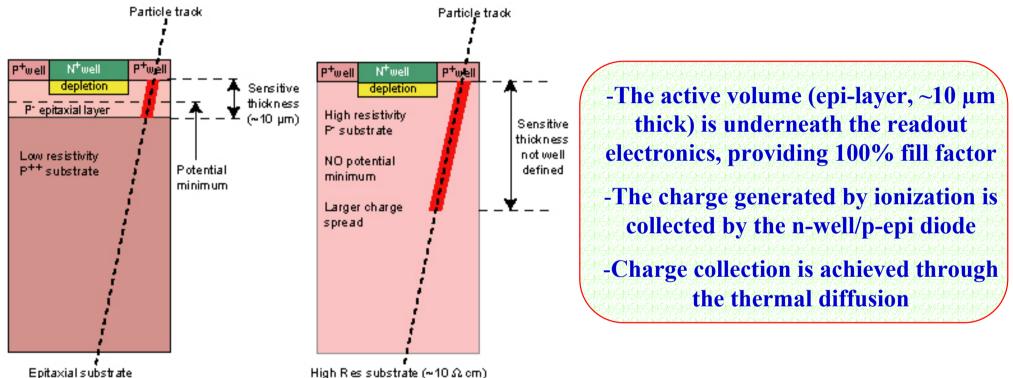

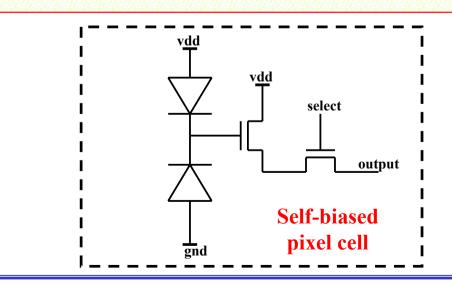

## **CMOS Monolithic Active Pixel Sensors (MAPS): radiation sensor and its readout electronics integrated on the same silicon wafer**

The device can be fabricated using standard, cost effective and easily available twin-tub CMOS process on epi substrate. <u>No post-processing (e.g. bumpbonding) is needed! However, it can be thinned down to less than 50 μm</u>

## Wafer scale MAPS prototype example: Mimosa5 (10<sup>6</sup> pixels) in AMS-0.6 µm CMOS process

Six inch wafer hosts 33 sensors, 1.7×1.9 cm<sup>2</sup> each

Maximum allowed size of a circuit in a standard CMOS process: ~20x20 mm<sup>2</sup> (reticle)

Reticle <u>stitching</u> is needed, in order to get a larger device (a ladder, ~10x2 cm<sup>2</sup>)

#### MIMOSA5

Each reticle is an independent circuit. Periphery logic and bonding pads layout along one side. Simplified stitching of up to 7 reticles in one direction. Still some problems with a yield (~30-40%) but it can be solved (according to some digital imager suppliers).

## Small scale prototype MIMOSA9: "self-bias" arrays with various pitch for tracking study

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 100 P | 1111111111111 |                                        |  |

|----------------------------------------|-------|---------------|----------------------------------------|--|

|                                        |       |               |                                        |  |

|                                        |       |               |                                        |  |

|                                        |       |               | 00000000000000000000000000000000000000 |  |

|                                        |       |               |                                        |  |

|                                        |       |               |                                        |  |

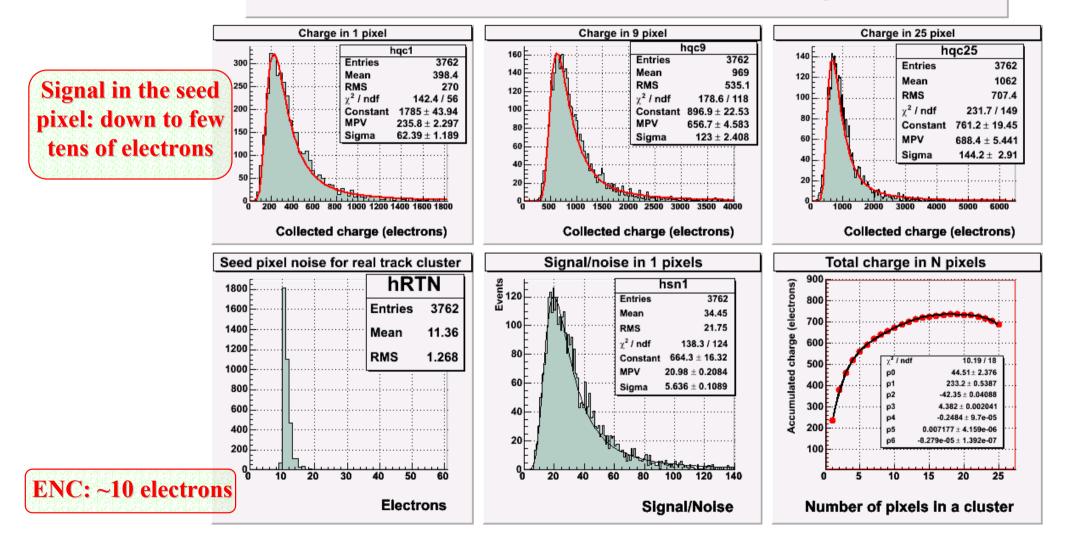

#### A "typical" example from the beam tests: 30µm pitch array, 20°C

M9 ; run 9534; Pl 10, dist 90; Gain 7.200; eff 99.810 +- 0.070; Seed 6.0; Neigh 4.0

EUDET kick-off meeting, DESY, February 2006

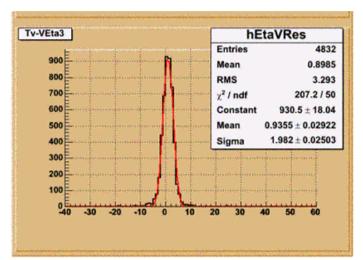

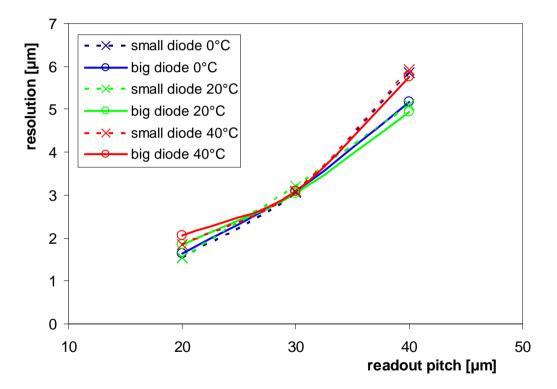

#### **Mimosa9 beam tests: spatial resolution**

**Residual distributions** for 20 μm readout pitch at 20°C Spatial resolution vs. pitch and temperature

Spatial resolution: down to 1.5 µm

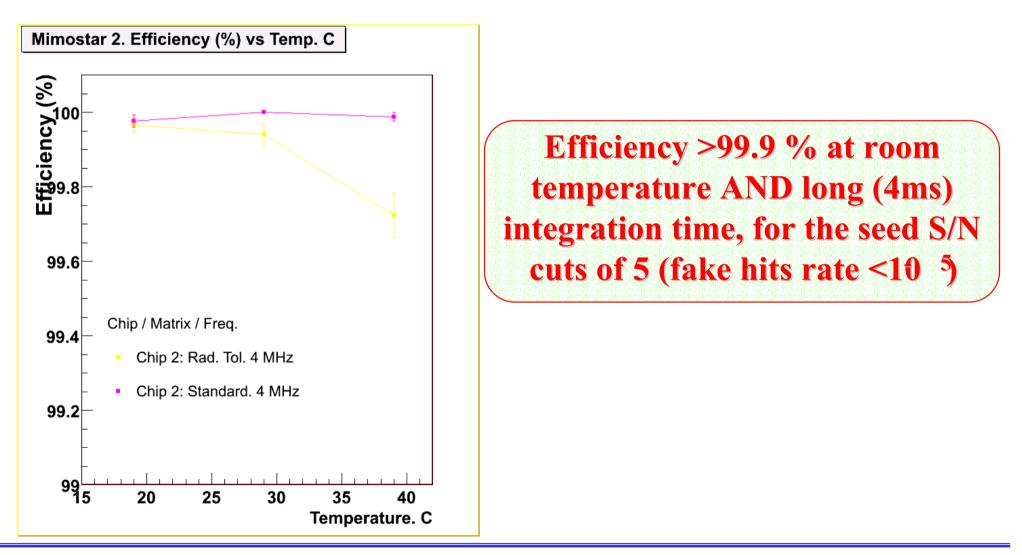

#### Mimo\*2: the demonstrator for STAR experiment microvertex upgrade. Based on radiation tolerant N-well collecting diodes.

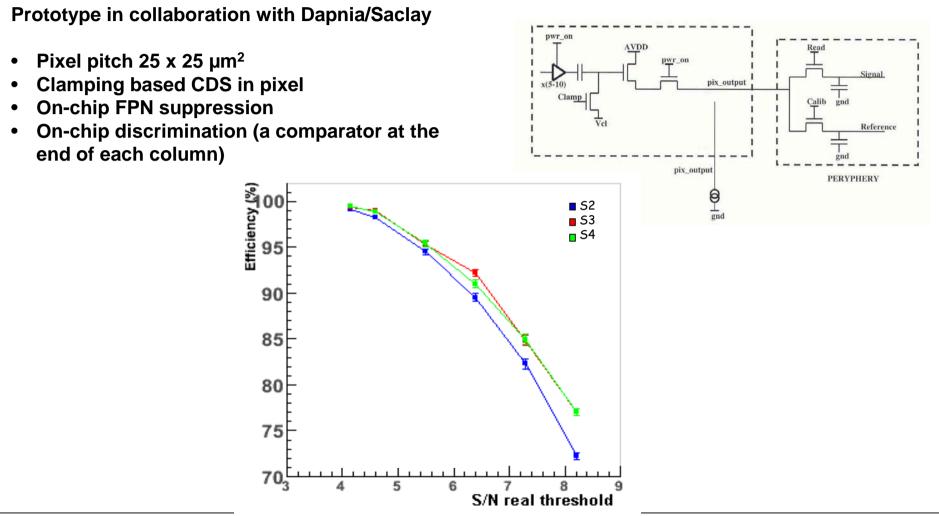

### Mimosa8 (TSMC-0.25µ, 8 µm epi) – a binary readout demonstrator

First demonstration of feasibility of FPN correction using on-chip real time circuitry

The design goal confirmed by the beam tests results: efficiency > 98 %

# **EUDET telescope implementation plans: phase 1** <u>("the demonstrator")</u>

Use of medium-size prototypes developed for STAR microvertex upgrade (existing Mimosa5 as a back-up)

256x256 (640x320) device, 30 µm readout pitch, 7.5x7.5 (19.2x9.6) mm<sup>2</sup> sensitive area, four (two) parallel outputs, the frame readout time (equal to the integration time) < 1 ms (<2 ms), room temperature operation, internal bias setting programmable by JTAG</li>

Sensors available in autumn 2006, the demonstrator beam telescope ready for mid-2007

Specific DAQ, providing real time data AND an easy interface to various users developed in parallel

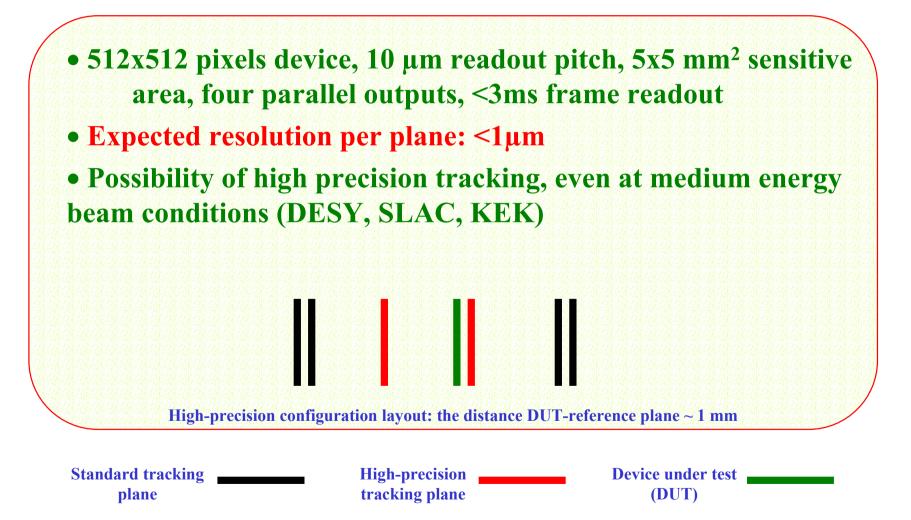

## **Optional high-precision modules for some specific use**

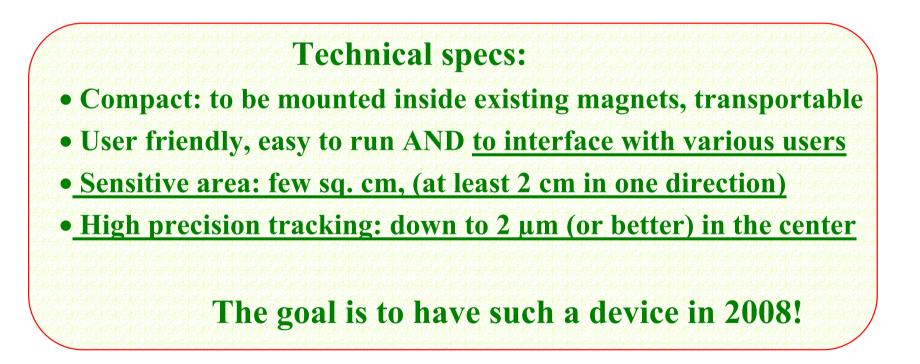

## **Implementation plans: phase 2 ("the ultimate device")**

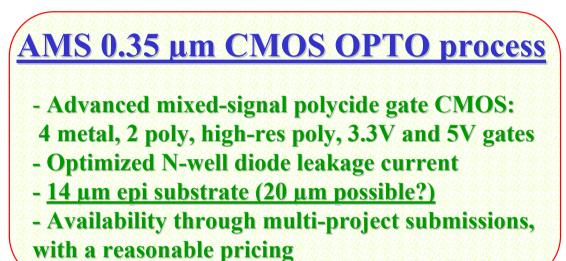

- Specific development for EUDET telescope application: digitally readout sensors

- 800x400 (800x800) pixels device, 25 μm readout pitch, 20x10 (20x20) mm<sup>2</sup> sensitive area, low resolution ADC per column(4-5 bit) for parallel processing, frame readout time (equal to the integration time) << 1 ms</li>

- Prototype sensors (in target AMS-035 OPTO process) available in 2007, the final size devices early 2008

- The ultimate beam telescope ready for the end of 2008!

# Conclusions

Clear and well defined plans, the technology under control, a lot of basic (novel) components firmly tested.

Ready to start, confident about the result!

**Major responsibility within JRA1:**

Sensors: IReS-IPHC (Strasbourg), DAPNIA (Saclay) plus LPSC (Grenoble) and LPC (Clermont-Ferrand) DAQ (very important!): Geneva University, INFN (Milano, Ferrara, Como), Bristol University Integration aspects: DESY, Bonn, Mannheim