### SiW Ecal in AIDA2020 and HIGHTEC

### Roman Pöschl

### CALICE Collaboration Meeting Arlington/TX – March 2016

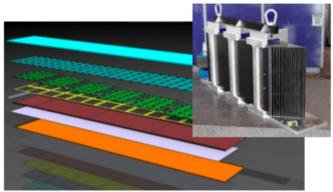

• SiW ECAL is baseline for future LC detectors

Jet energy resolution 3-4%, Excellent photon-hadron separation

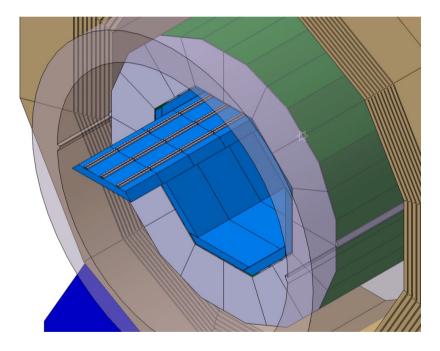

The SiW ECAL in the ILD Detector

#### **Basic Requirements:**

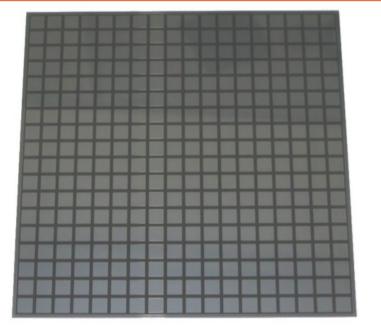

- Extreme high granularity

- Compact and hermetic (inside magnetic coil)

#### **Basic Choices:**

- Tungsten as absorber material X₀=3.5mm, R<sub>M</sub>=9mm, ⊕=96mm Narrow showers Assures compact design

#### - Silicon as active material

Support compact design Allows for pixelisation Robust technology Excellent signal/noise ratio: ~10

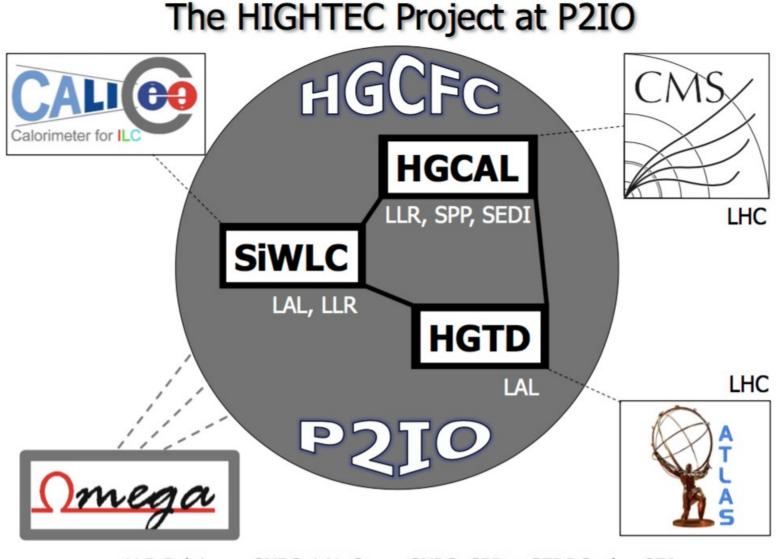

- Until ~2020 SiWEcal (in France) will benefit from two approved projects

Horizon2020 European Research Infrastructure SiW Ecal Beneficiaries: LAL, LLR, LPNHE, LPSC, OMEGA Materiel, HR, Travel

Ile de France South Excellence Cluster P2IO SiW Ecal Beneficiaries: LAL, LLR Material, HR, Travel

Support from overarching bodies like IN2P3 and Ecole Polytechnique is herewith explicitly acknowledged as well

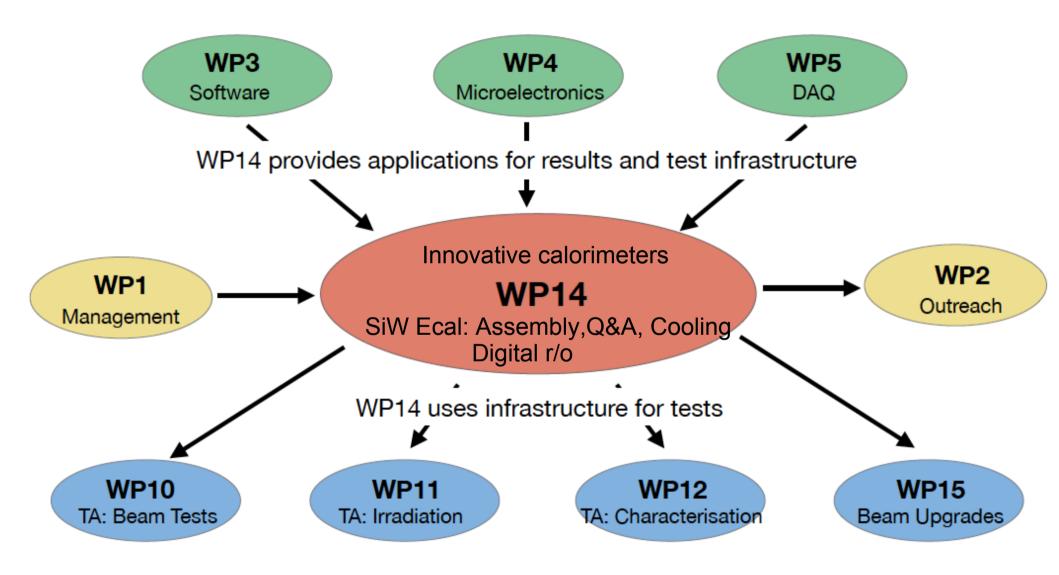

### AIDA2020 Workpackages

AIDA-2020-MS14

AIDA-2020

Advanced European Infrastructures for Detectors at Accelerators

**Milestone Report**

## Assembly and QA chain demonstration for highly granular silicon calorimeters

Boudry, V. (CNRS) et al

23 June 2016

The AIDA-2020 Advanced European Infrastructures for Detectors at Accelerators project has received funding from the European Union's Horizon 2020 Research and Innovation programme under Grant Agreement no. 654168.

Important validation of procedures (Combined) beam test in june 2016 ... to be continued in 2017

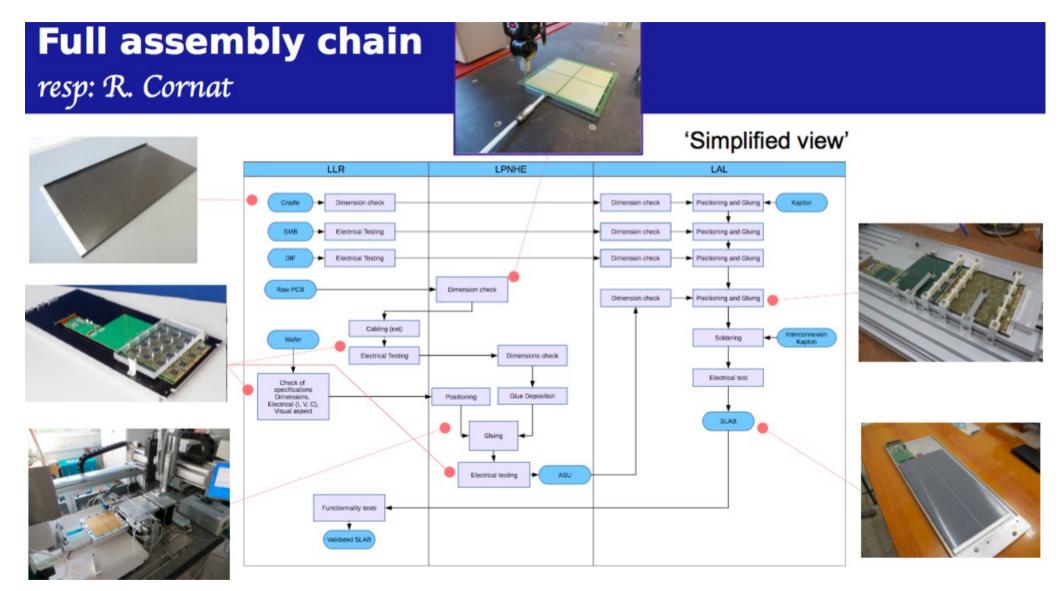

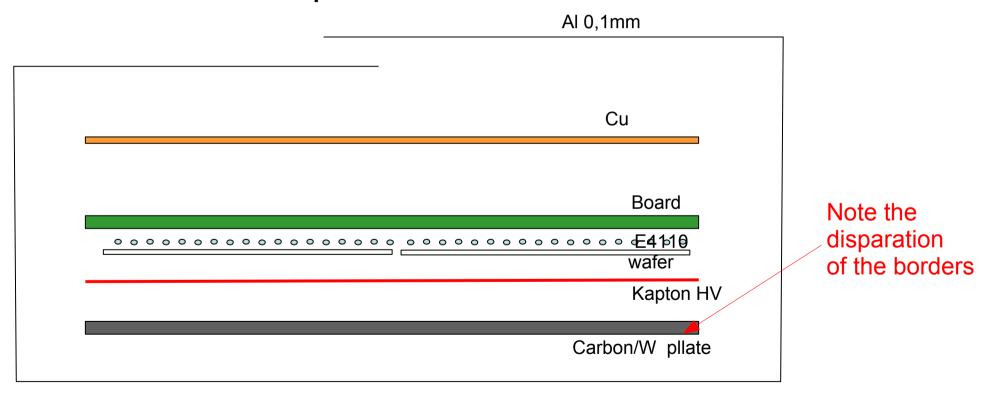

### **Assembly chain - Overview**

#### V. Boudry, ECFA Workshop 2016

| MILESTONE: MS31          |                                                |

|--------------------------|------------------------------------------------|

| Document identifier:     | AIDA2020-MS31                                  |

| Due date of deliverable: | End of Month 18 (October 2016)                 |

| Report release date:     | Dd/09/2016                                     |

| Work package:            | WP14: Infrastructure for advanced calorimeters |

| Lead beneficiary:        | DESY                                           |

| Document status:         | Draft                                          |

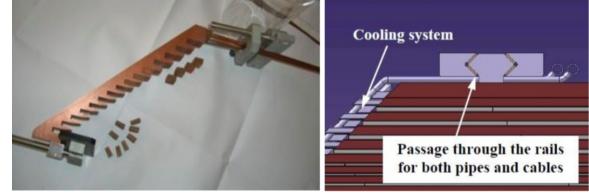

DESIGN OF COOLING SYSTEMS FOR TUNGSTEN

#### Abstract:

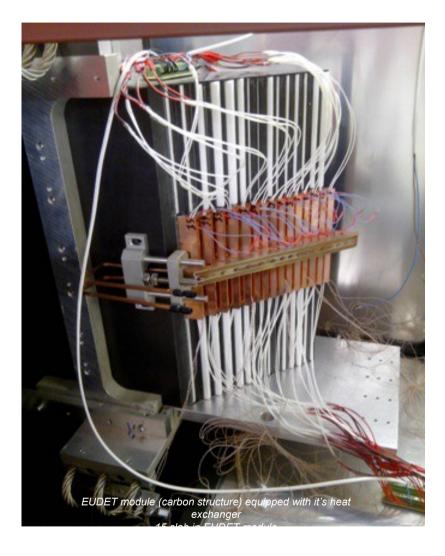

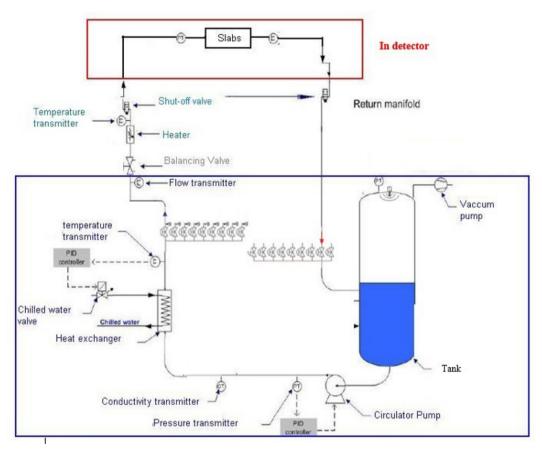

The front-end electronics for both highly granular silicon-based electromagnetic and hadronic calorimeters requires a highly integrated and efficient cooling. Thermal properties of tungsten and carbon fibre based absorber elements drive the cooling concepts of electromagnetic calorimeters; it is the same with the properties of steel absorber stack for hadronic calorimeters. The feasibility and the development of a large leak less water cooling system has been successfully demonstrated for low power calorimeter readout electronics. Thermal modelling and measurements performed on demonstrators constructed within the EUDET project and distributed between two participating labs, fulfil the thermal requirements.

PUBLIC

Grant Agreement 654168

1/26

#### See talk by Denis Grondin

LLR Palaiseau CNRS, LAL Orsay CNRS, SPP + SEDI Saclay CEA

13

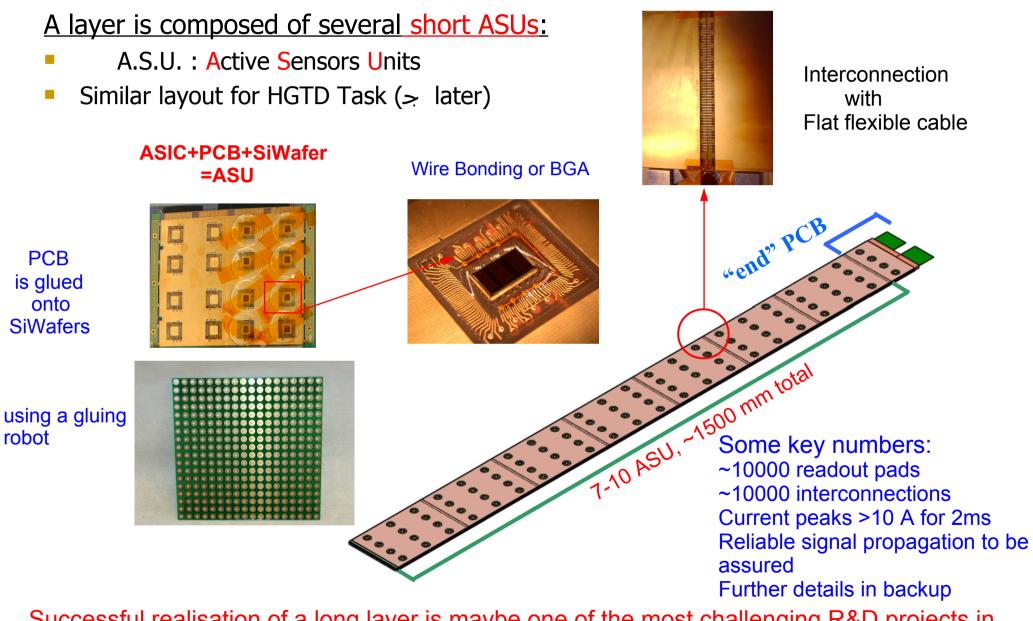

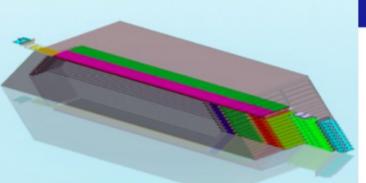

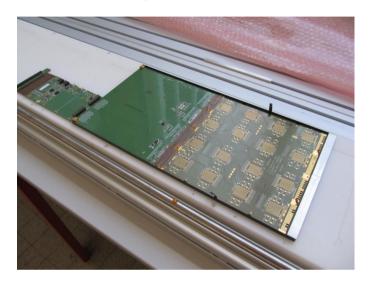

### SiW ECAL – Long layer

## Successful realisation of a long layer is maybe one of the most challenging R&D projects in worldwide detector R&D

Roman Pöschl

CALICE Arlington September 2015

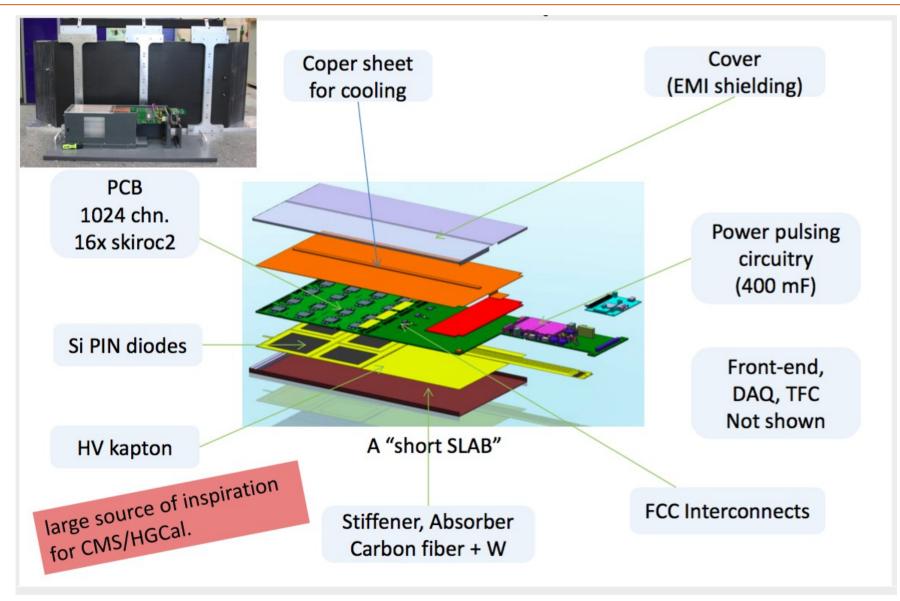

In principle, front-end boards will be chained forming up to 2m long detector SLAB, most of signals in bus

Issue 1 : clock distribution (5 & 50 MHz) Interconnects are not impedance controlled (FFC) One clock line may be loaded by 40 to 80 ASICS

- ⇒ Use of MLVDS adapted with 100 Ω on both sides, 100 mVpp remaining signal at the end (6 Ohms loss/board, 20-40 pF/board, up to 10 boards)

- ⇒ Next version ASIC will have a PLL generating the highest frequency

- Issue 2 : Power distribution (12 A pulses) & blocking capacitors (tested with FET switches as loads)

$\Rightarrow$  Current taken from a 800mF super cap (16m $\Omega$  ESR) + 2mF/board

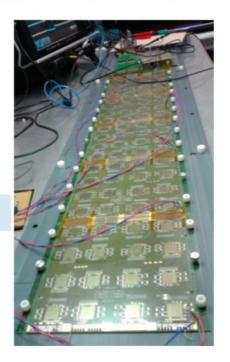

Along 6 boards, static loss is 250 mV due to connectors (w/o chips). May foresee to distribute power in a star topology. **4 boards SLAB being assembled at LAL**

large C-W structure exists

#### R. Cornat LLR

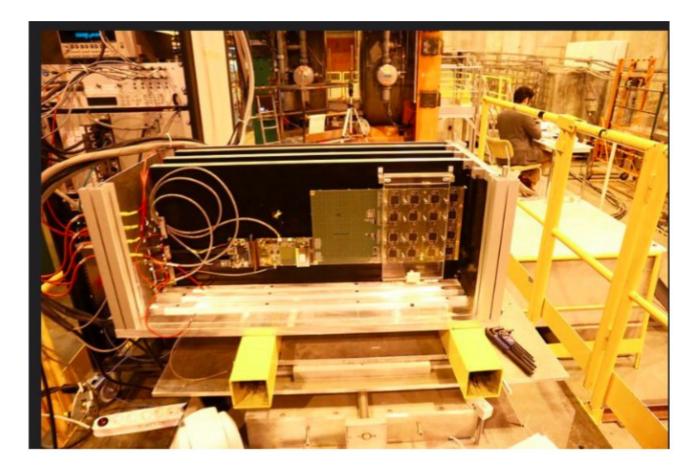

### Test of HW: long slab

#### 8-10 ASUs stitched in Power-Pulsing

- what can't be done with a small RA source ?

- perf in strong B field, with PP.

#### V. Boudry, ECFA Workshop 2016

Roman Pöschl

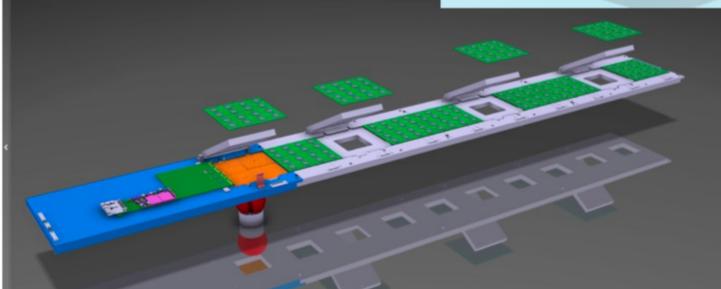

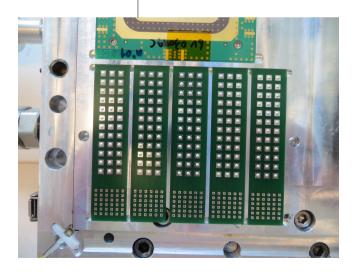

### **Assembly of SiW Ecal layers**

### SiW ECAL Assembly

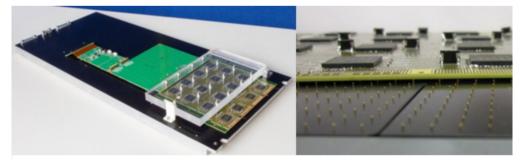

#### Pick and place

#### Precise alignment

#### Ready for test

- Assembly steps are validated with short layers

- Need big step towards long layer to assure high quality product

- Automated pick-and-place and alignment

- Interplay of many different working steps

- a) Assembly proper

- b) Continuous control of up to 8 ASUs during assembly

- Successful product requires a lot of testing and exercising of well trained technical staff!!!

- Strong synergy with HGTD Task and CMS Task (?)

<u>Guiding lines :</u> Ease of assembly Easetofabricate the elements Robustness Compactness

#### J. Bonis/A. Thiebault

#### Two major options:

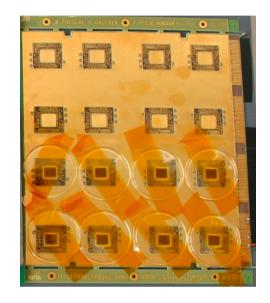

#### **BGA** packaged chips

#### BGA version is considered as save incremental step:

test of chips before soldering ; Space for external decoupling capacitors Symmetric stacking will improve flatness, good for wafer gluing Optimal shielding of signal traces Solution for current beam tests

May need revision to facilitate assembly process Heat loss during interconnection

#### PCB with naked die

- Thin board (~1.2mm)=> maximal channel density

- Tests since 2015

Integration into ECAL prototype during HGCFC project

Intensive test programme

e.g. Noise and cross talk

#### Details see previous talk

Details see electronics session this morning

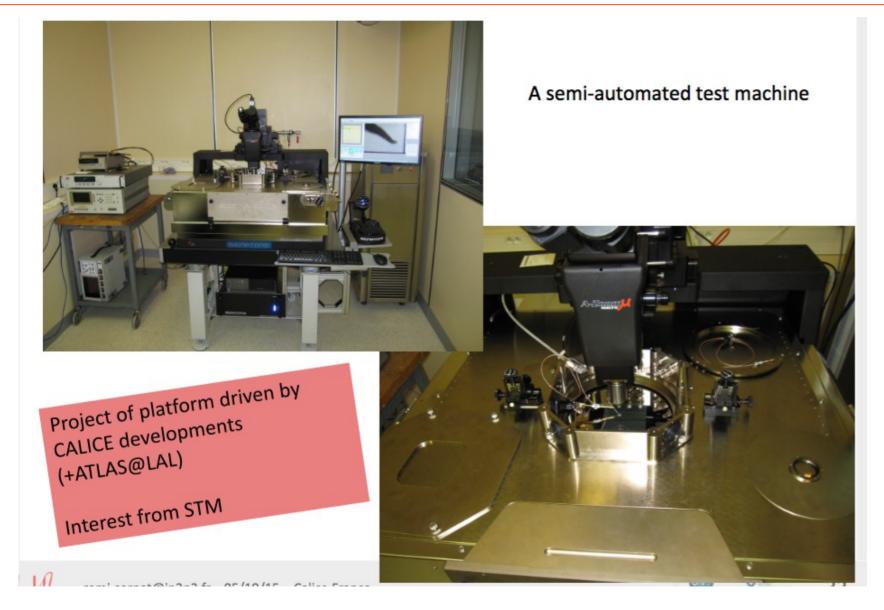

### SiW Wafer R&D

#### SiW Wafer tests:

Desktop setup with unglued sensors

Well advanced infrastructure for full wafer characterisation => Wafer tests within HGCFC Common interest of all branches of project

High resistive Si Wafer from Hamamatsu Photonics

- Excellent quality!!!

e.g. leakage current O(nA/pixel)

- However, expensive (2kEUR/wafer) and Large quantity needed requires quest for Further producers e.g. LFoundry

Laser station

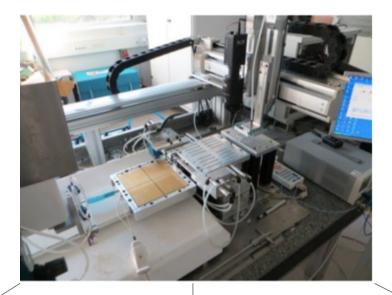

### **Versatile Gluing Robot**

Done, FEV11\_BGA

Done, HGTD-LGAD

Under discussion, FEV\_COB

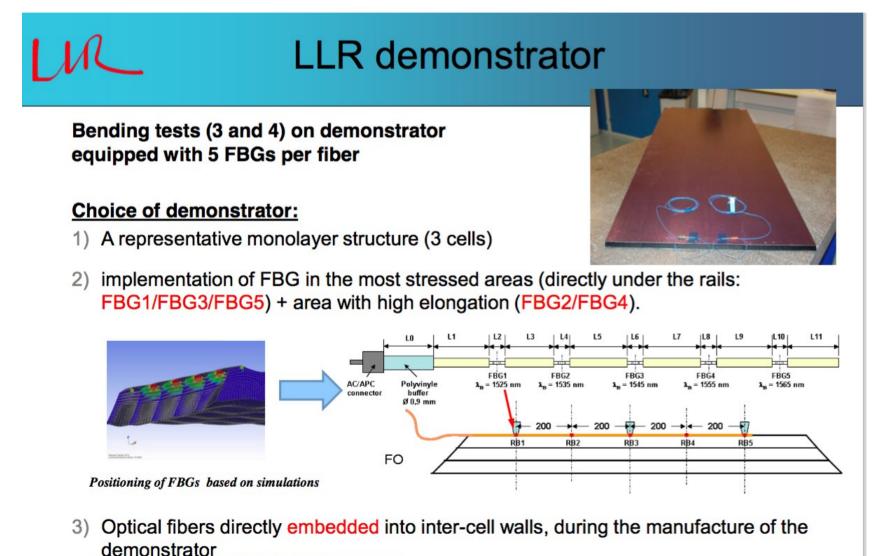

Use of Fiber-Bragg Gating Sensors for the characterisation of deformation of composites structures

### **Towards Full Sized Cooling system**

#### Details in next talk

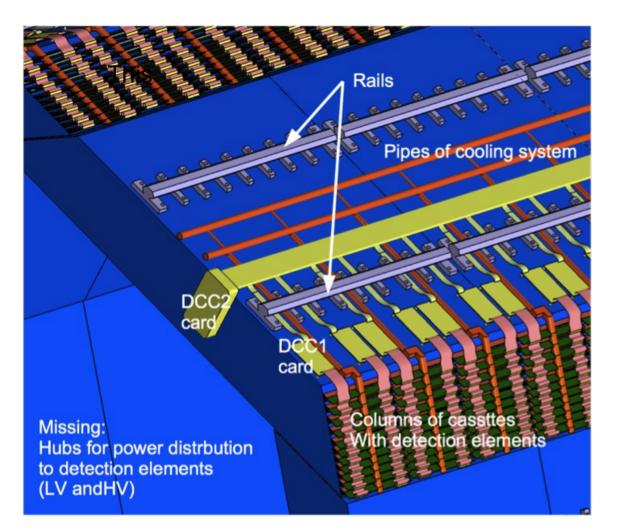

### Readout, power supply and all that ...

How to fit services into ~3cm between Ecal and Hcal in ILD

#### N.B. Image by M. Anduze and H. Videau Labels by R.P., picture will vanish from uploaded slides

- SiW Ecal R&D is more challenging than ever

- Beam tests with short layers

- Gradual move to system aspects

- Long layers

- Full sized cooling system

- Service integration in tight space

- Quality and assembly chain

- Stress tests for alveolar structure

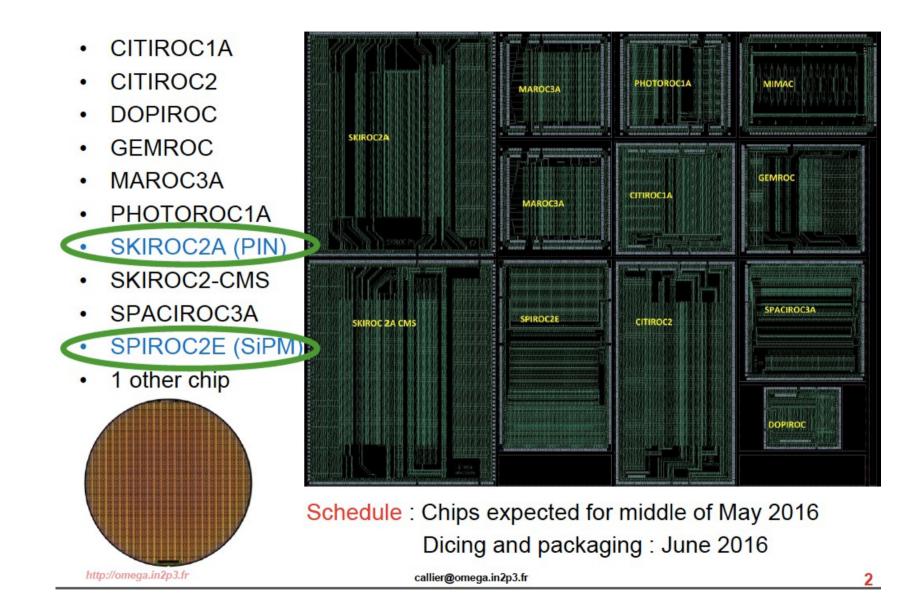

- Important R&D on core components and techniques

- Silicon wafers

- ASICs

- Thin PCBs

- Gluing

- HIGHTEC and AIDA-2020 provide significant funding for these studies

- Projects run until ~end of 2019

- May match decision period on ILC or not

- Synergies with ongoing LHC detector R&D

### SiW ECAL – Short layer

#### Between 12 and 15 short layers for HGCFC beam tests

R. Cornat LLR

Roman Pöschl

### **SiW ECAL – First short layers**

#### Test bench and beam test setup of first short layers with preliminary assembly

#### V. Boudry LLR

# Backup

### **Platform CAPTINNOV**

... has been already used for CALICE wafer cahracterisation

R. Cornat LLR

Roman Pöschl

CALICE Arlington September 2015