# SiW Ecal Electrical interfaces

- A (still) poor man's view -

Roman Pöschl, Henri Videau

### ILD Integration Kick-off Meeting, LAL Orsay Feb. 2018

Disclaimer for Ecal:

- I work out from what I have said back in September integrating some first feedback from electronic engineers at LAL and discussion with Henri

- Still all mistakes are mine

- Towards serious revision and prototyping in coming months!!!

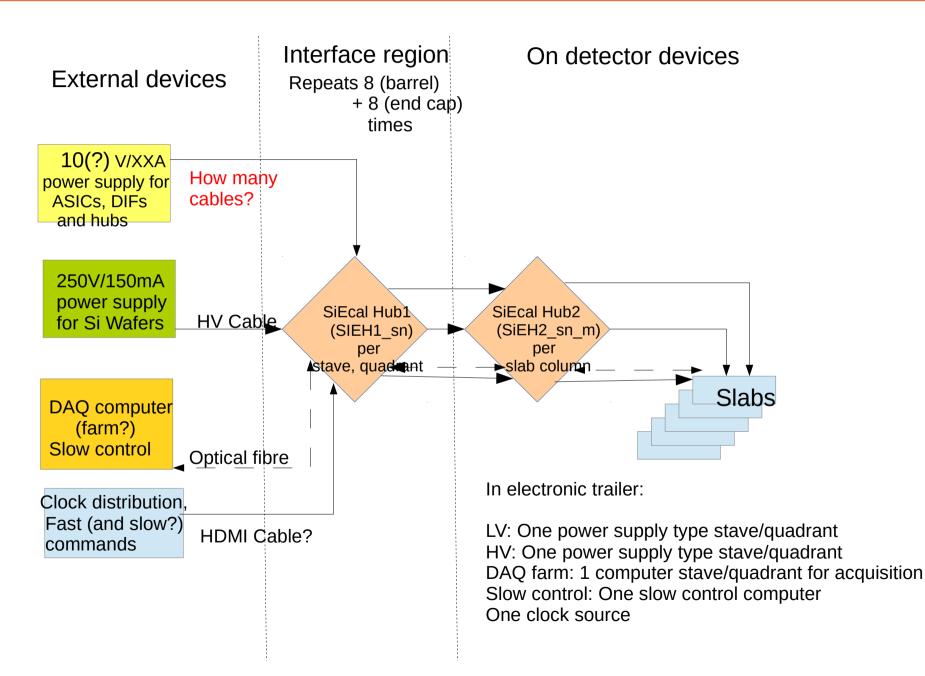

## **ICD SiECal – Electrical Interfaces I**

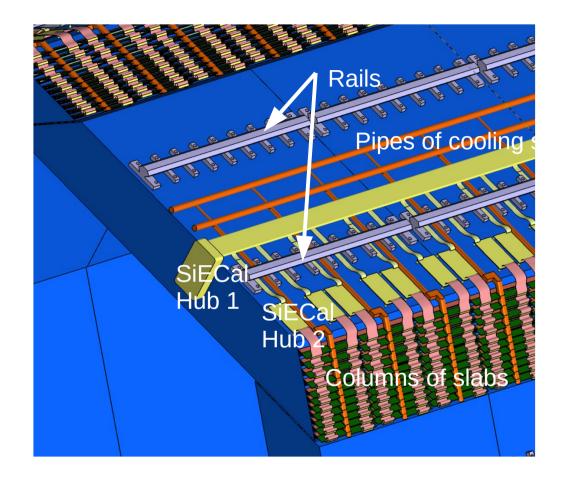

• SiEcal Hub 1 (hub to external supplies and DAQ)

#### SiECal internal components

- SiEcal Hub2

- (internal hub to be checked whether heat source)

Disclaimer: Design subject to change Question 1: 1 big SiEcal Hub 1 or a few smaller ones

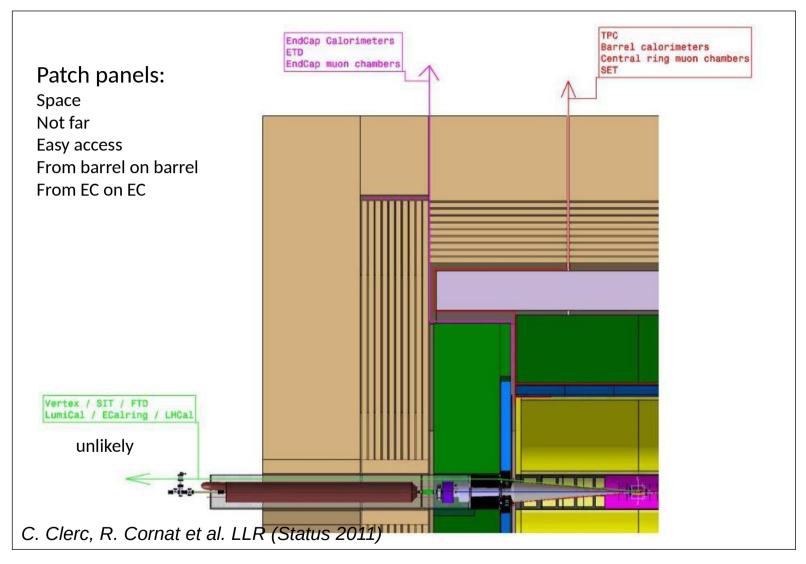

### **SiECAL – Service lines**

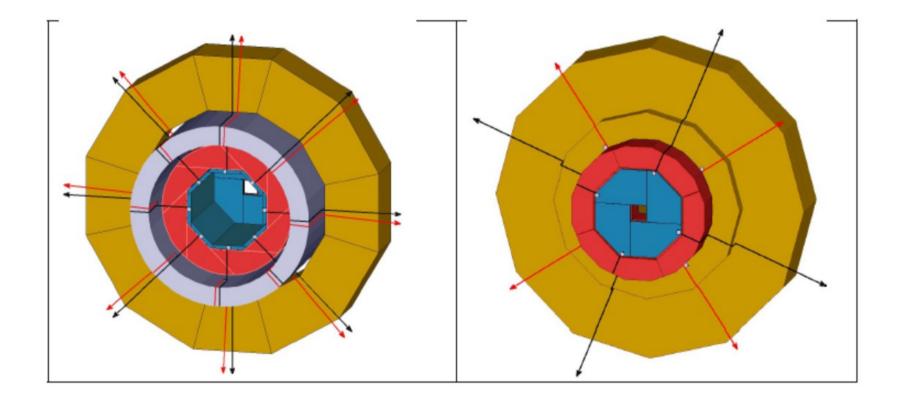

- Service lines leaving from barrel

- Service lines leaving from endcap

Details see talk by Henri

- LV

- Need to power Chip AVDD, DVDD, DIF and hubs

- Peak currents for AVDD, DVDD will be fabricated by on-detector capacitances

- Power

- "On PCB": ~2.1 kW total Ecal

- DIF: ~2.5kW (0.3 W, will be operated in continuous mode)

- Hubs: ~300 Hubs a << 50 W -> 1.5 kW if 5 W/hub (to be validated in 2018)

- => Total: 4.6 + 1.5 kW = 6.1 kW

- Power supply will be of type Lambda TDK Genesis 1U, need 16 supplies (x2 for redundancy?)

- => 2 racks, more to reduce power density

- HV

- 300 V / 200 mA per stave/end cap quadrant

- => Total Power consumption ~1kW

- Assume 1 power supply per stave/end cap quadrant (may be too much)

- => 16 power supplies (x2 for redundancy), e.g. iSeg supplies => should fit into 1-2 racks

- Computing and slow control

- ....

Grand total:

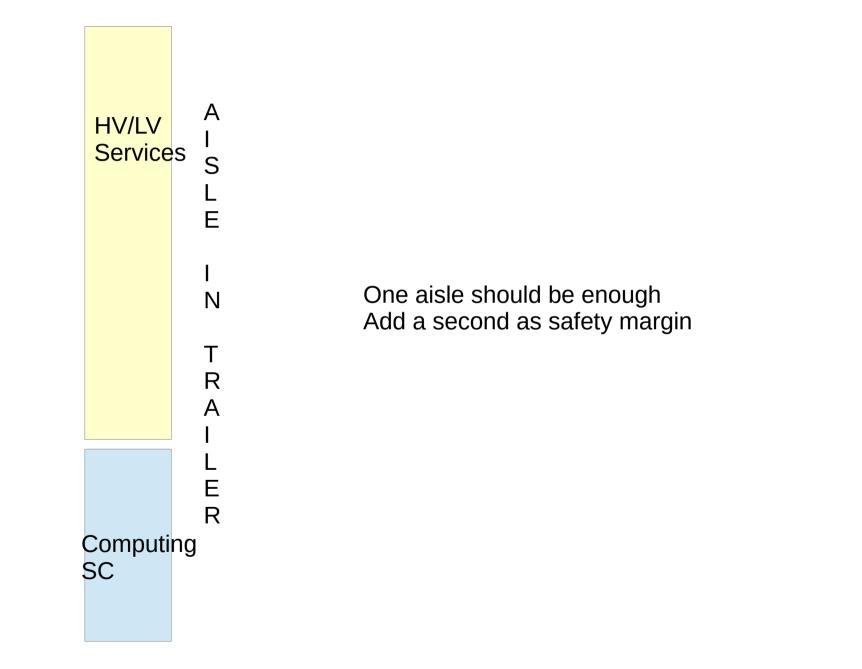

Power: ~7 kW Space: 4 racks w/o computing

- Regard power cables that enter into first hub (SiEcal Hub1)

- LV Example for barrel stave (5 trapezoidal modules)

- One stave consumes about 320 A (including factor 2 safety margin)

- This leads to a power loss of about 10W/m along the entering power cable(s)\*

- Question 1: Do we bring this current from outside to the detector

- Question 2: If yes, one thick or a few thinner cables?

- Question 3: If no, what about DC-DC Converters?

- HV

- About factor 10 less current

- Remark on hubs

- Estimation on power consumption given at KEK 50 W was largely exaggerated (mea culpa)

- 5 W is more realistic

- These need to be designed carefully to avoid that they become hotspots

- Studies have started

using technical data on required cable surfaces given on

https://www.sab-kabel.de/kabel-konfektion-temperaturmesstechnik/technische-daten/ kabel-leitungen/sicherheitsgerechte-verwendung-von-kabeln-und-leitungen/grenzbedingungen/ kabelquerschnitt-berechnen-strombelastbarkeit-tabelle.html

- Design architecture of power distribution (and clock distribution and data transfer)

- More professional than so far by R.P.

- How many cables for power supply/octant (same for endcap quadrants)

- 1 big or a few smaller ones?

- DC-DC Converters or not, if yes which ones and where?

- What is the real power dissipation of the supply cables for the LV?

- Looks like 10W/m is a realistic number

- Select suited cables

- Come up with a design of the hubs and an estimation of the power consumption

- Including prototypes

- Ongoing work

# Backup ....

# **Cabling and power**

A reminder

#### Study for DBD needs regular update!!!! Use ICD