### Timing Calibration of the CALICE AHCAL Prototype

Lorenz Emberger

Tokyo Analysis Workshop August 2018

Showing work from Christian Graf

Why do we need timing?

Why do we need timing?

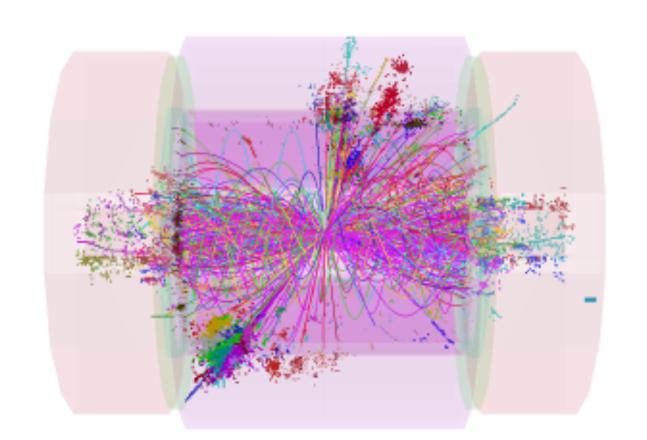

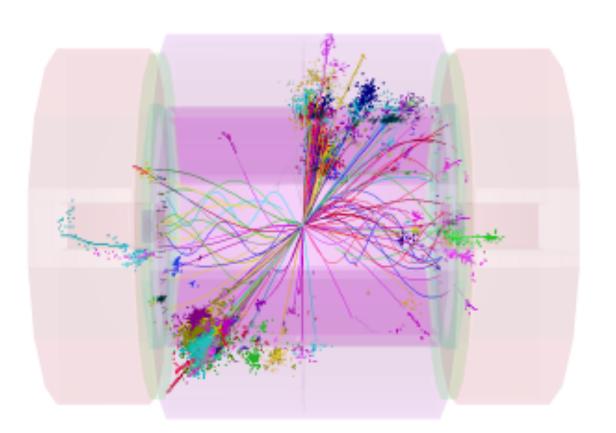

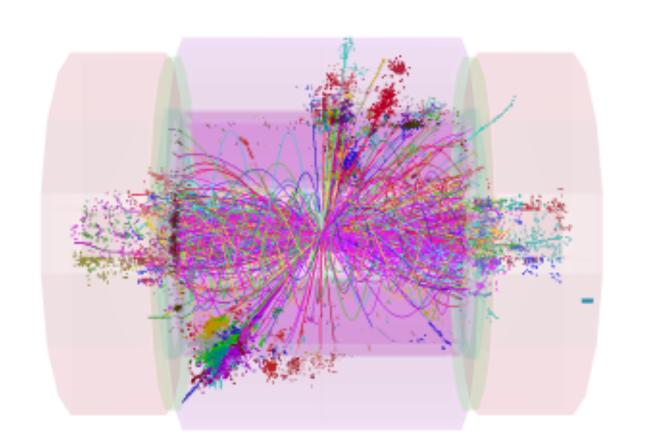

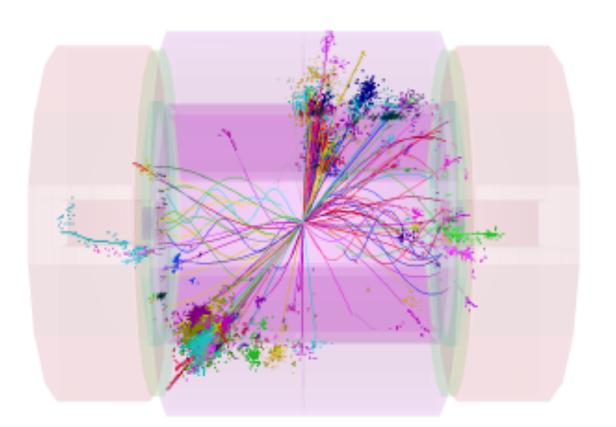

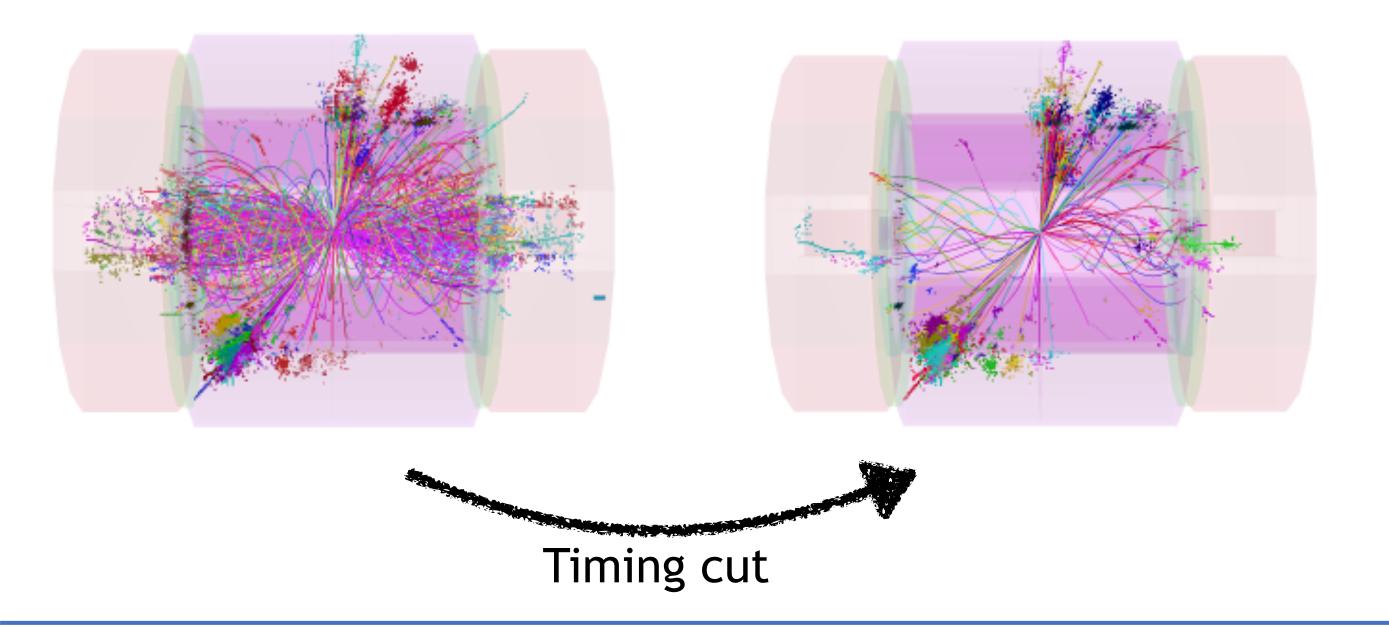

• Reject background

Timing cut

#### Why do we need timing?

- Reject background

- Aid clustering

Timing cut

Why do we need timing?

- Reject background

- Aid clustering

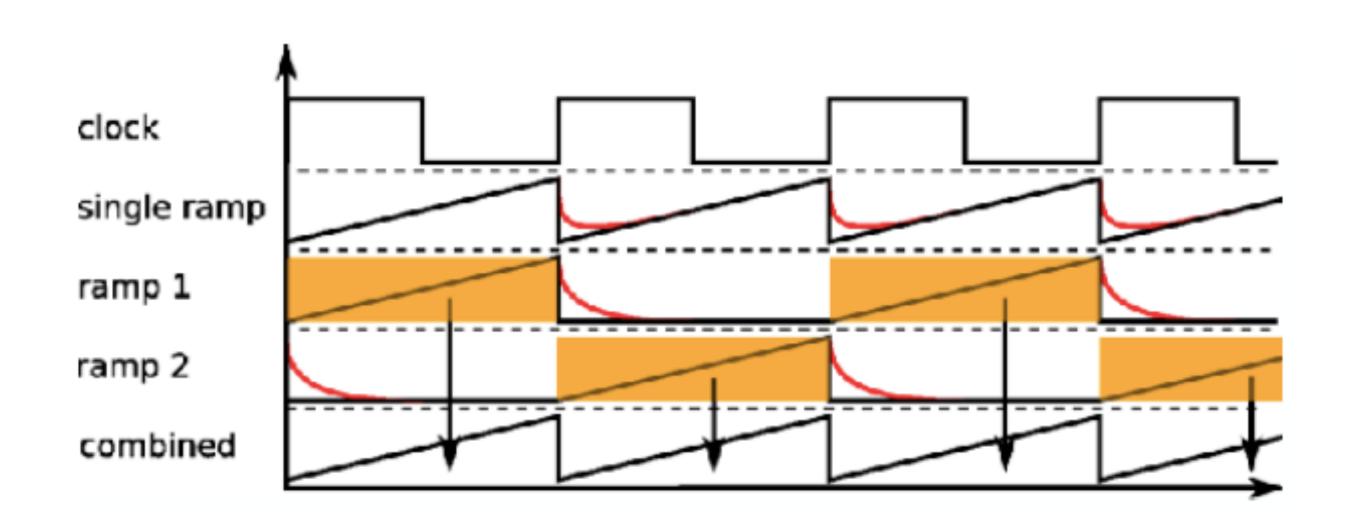

- Use in software compensation to identify components of hadronic showers

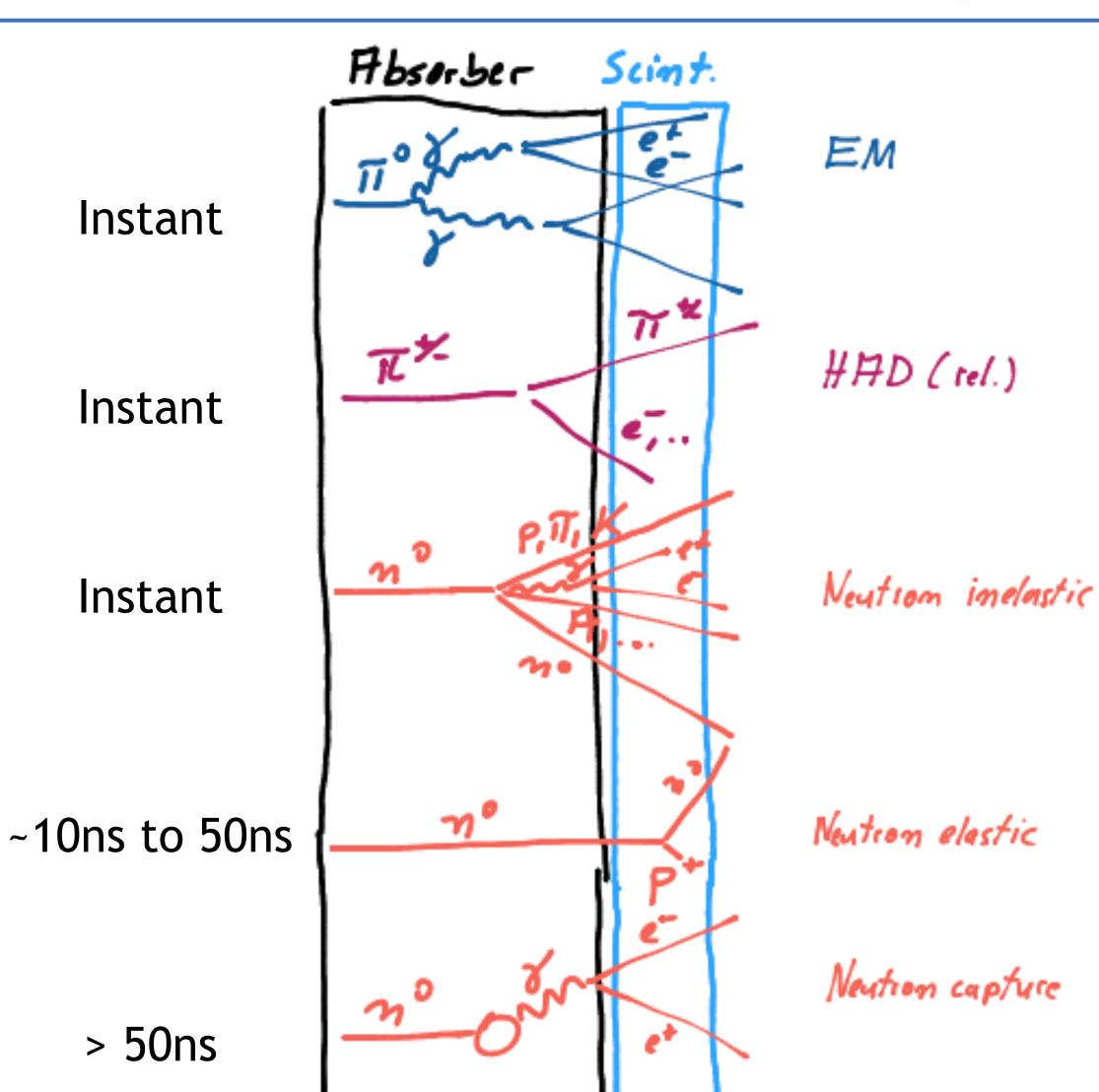

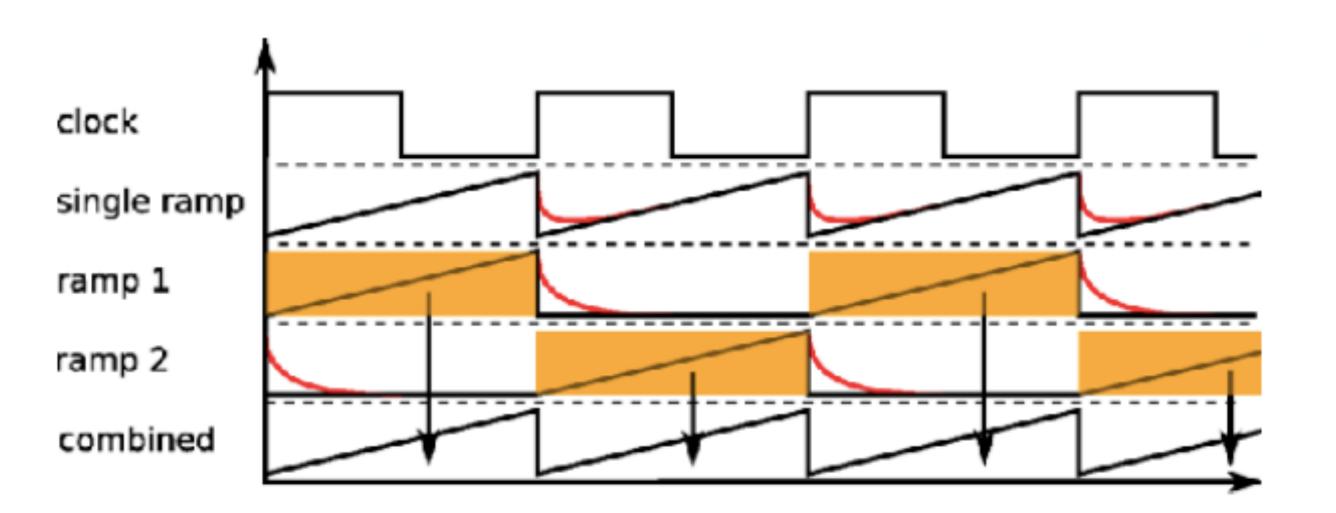

Timing unit on Spiroc2E: <u>TDC</u>

1. BIF gives time reference (BxID)

Timing unit on Spiroc2E: <u>TDC</u>

- 1. BIF gives time reference (BxID)

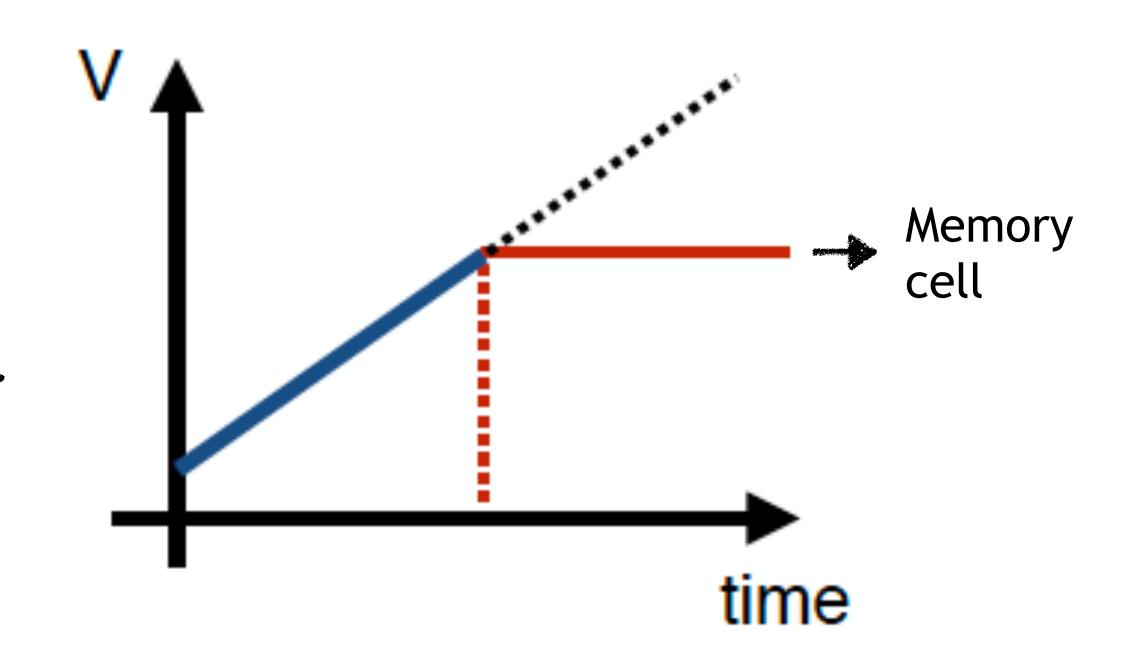

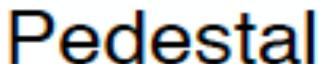

- 2. Ramp up voltage for maximum 3920ns

- Slope for even and odd BxID

Timing unit on Spiroc2E: <u>TDC</u>

- 1. BIF gives time reference (BxID)

- 2. Ramp up voltage for maximum 3920ns

- Slope for even and odd BxID

- 3. On hit, the ramp stops

- 4. Current voltage is stored in memory cells and digitized by ADC

Timing unit on Spiroc2E: <u>TDC</u>

- 1. BIF gives time reference (BxID)

- 2. Ramp up voltage for maximum 3920ns

- Slope for even and odd BxID

- 3. On hit, the ramp stops

- 4. Current voltage is stored in memory cells and digitized by ADC

- 5. Resulting TDC value needs to be related to hit time in ns → Calibration

Per chip

Slope

Per memory cell

- All memory cells to be calibrated against BIF clock (T0)

- Calibration needs to achieve permill precision to achieve sub-ns time resolution→need ~100 hits per memory cell

calice\_calib/calib/Ahc2TimingCalibrator.cpp

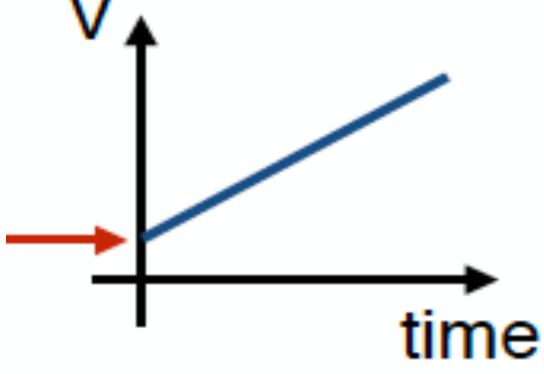

- All memory cells to be calibrated against BIF clock (T0)

- Calibration needs to achieve permill precision to achieve sub-ns time resolution→need ~100 hits per memory cell

- 1. Extract slope for even and odd BxID per chip

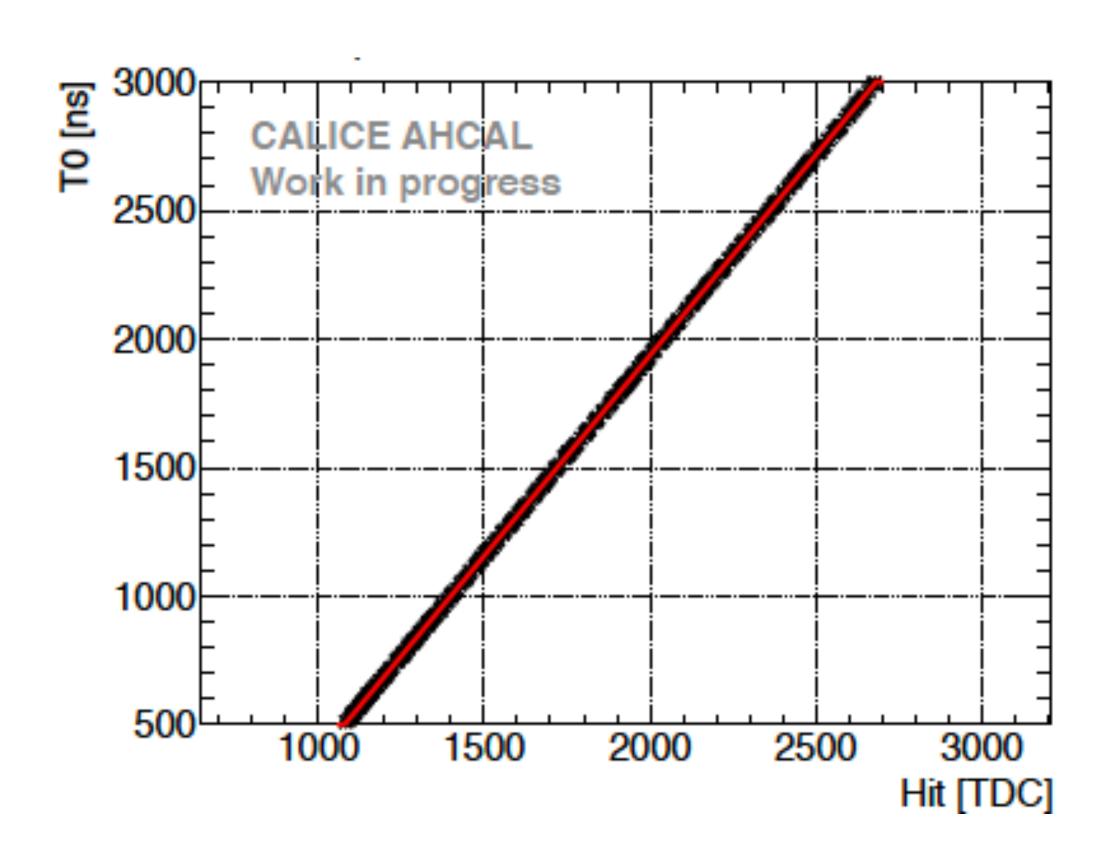

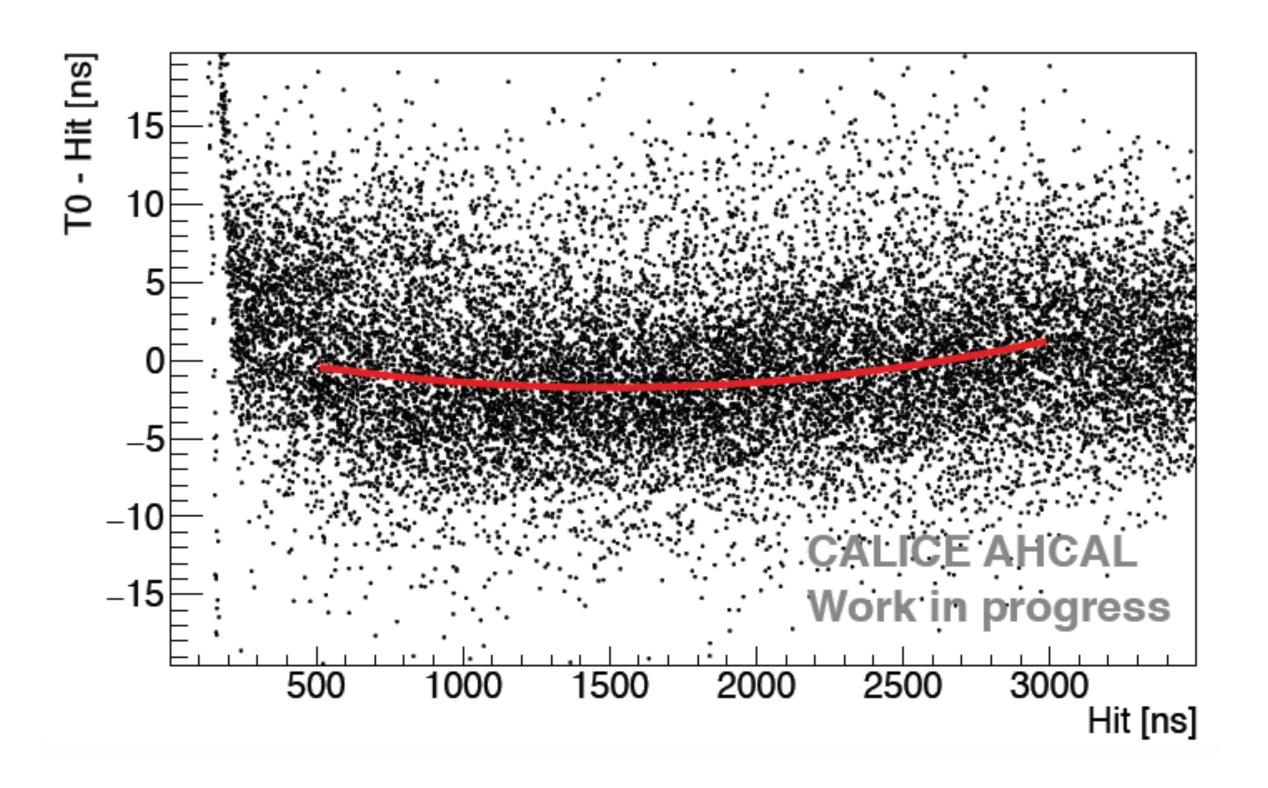

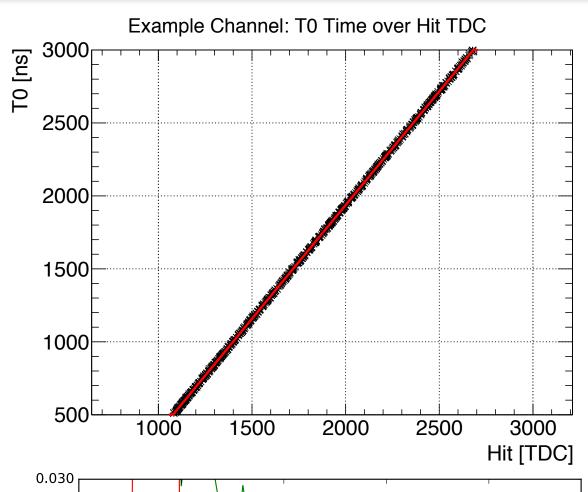

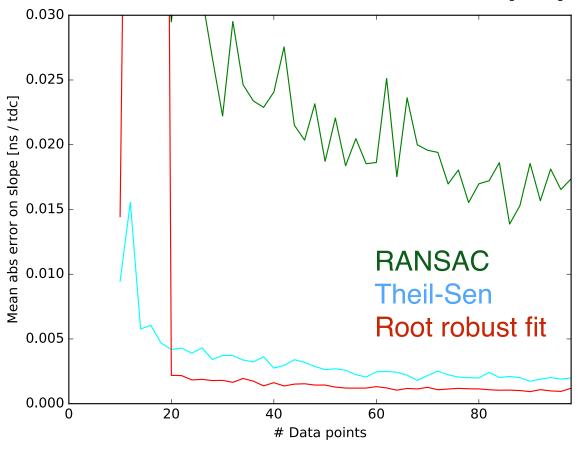

- 1. Perform robust linear fit between 500ns and 3000ns for first memory cell of every channel

- 2. Reject every hit which is off by >10ns

- 3. Take median of all slopes as common slope for chip

calice\_calib/calib/Ahc2TimingCalibrator.cpp

- All memory cells to be calibrated against BIF clock (T0)

- Calibration needs to achieve permill precision to achieve sub-ns time resolution→need ~100 hits per memory cell

- 1. Extract slope for even and odd BxID per chip

- 1. Perform robust linear fit between 500ns and 3000ns for first memory cell of every channel

- 2. Reject every hit which is off by >10ns

- 3. Take median of all slopes as common slope for chip

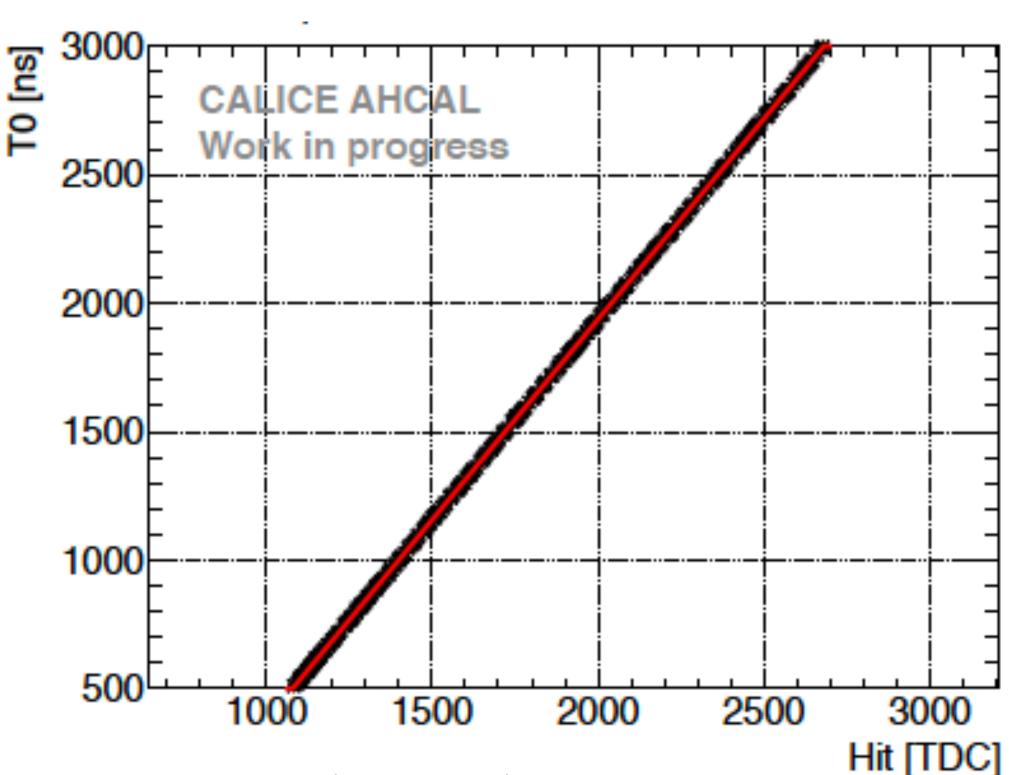

- 2. Extract offset for every memory cell

- 1. Perform linear fit for every memory cell with fixed slope of the respective chip

calice\_calib/calib/Ahc2TimingCalibrator.cpp

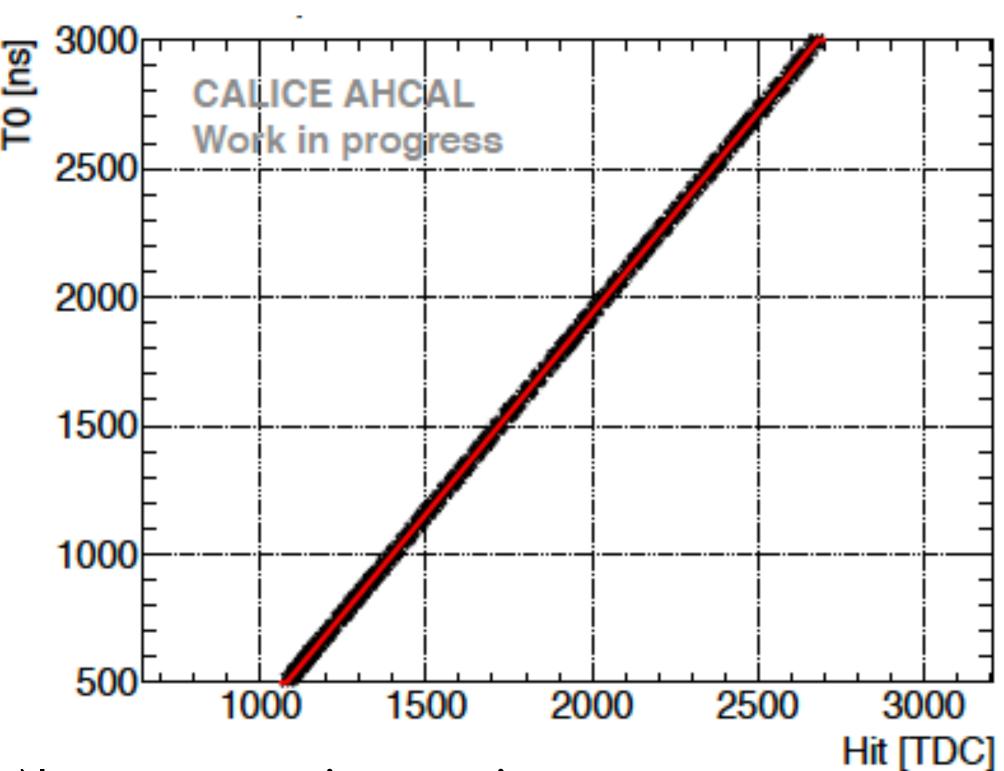

- All memory cells to be calibrated against BIF clock (T0)

- Calibration needs to achieve permill precision to achieve sub-ns time resolution→need ~100 hits per memory cell

- 1. Extract slope for even and odd BxID per chip

- 1. Perform robust linear fit between 500ns and 3000ns for first memory cell of every channel

- 2. Reject every hit which is off by >10ns

- 3. Take median of all slopes as common slope for chip

- 2. Extract offset for every memory cell

- 1. Perform linear fit for every memory cell with fixed slope of the respective chip

calice\_calib/calib/Ahc2TimingCalibrator.cpp

Not yet on main repository:

- need two additional DB collections

- TimeOffsetMem\_Even, TimeOffsetMem\_Odd

- All memory cells to be calibrated against BIF clock (T0)

- Calibration needs to achieve permill precision to achieve sub-ns time resolution→need ~100 hits per memory cell

- 1. Extract slope for even and odd BxID per chip

- 1. Perform robust linear fit between 500ns and 3000ns for first memory cell of every channel

- 2. Reject every hit which is off by >10ns

- 3. Take median of all slopes as common slope for chip

- 2. Extract offset for every memory cell

- 1. Perform linear fit for every memory cell with fixed slope of the respective chip

- 3. Calculate hit time by

$$t_{hit}[ns] = TDC_{hit} \cdot Slope \left[ \frac{ns}{TDC} \right] + Offset [ns] - T_0$$

calice\_calib/calib/Ahc2TimingCalibrator.cpp

Not yet on main repository:

- need two additional DB collections

- TimeOffsetMem\_Even, TimeOffsetMem\_Odd

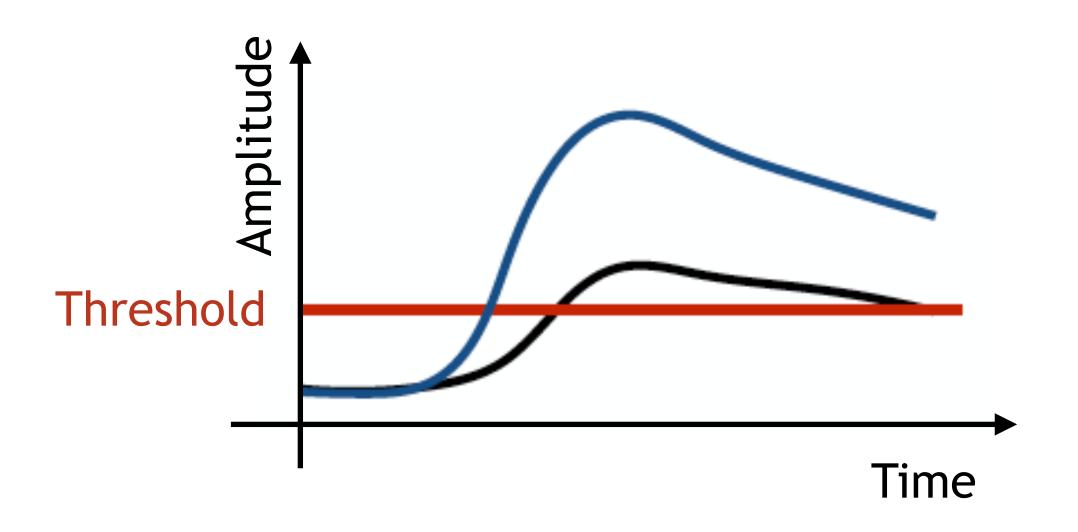

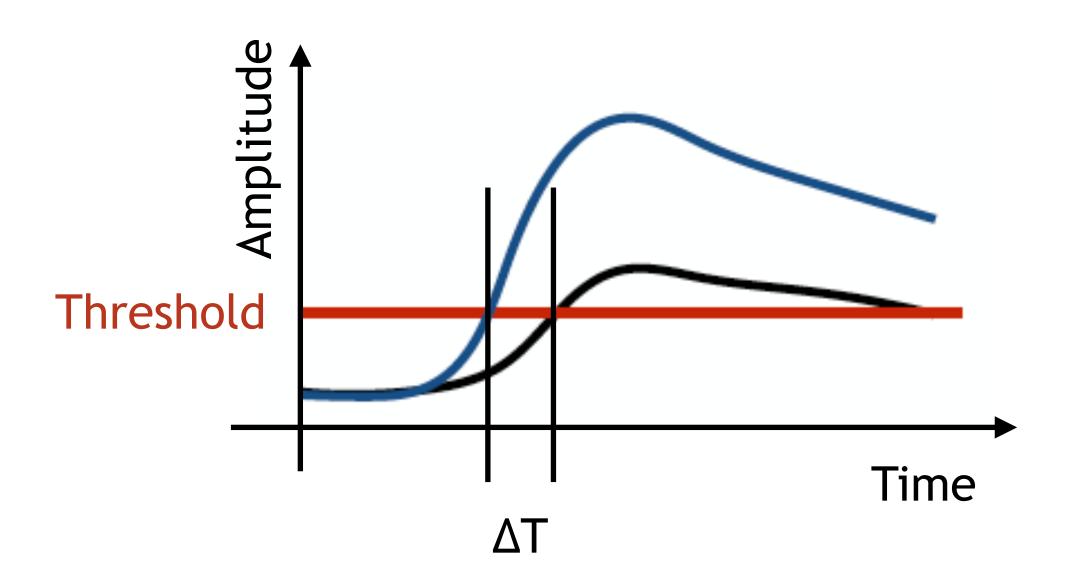

#### Time walk correction

#### Time walk correction

#### Time walk correction

Add Database entries for correction factors

#### Time walk correction

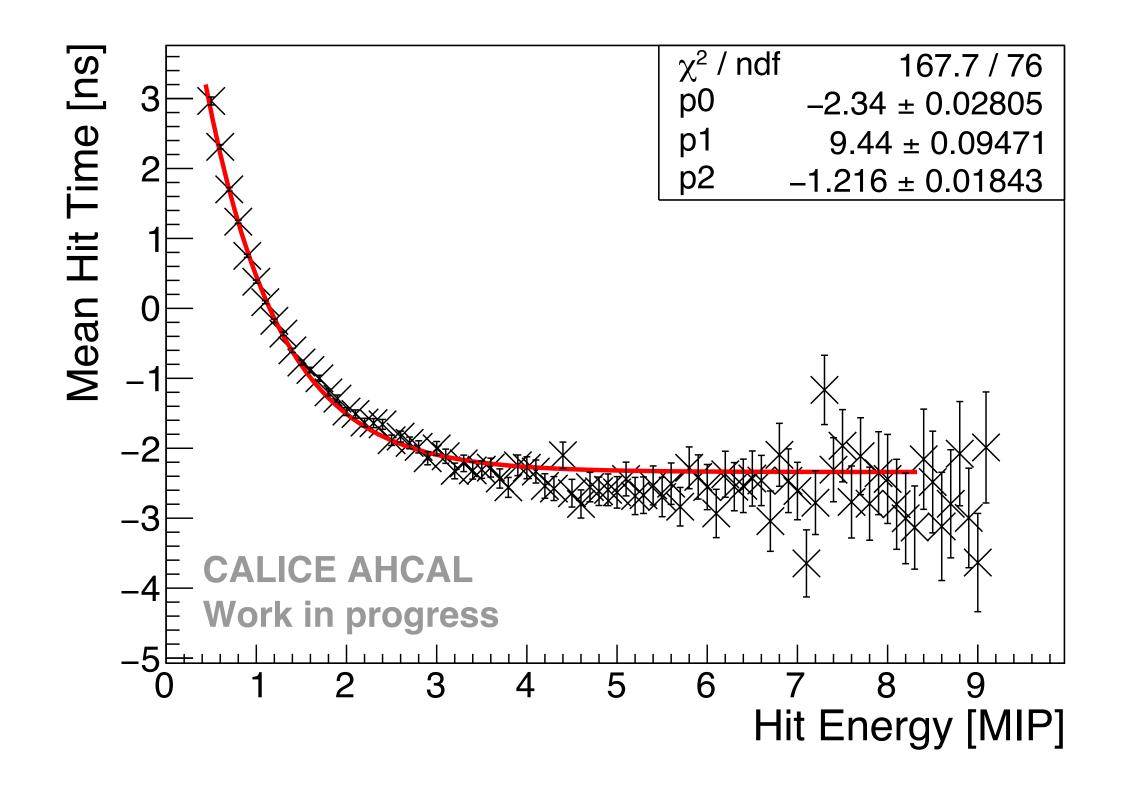

### $\chi^2$ / ndf 167.7 / 76 Mean Hit Time [ns $-2.34 \pm 0.02805$ $9.44 \pm 0.09471$ $-1.216 \pm 0.01843$ CALICE AHCAL Work in progress Hit Energy [MIP]

#### Non-linearity correction

Add Database entries for correction factors

### Time Resolution - T0 vs BIF

16

Time resolution given by the distribution of residuals of the linear fit

#### 2015 August - T0 Channels

### Time Resolution - T0 vs BIF

Time resolution given by the distribution of residuals of the linear fit

2015 August - T0 Channels

2017 May - BIF Clock

Relative to BIF time: 5ns (FWHM), 4.3ns (RMS)

-> Better muon time resolution with BIF

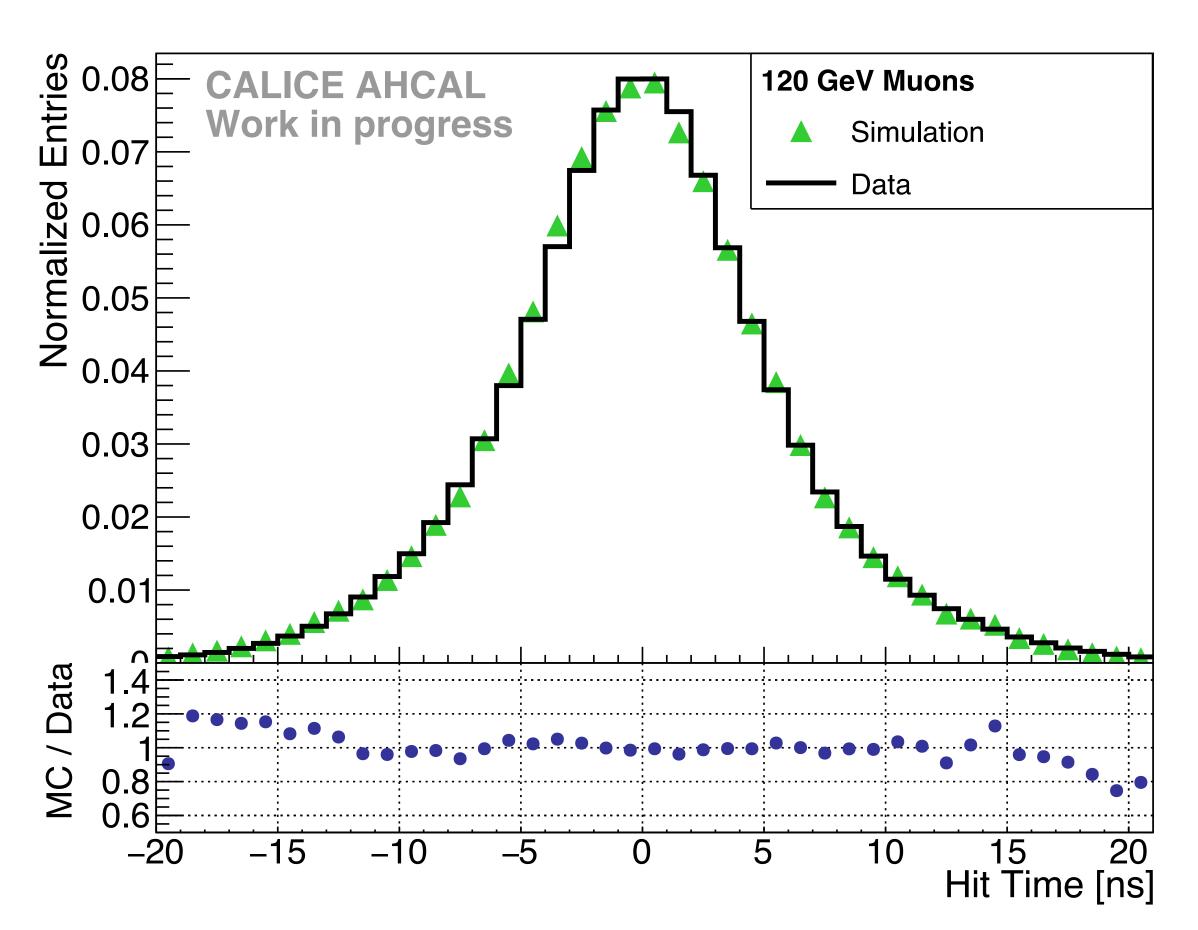

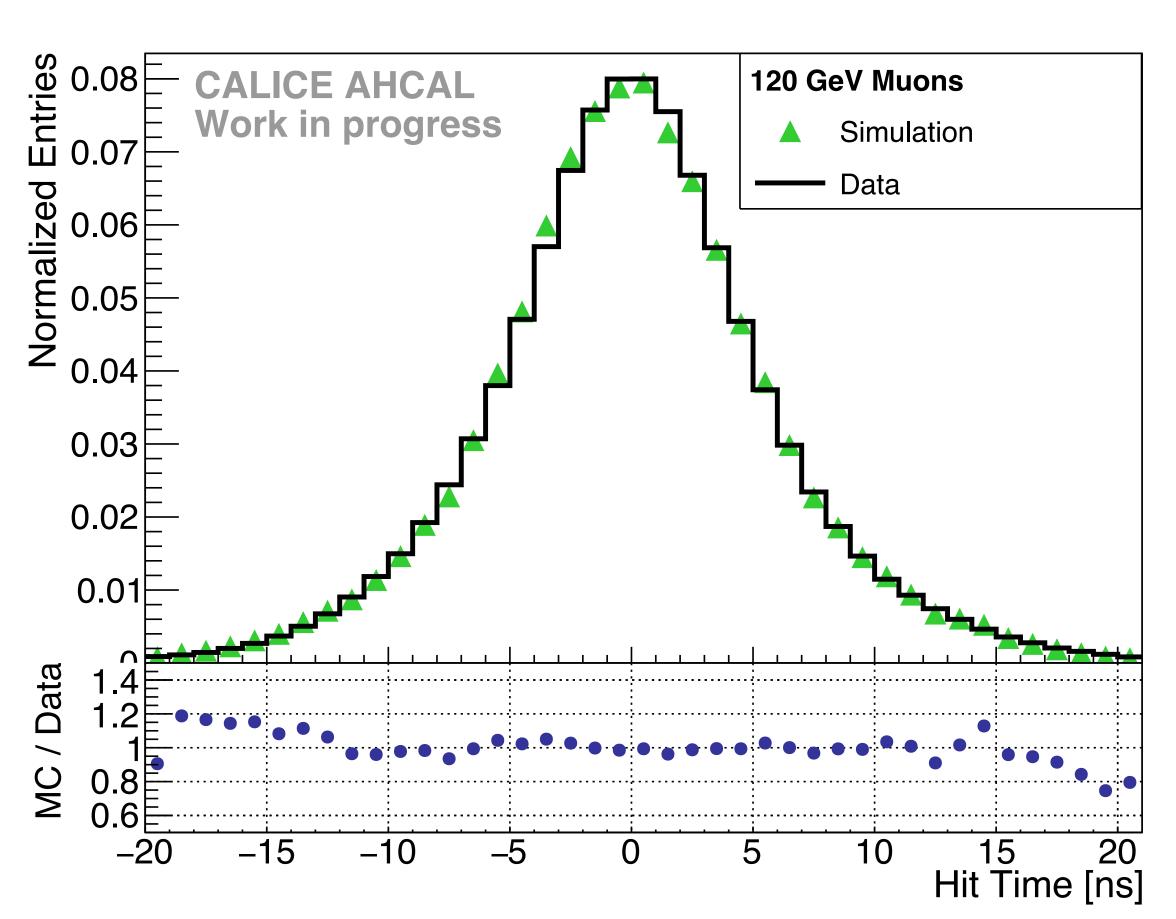

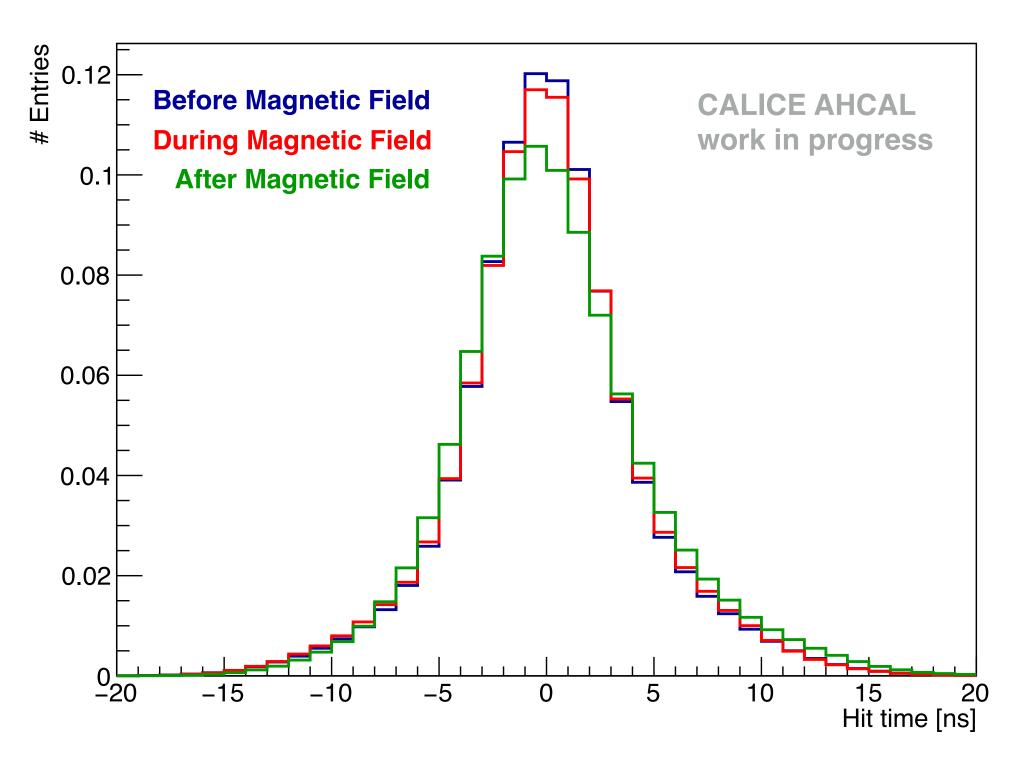

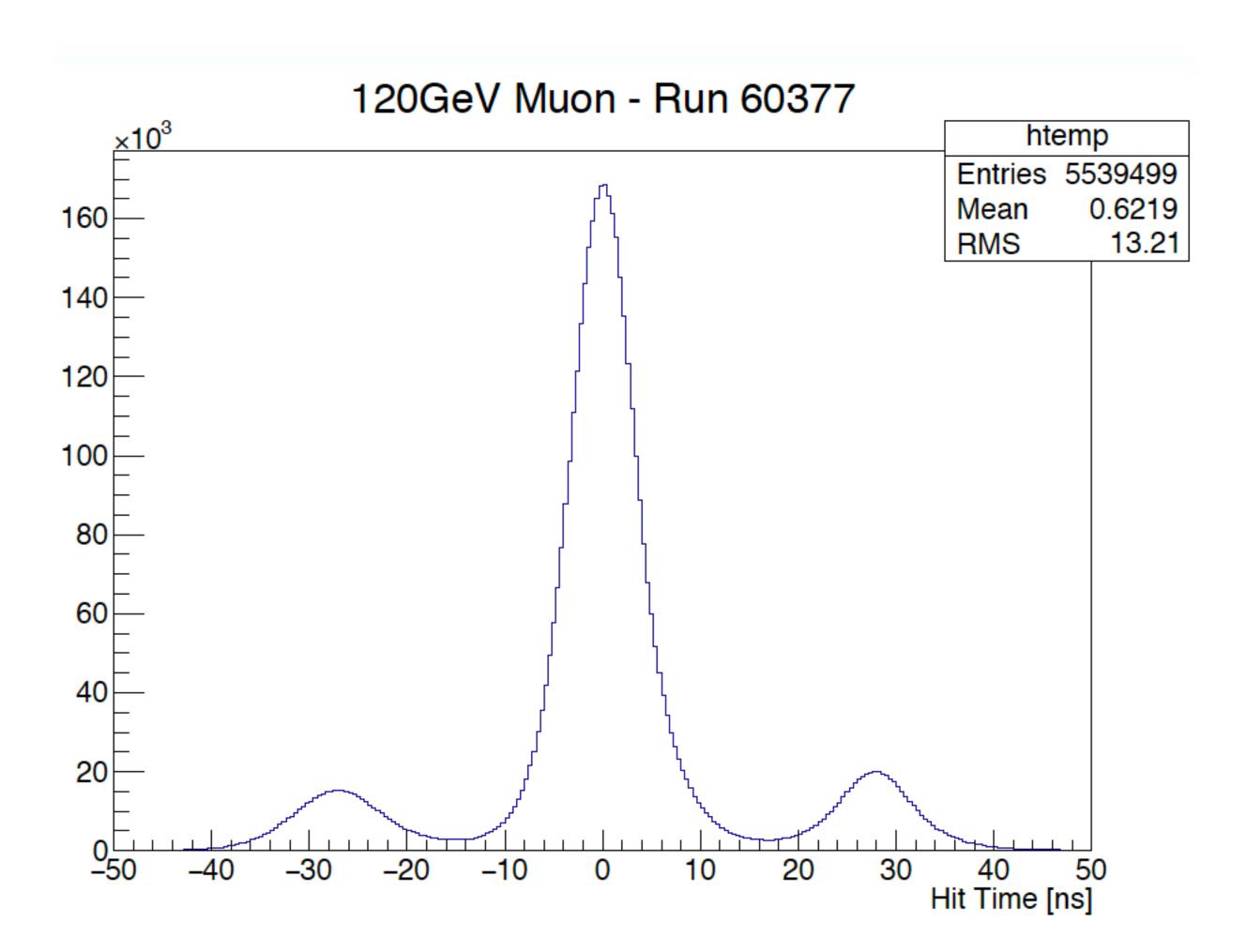

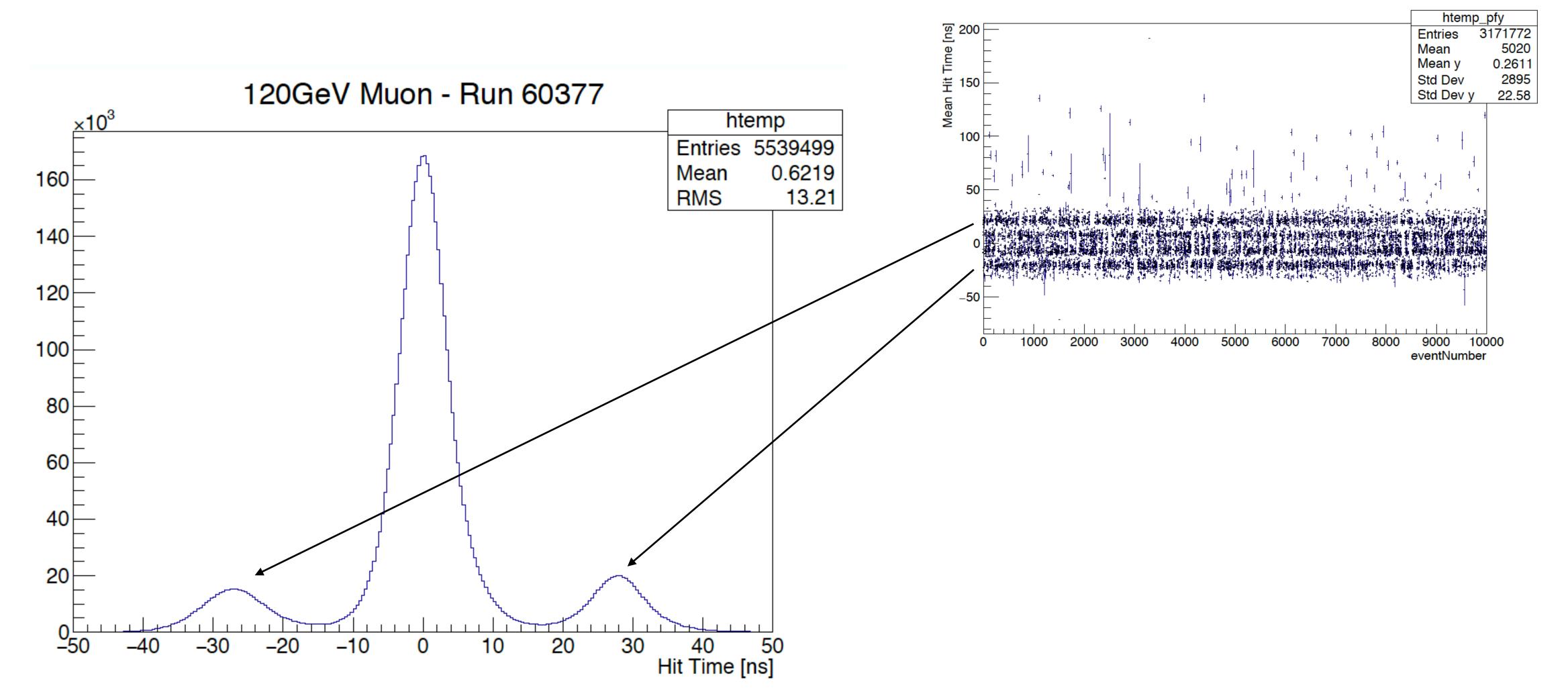

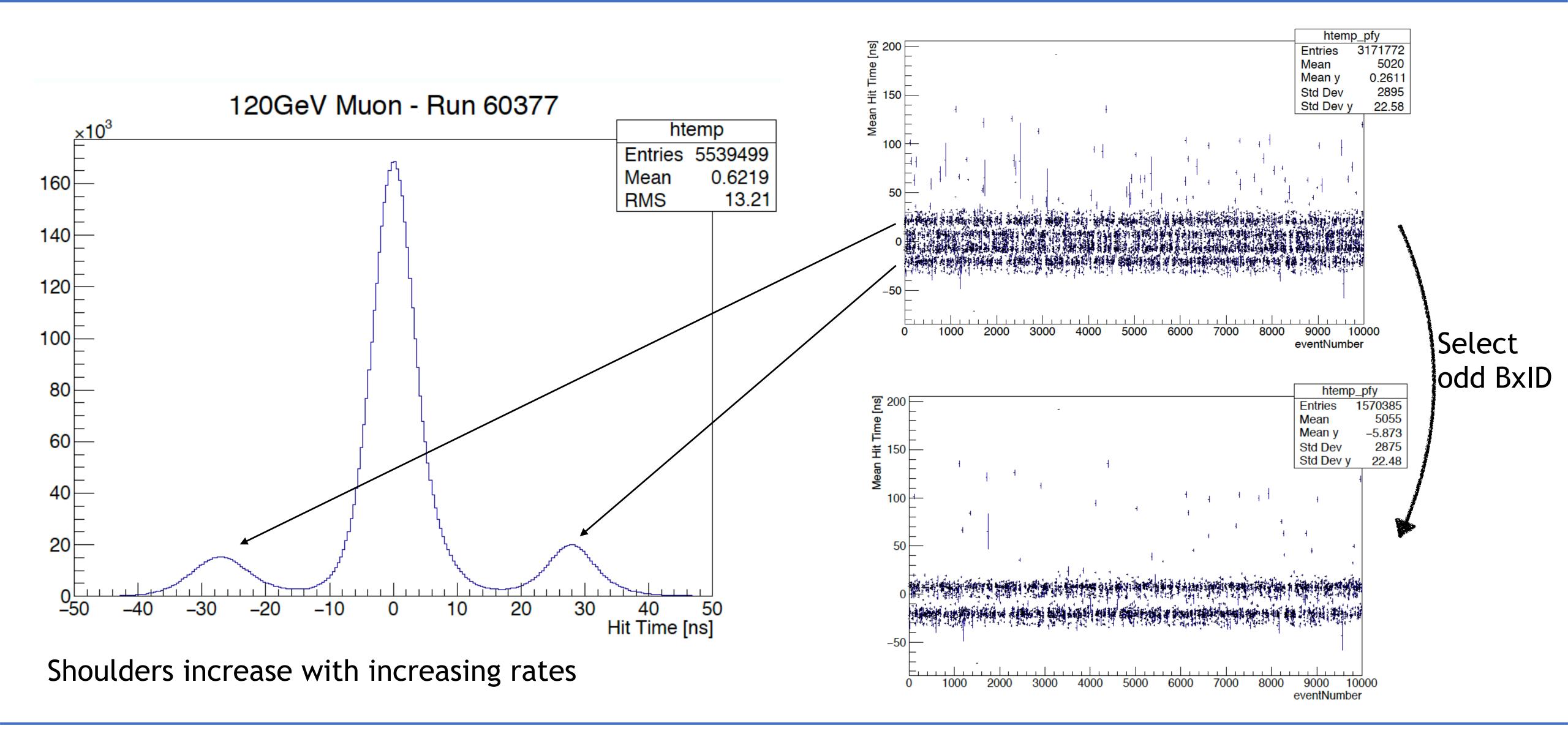

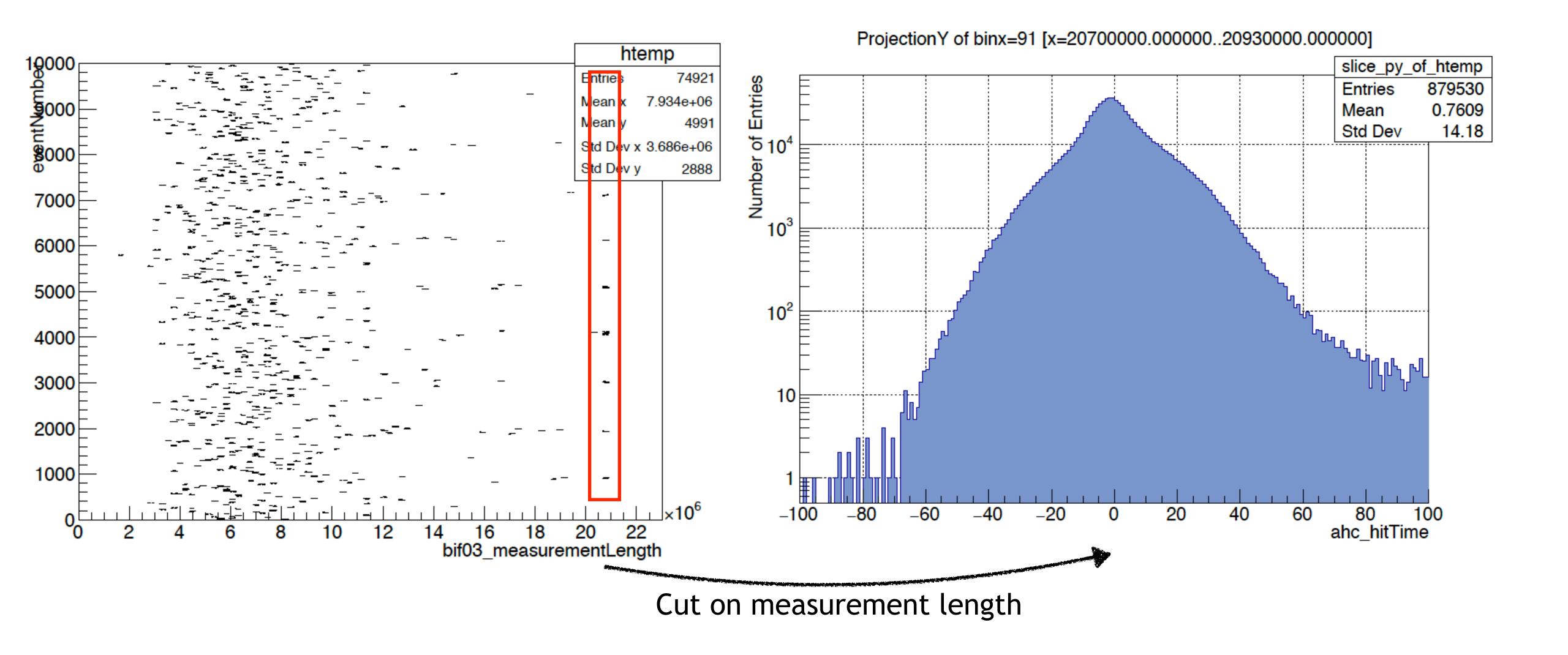

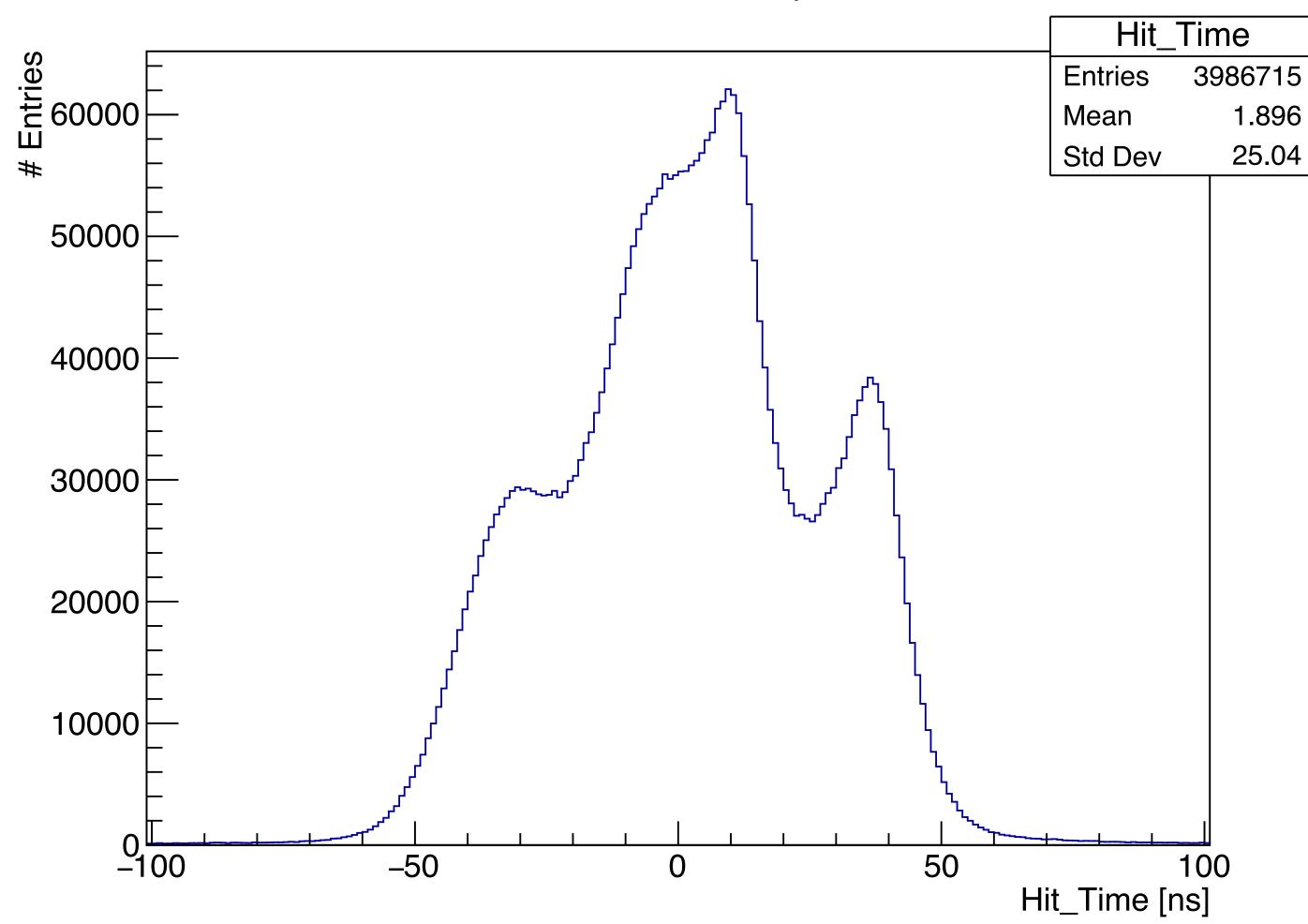

## Muon Time Resolution - May 2018

## Muon Time Resolution - May 2018

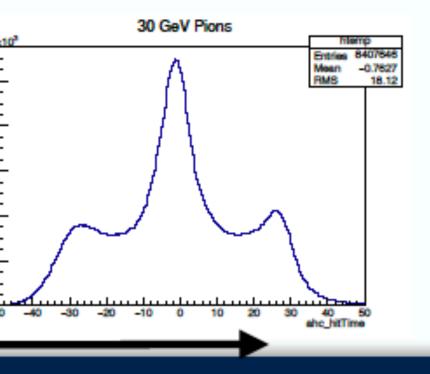

Shoulders increase with increasing rates

### Muon Time Resolution - May 2018

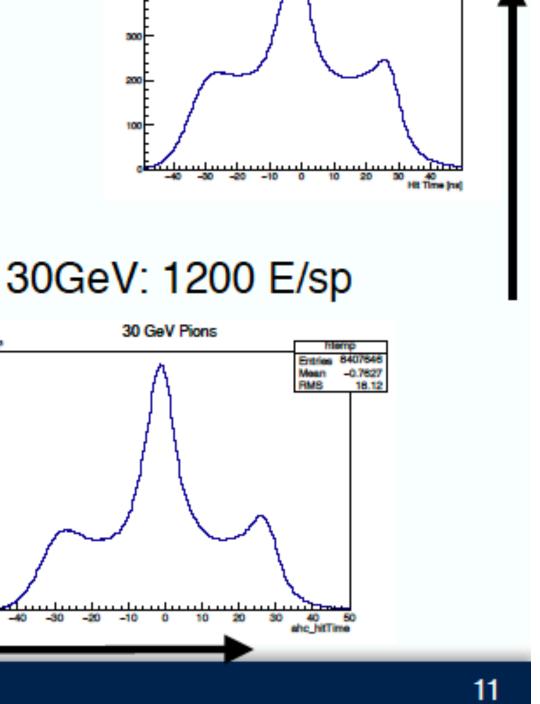

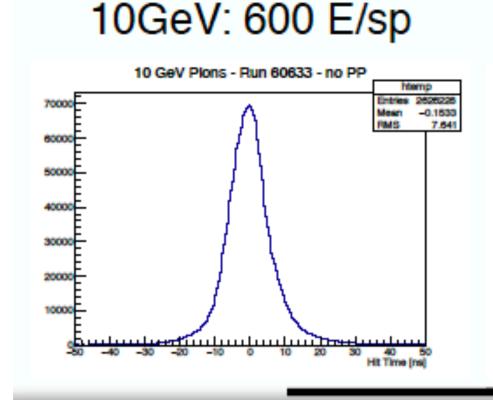

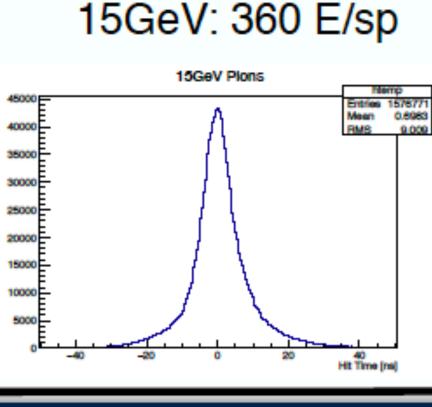

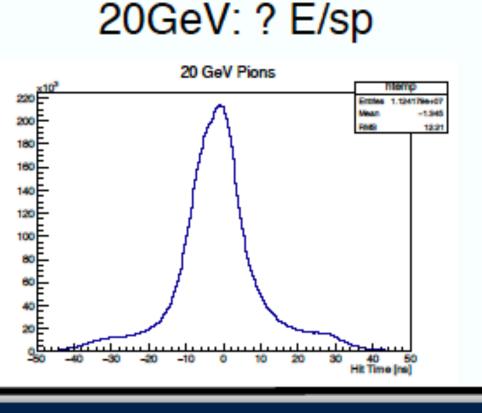

## Pion Time Resolution - May 2018

## Pion Time Resolution - May 2018

## Pion Time Resolution - May 2018

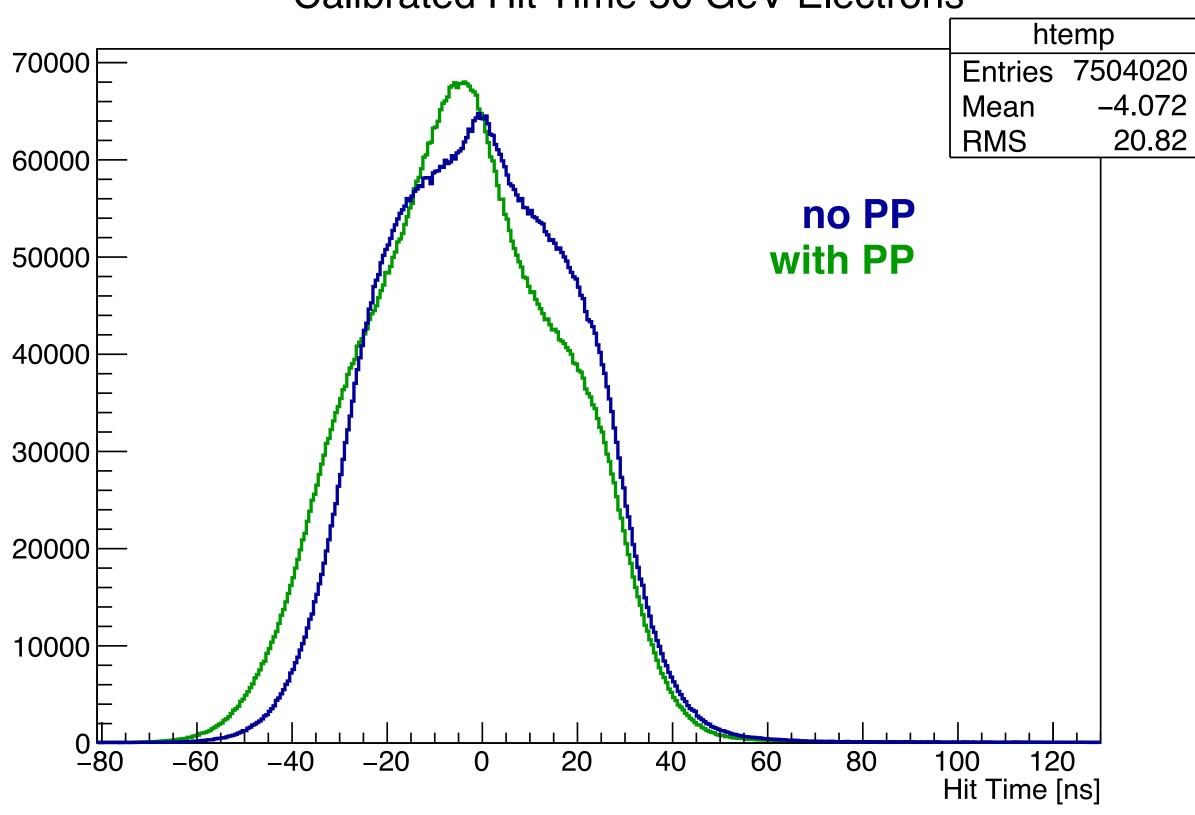

## Electron Time Resolution - May 2018

- Shoulders present in both modes

- PP shifts the peak to negative hit times

### Pion Time Resolution with PP - June 2018

Run 61375 - 30GeV Pions PP - June18 - May18 Calibration Constants

- Used time calibration from May 2018

- Done without PP

- Tailcatcher and Tokyo module excluded

- Reasonable distribution

- With respect to shoulders

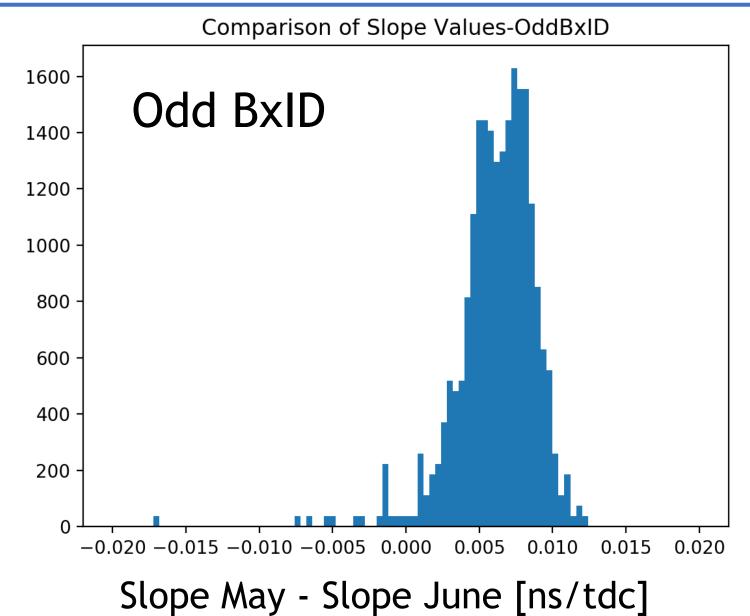

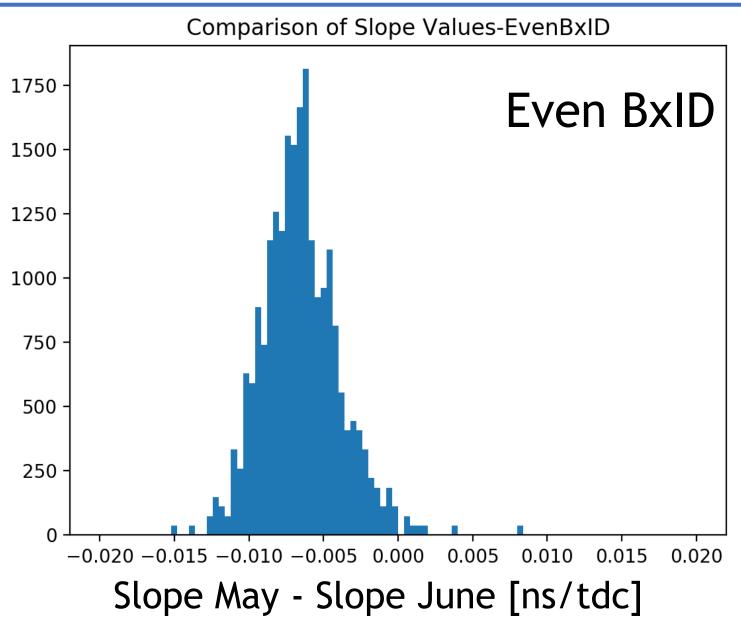

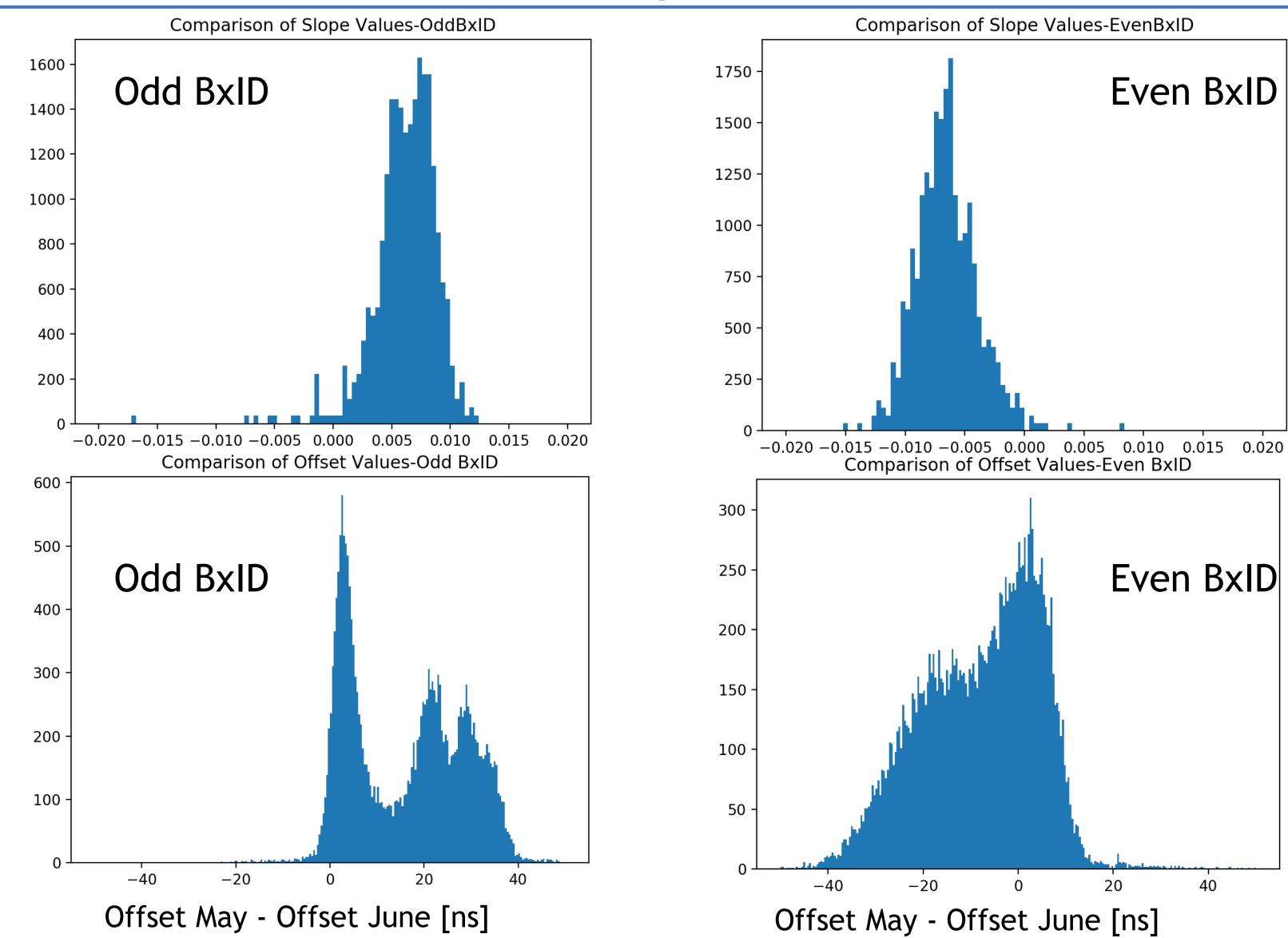

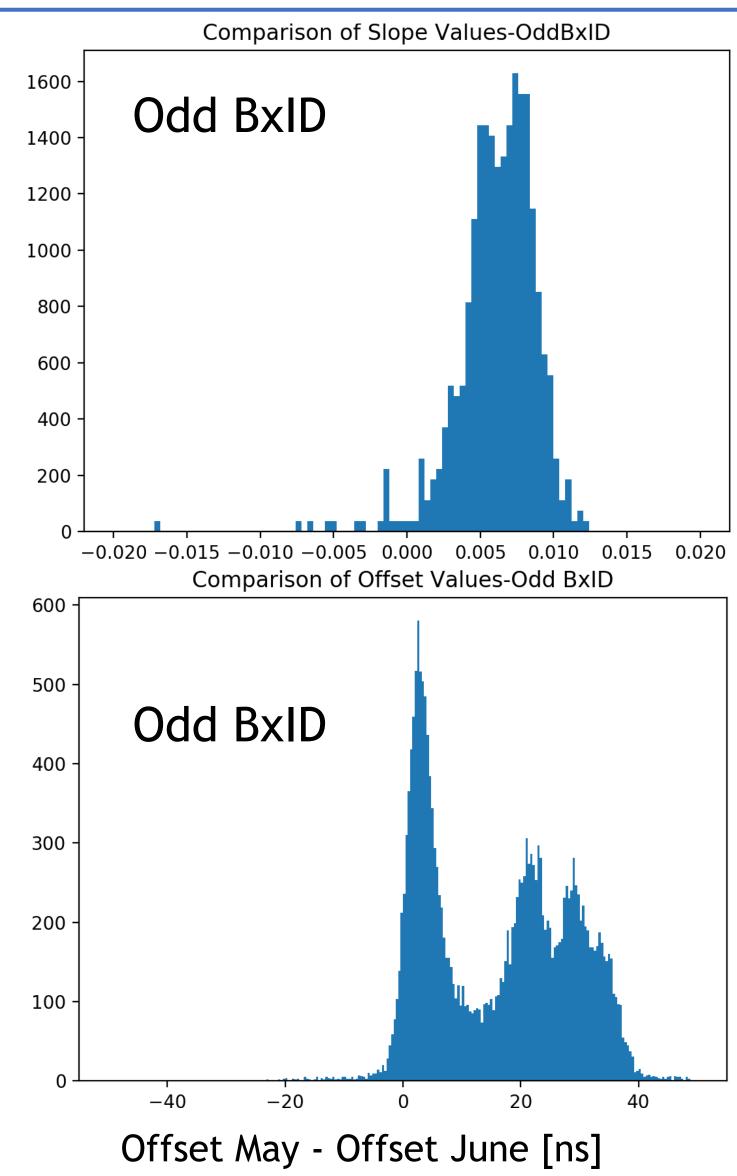

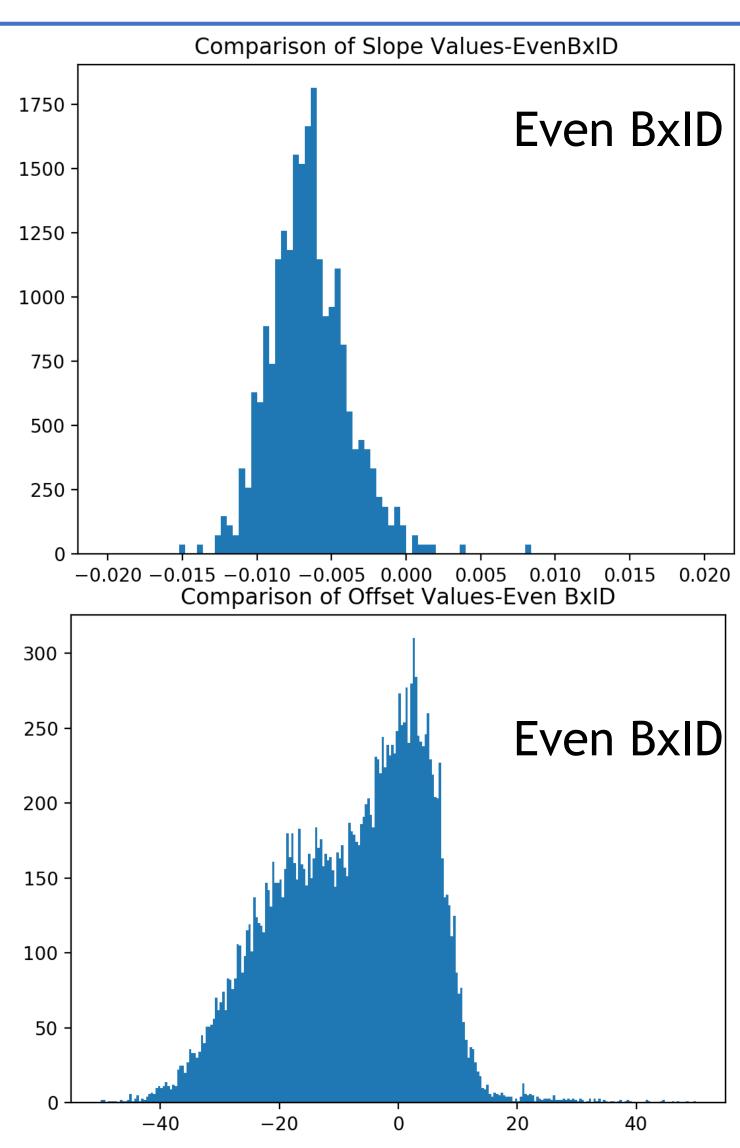

## Fit Parameters per Channel - May vs June

## Fit Parameters per Channel - May vs June

24

### Fit Parameters per Channel - May vs June

- May calibration done <u>without</u> power pulsing

- June calibration done <u>with</u> power pulsing

May translate the comparison to PP vs No-PP

Offset May - Offset June [ns]

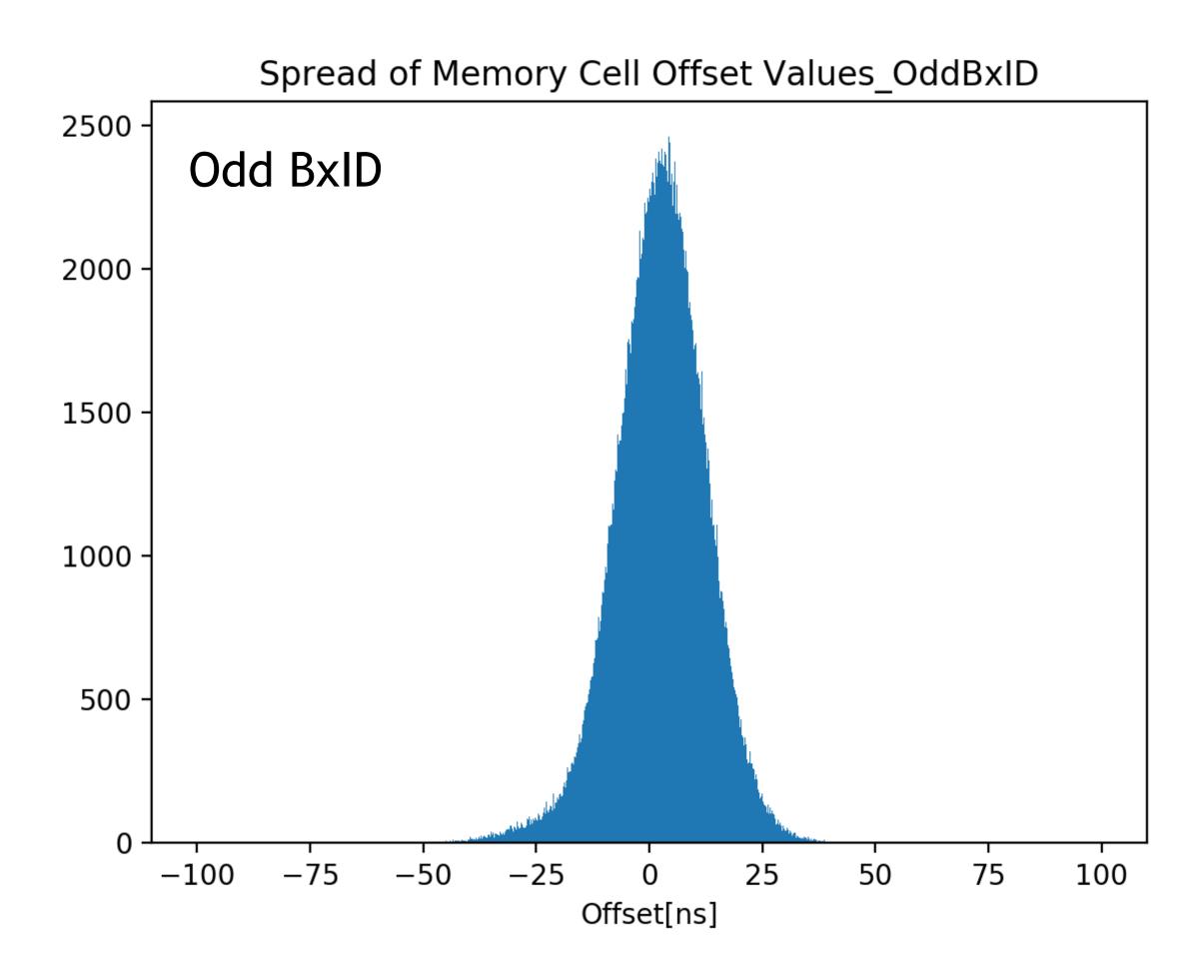

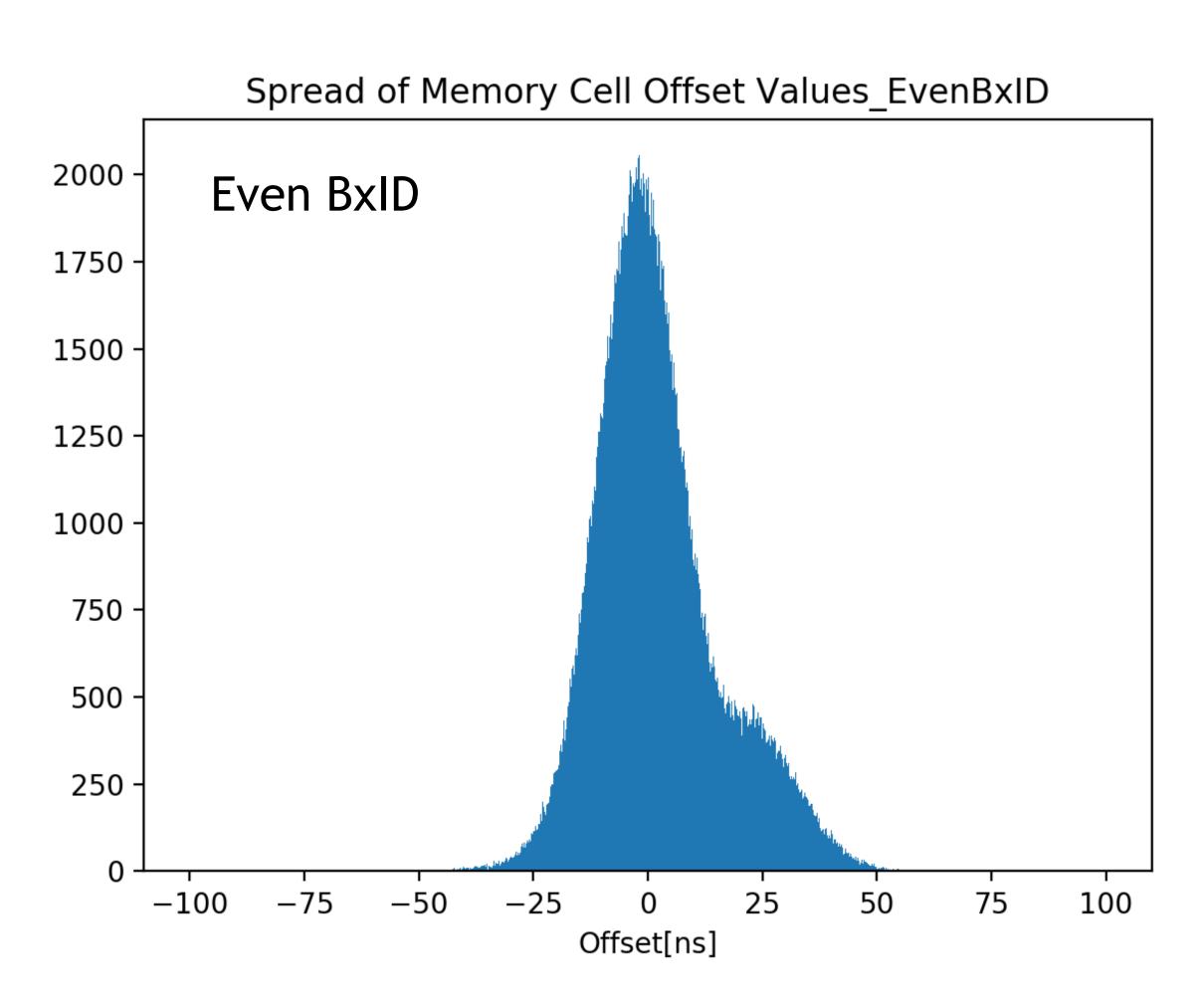

## Spread of Memory Cell Offset - May 2018

~16% non-calibrated

~19.5% non-calibrated

### To do's

#### By (proposed) priority:

- 1. Identify reason for shoulders in time resolution and try to reject/recover

- 2. Add database entries for time walk correction, non-linearity and Memory cell offset

- 3. Implement time walk and non-linearity correction as Marlin processor

- 4. Investigate difference between PP and No-PP

- 5. Investigate failure of robust fit

### Backup

#### Time Calibration

#### **Implementation**

- Implemented as marlin processor

- Calibration working for TDC ramp slopes and offsets between channels

- Time walk correction and non-linearity correction missing

- —> Current time resolution ~6-7ns (no quality cuts)

#### **Performance**

- Fits need to be done with per mille precision

- ~100 hits per memory cell needed (min. 30)

- ~370k memory cells

- 10'000 fits take about 5min. Calibration should be feasible within few hours

- Adds few ns to resolution if we don't have all memory cells calibrated

**Christian Graf**

Test Beam Readiness Review - April '18

8

### Backup

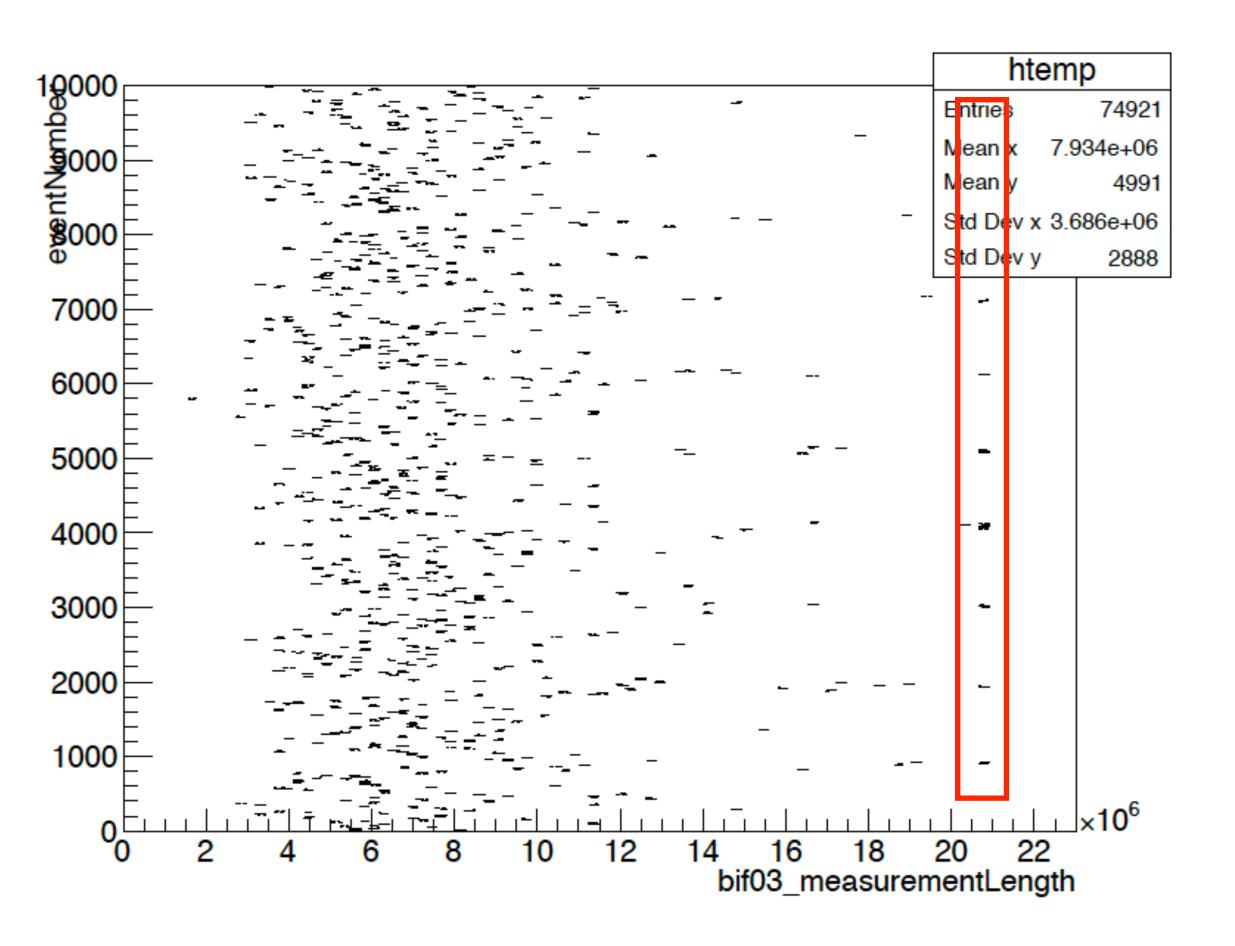

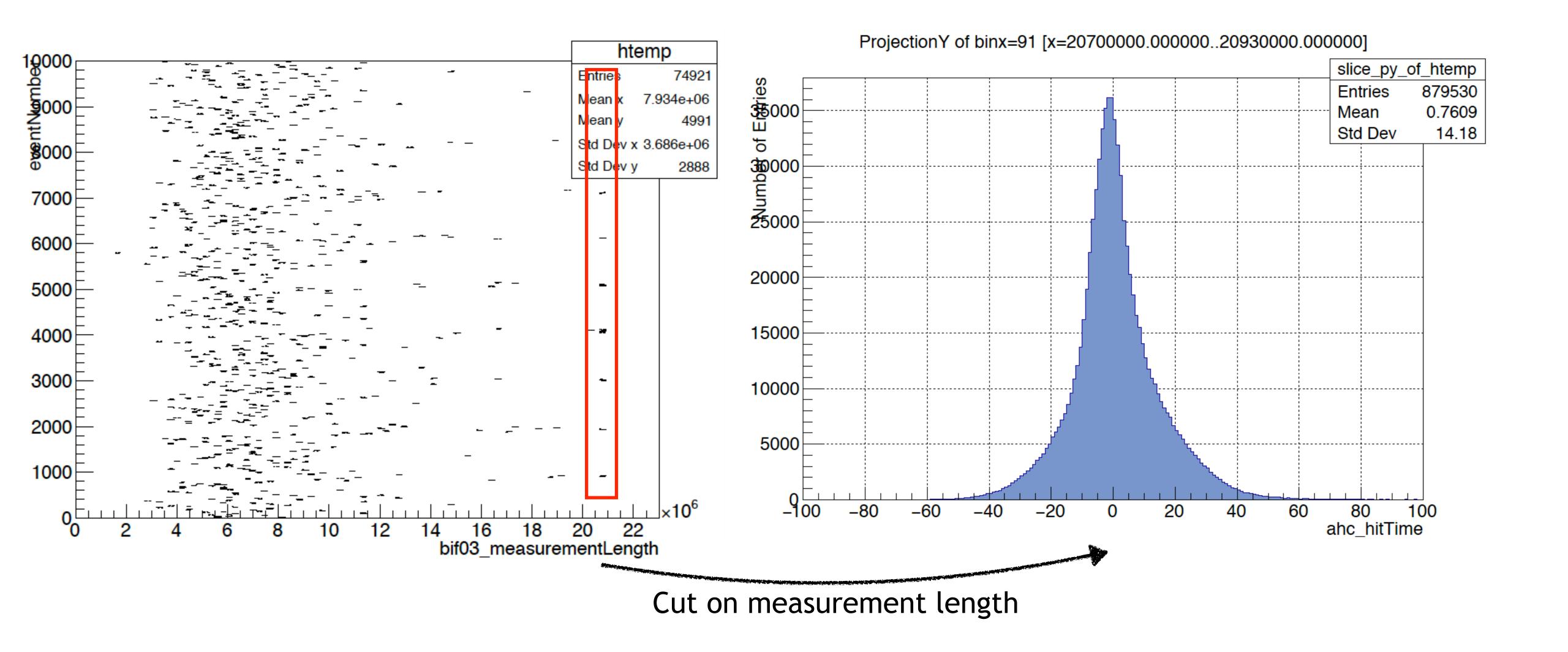

### Higher Rates

- 10GeV give nice time resolution

- Shoulders problem increases for increasing rate

- From first look: There does not seem to be a problem for high chip occupancies (at least not as severe as in 2015)

60GeV: 1100 E/sp

**Christian Graf**

Group Meeting - 13.06.2018

Lorenz Emberger