# HG/LG Inter-Calibration

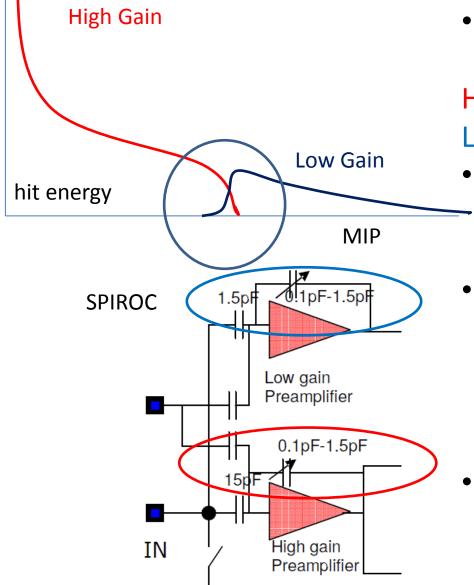

- SPIROC2B/2E has 2 signal output lines. High Gain and Low Gain

HG -- small deposited energy hits

LG -- large deposited energy hits

- In principle, IC factor is constant

and just depends on ratio of capacitors. (IC ~20 for TB 2018)

- But IC factor is different for each channel due to an uneven quality of capacitance and parasitic capacitance.

$\rightarrow$  measurement is important

After inter-calibration, HG and LG output of hit energy should be connected smoothly <sup>2</sup>

## Methods to extract IC factor

#### LED runs

- slope of HG\_ADC vs LG\_ADC

- $\Delta HG_ADC / \Delta LG_ADC$

#### Challenges

- Pedestal shift

- linear range selection

- IC factor extraction with beam runs

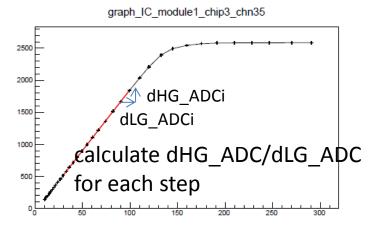

# IC factor from LED runs dHG\_ADC/dLG\_ADC

• Small LED V step is required to cancel out or reduce impact of pedestal shift.

$\Delta$ Light yield \* HG = (HG\_ADC<sub>i+1</sub> - HG\_ADC<sub>i</sub>)  $\Delta$ Light yield \* LG = (LG\_ADC<sub>i+1</sub> - LG\_ADC<sub>i</sub>)

$IC = HG/LG = (HG_ADC_{i+1} - HG_ADC_i)/(LG_ADC_{i+1} - LG_ADC_i)$

graph IC module1 chip3 chn35 constraints 2500 reasonably large signal  $HG_ADC_{i+1} - HG_ADC_i > 100$ 2000  $30 < LG_{ADC_{i+1}} - LG_{ADC_{ped}} < 100$ dHG ADCi 1500 dLG ADCi total amount of charge 1000 calculate dHG\_ADC/dLG\_ADC in a chip < 60000 500 for each step 100 150 200

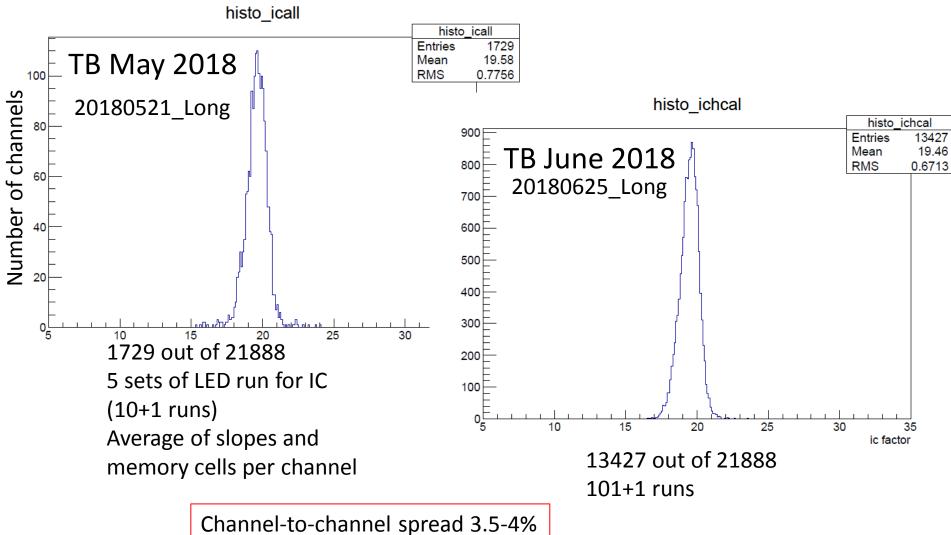

#### LED Run May and June 2018 LG1200

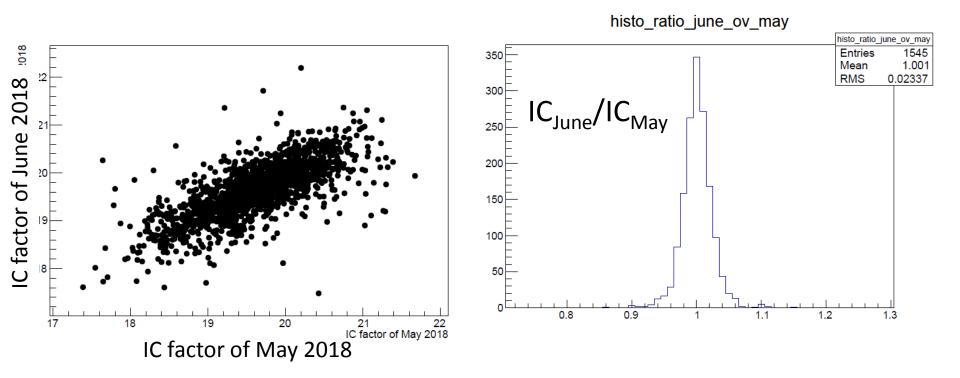

# Comparing IC factor of June and May 2018

after reject outliers: range of plots is mean  $\pm$  3xRMS of IC histogram

RMS of IC<sub>June</sub>/IC<sub>May</sub> is 2.3%, mean is 1.001  $\pm$  0.0006

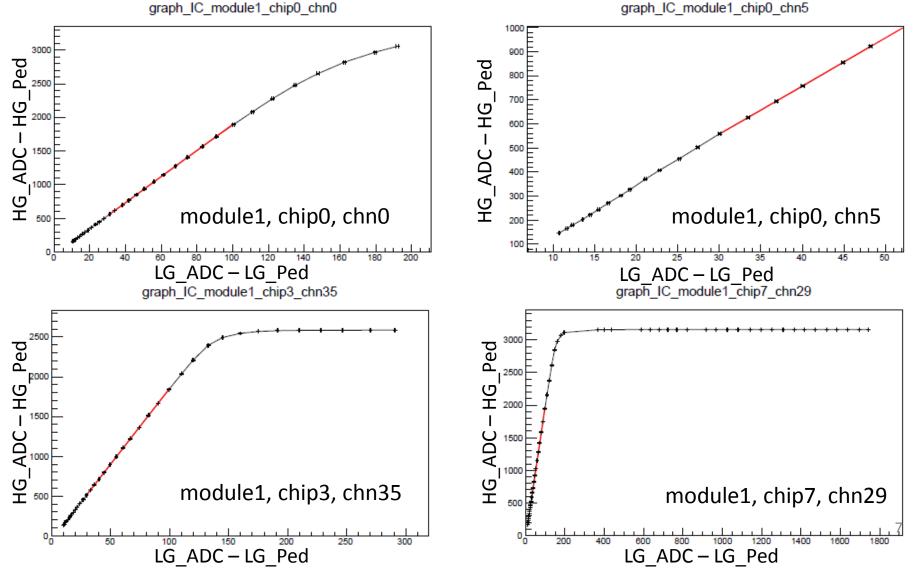

# Slope of HG vs LG

- after pedestal subtraction

- fitting range 30 < LG < 100

- total amount of charge in a chip < 60000 ADC (HG)

- at least 5 points in the fitting range

### Slope of HG vs LG

histo\_ic\_slope histo\_ic\_slope Entries 18364 18.87 Mean 1600 RMS 1.154 Underflow 0 1400 Number of channels Overflow 0 Integral 1.836e+04 1200 Tail suspected to be 1000 due to pedestal shift 800 in events with large total charge 600 (affects the dimmest 400 channels) 200 00 5 10 15 20 25 30

8

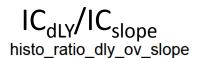

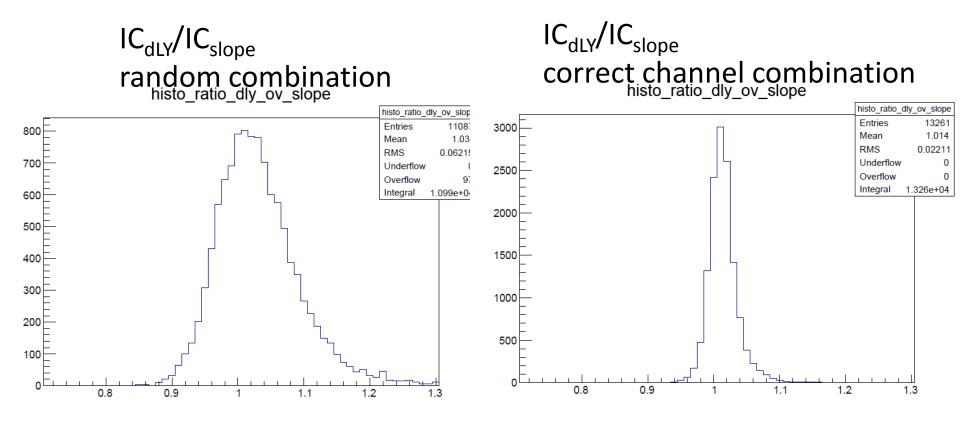

#### IC factor dLY vs Slope and IC<sub>dLY</sub>/IC<sub>slope</sub>

dLY vs Slope

- Mean of  $IC_{dLY}/IC_{slope}$  1.014  $\rightarrow$  1.4% systematic shift

- RMS = 0.022

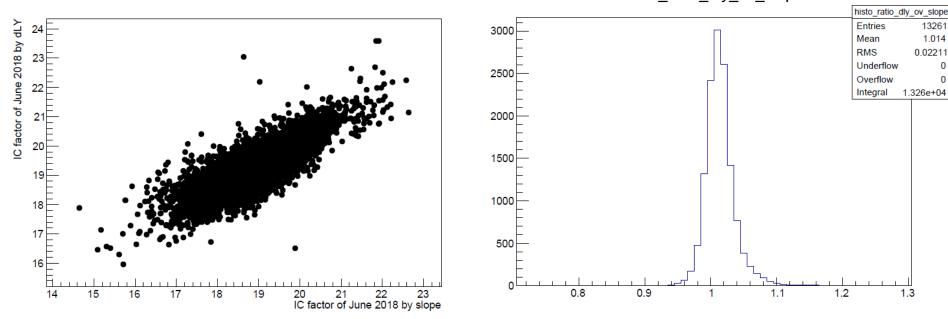

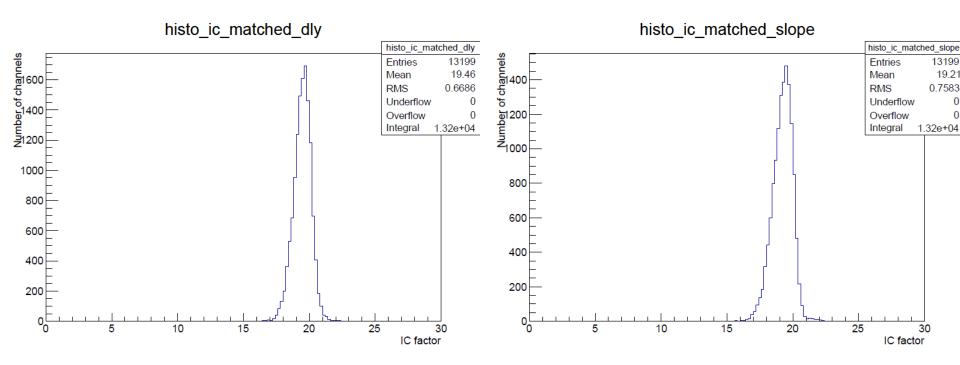

#### IC factor extracted by dLY and slope

fill IC values extracted by dLY within mean +/- 3\*rms of IC histogram of dLY

fill IC values extracted by slope within mean +/- 3\*rms of IC histogram of slope, if the IC values are not filled by first step.

10

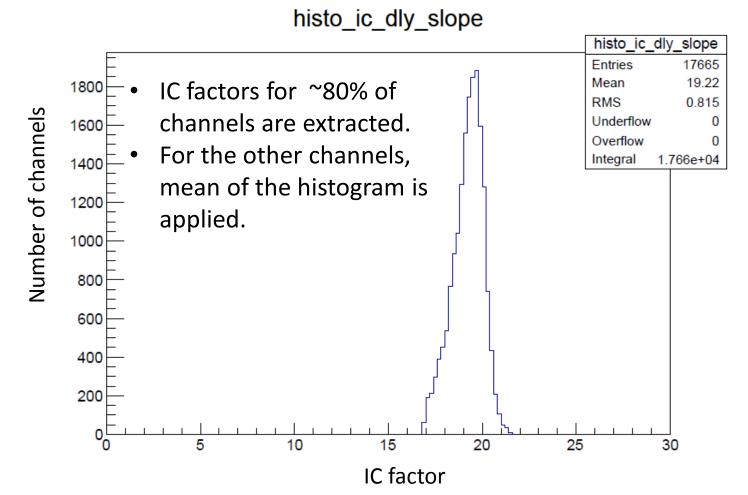

### Muon Run with IC mode (HG/LG) Pedestal shift with hit?

AT run is not available to extract the IC factor due to a pedestal shift. But this information is useful to correct the low gain pedestal.

• IC factor is obtained from LED runs (ETIC)

$\rightarrow$  Pedestal\_LG = (Peak\_LG with hit) – (expected MIP\_LG)

(expected MIP\_LG) = MIP\_HG/F<sub>IC</sub>

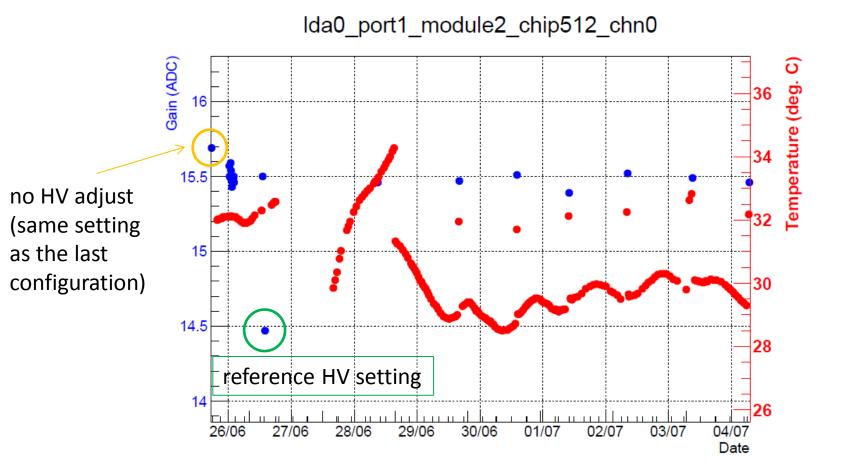

#### Gain Stability During TB

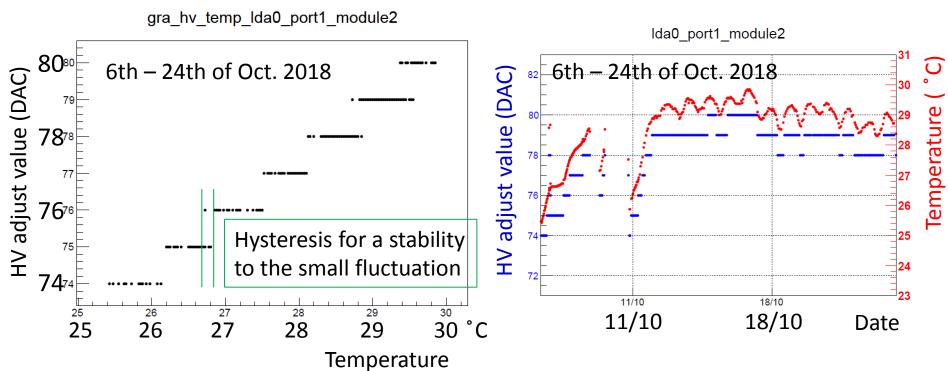

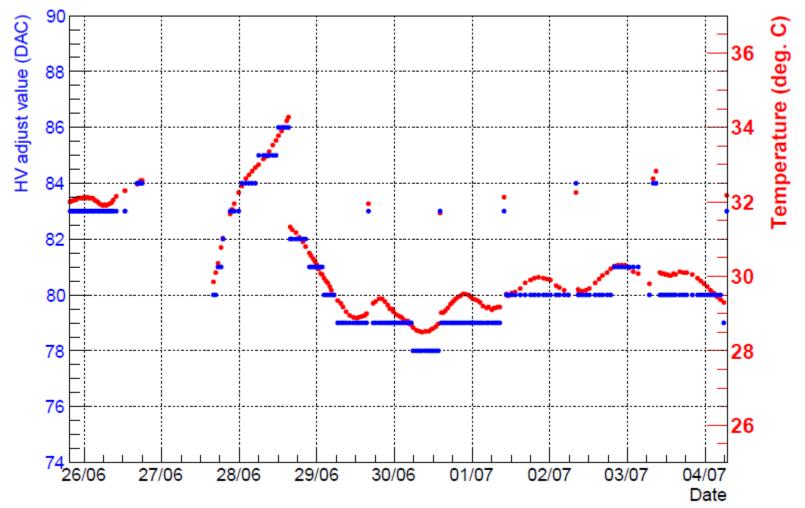

### HV Adjustment HV Adjust Value and Temperature vs Time

- Automatic HV adjustment on power board successfully works for Vop correction against temperature changes.

- Routinely running for TB in 2018

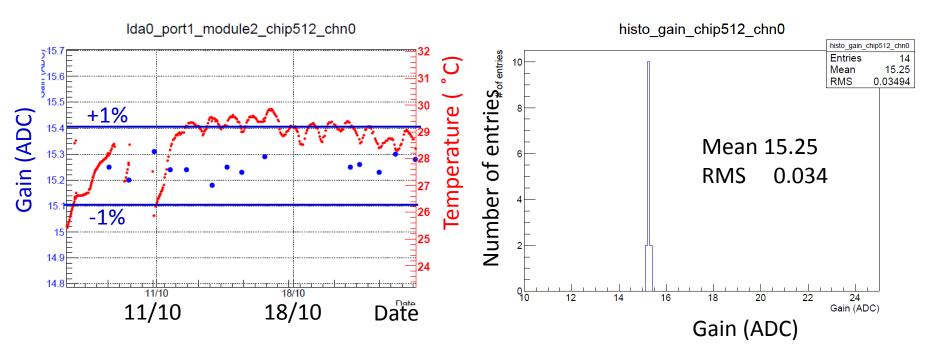

#### Gain Stability

#### Gain and Temperature vs Time

- Gain of MPPCs are successfully stabilized by automatic HV adjustment

- Dispersion of gain is within a precision of gain extraction by multi Gaussian fitting (<1%)</li>

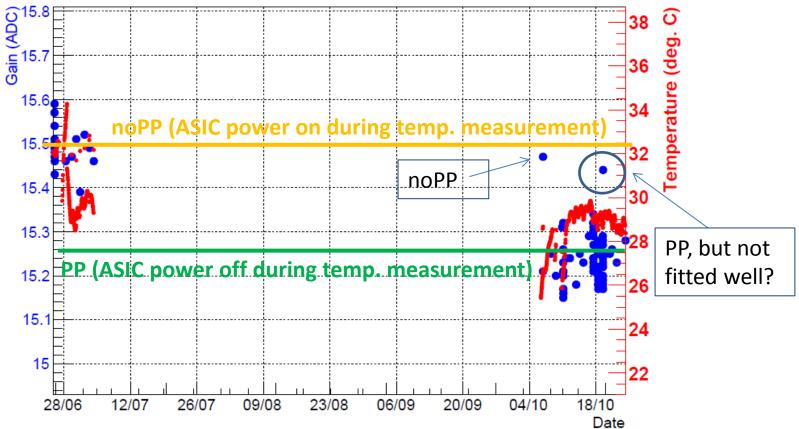

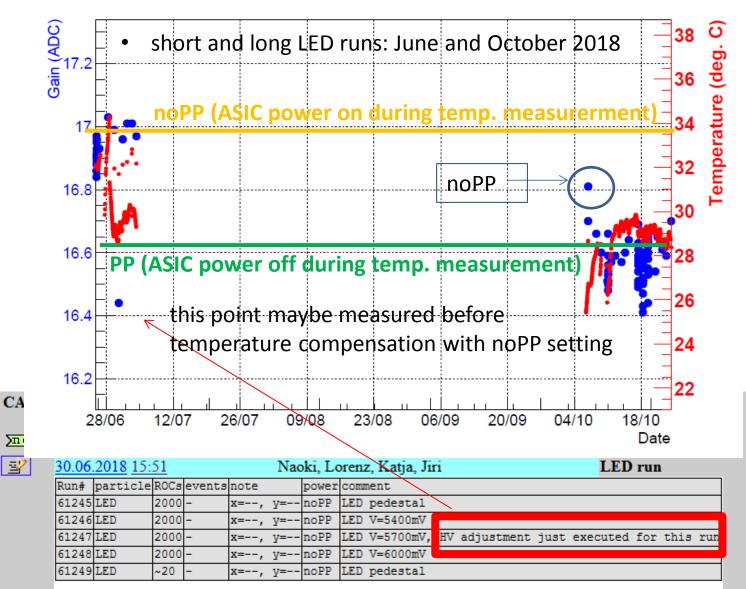

#### Gain Stability Gain and Temperature vs Time

• short and long LED runs: June and October 2018

lda0\_port1\_module2\_chip512\_chn0

# Summary

- HG/LG IC factor ~ 19.2

- Mean of  $IC_{June}/IC_{May} = 1$ , RMS ~2.3%

- no significant difference between slope and dLY methods

- IC factor is extracted for 17665 channels by 2 methods

- Automatic adjustment of common bias voltage to compensate for temperature changes  $\rightarrow$  stable gain within less than  $\pm$  1%

To do

• apply higher order correction for slope

#### Backup

### **Gain Stability**

Ida0\_port1\_module2\_chip517\_chn0

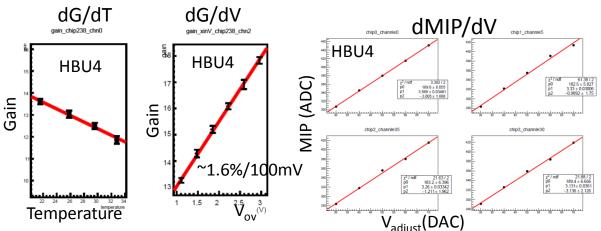

#### Temperature Compensation for MPPC

MPPC gain depends on temperature. Because breakdown voltage depends on temperature. Gain ∝ V<sub>ov</sub>

complete discussion of temperature dependence on gain by HPK. https://hub.hamamatsu.com/sp/hc/resources/Temperature\_Gain\_SiPM.pdf

- Gain  $\propto V_{ov}$  $V_{ov} = V_{bias} - V_{break down}$

- We want to keep V<sub>ov</sub> same as a value at a reference point. Adjust bias voltage against temperature changes.

→Automatic HV adjustment

- HPK S13360-1325

- dMIP/dV is ~1.1%/DAC (1 DAC ~ 37mV)

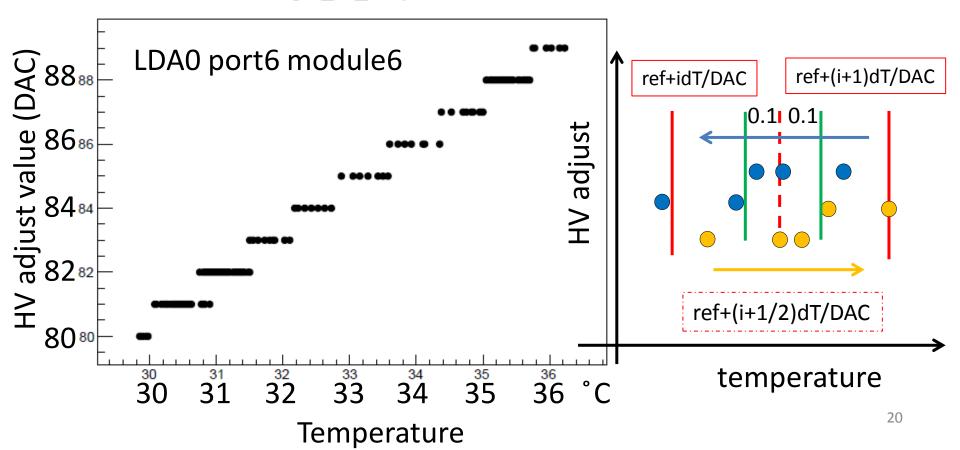

# HV adjust vs Temperature

- 28th of June 4th of July 2018

- There are over-lap of 0.2 degree C due to a hysteresis for stabilization around borders of temperature gra\_hv\_temp

#### HV adjust value and Temperature vs Time

lda0\_port1\_module2

21

#### Gain and Temperature vs Time

- Automatic HV adjustment on power board successfully works for the temperature compensation.

- Automatic HV adjustment is included in DAQ chain for TB in 2018. 22

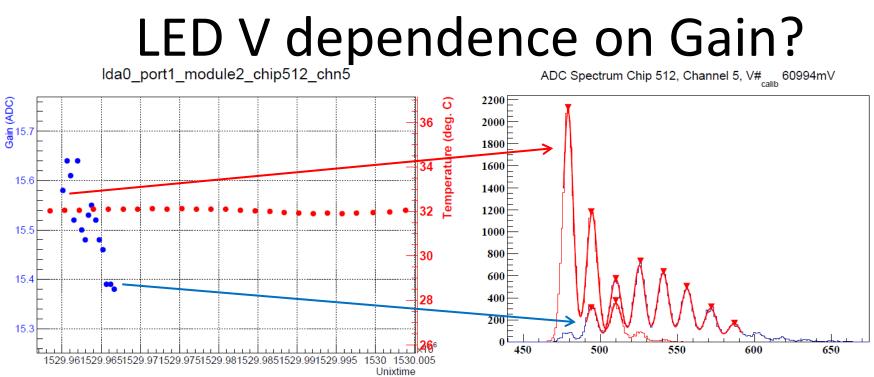

- Is there LED V (total amount of charge) dependence of Gain?

- same trend on many channels

- SPS looks O.K. for the first and the last measurement of point.

peak has a tail on lower side

- ightarrow later peaks affected by after pulsing

- ightarrow dependence on number of peaks

- $\rightarrow$  Systematic shift caused by a fitting method?

# IC factor from LED runs dHG\_ADC/dLG\_ADC

$\Delta Ligit yield * HG = (HG_ADC_{i+1} - HG_ADC_i)$  $\Delta Ligit yield * LG = (LG_ADC_{i+1} - LG_ADC_i)$

$IC = HG/LG = (HG_ADC_{i+1} - HG_ADC_i)/(LG_ADC_{i+1} - LG_ADC_i)$

constraints

- HG\_ADC<sub>i</sub> > HG\_ADC<sub>ped</sub>

- $HG\_ADC_i$  and  $HG\_ADC_{i+1} > 10$

- $HG\_ADC_i$  and  $HG\_ADC_{i+1} < 1500$

- $30 < LG_{ADC_{i+1}} LG_{ADC_{ped}} < 100$

- total amount of charge in a chip < 60000</li>

- $HG\_ADC_{i+1} HG\_ADC_i > 100$

- $HG_RMS_{i+1}$ - $HG_RMS_i$  >0

- LG\_RMS<sub>i+1</sub>-LG\_RMS<sub>i</sub> >0

# IC factor dLY and slope $0.9 < IC_{dLY}/Ic_{slope} < 1.1$

# IC factor dLY vs Slope and IC<sub>dLY</sub>/IC<sub>slope</sub>

- RMS of  $IC_{dLY}/IC_{slope}$  with random combination ~6%

- channel by channel variation ~6%