### Facing the challenges:

- 5 bunch trains per second (5 Hz)

- 3000 bunches within one train

- one bunch every 300 ns, 150 ns possible

- each bunch to be registered

- high dynamic range (better 1:10k)

- more than 10k channels, depending on design

- Fast, low power, rad hardness to be considered

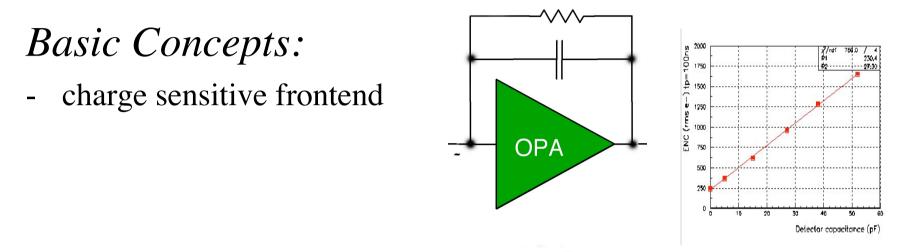

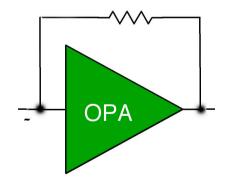

- current sensitive frontend

#### Dynamic Range:

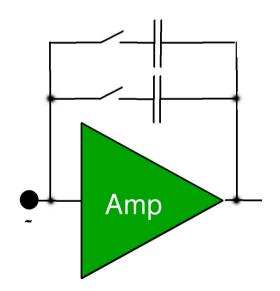

- operation with two (more) scales:

### Analog or Digital Storage:

- 3000 bunches within one train

- one bunch every 300 ns, 150 ns possible

- $\rightarrow$  analog storage nearly impossible

- (depth, decay of charge, switching noise)

- $\rightarrow$  Digitization with ADC, staggering?

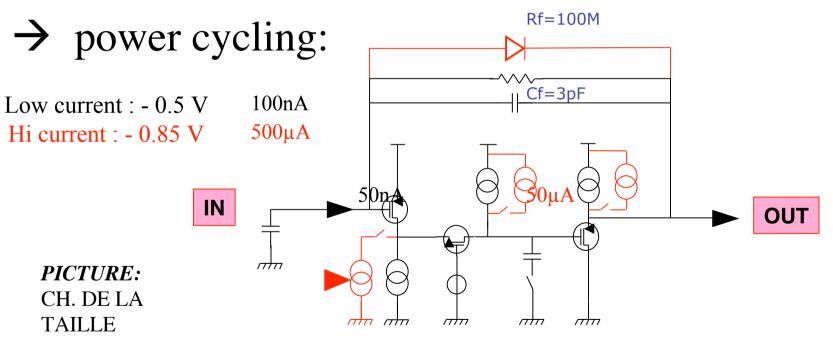

#### Power Consumption:

- more than 10k channels, depending on design

#### The Way To Go:

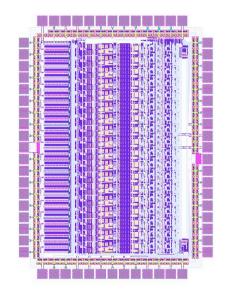

- Integrated solution after testing concepts

#### The Price To Be Payed:

- About 5 man-years + (electronics engineer)

- Several chip submissions (collaboration?)

- And, and, and

Next Steps:

- Investigation of preamp principles

- Feasibility studies of digitization

- Investigation of known r/o systems

(FLC Calice (Orsay))

- developing and refining of building blocks