### Timing Analysis and Correction for Chip Effects

Lorenz Emberger

CALICE Collaboration Meeting

Utrecht

12.4.2019

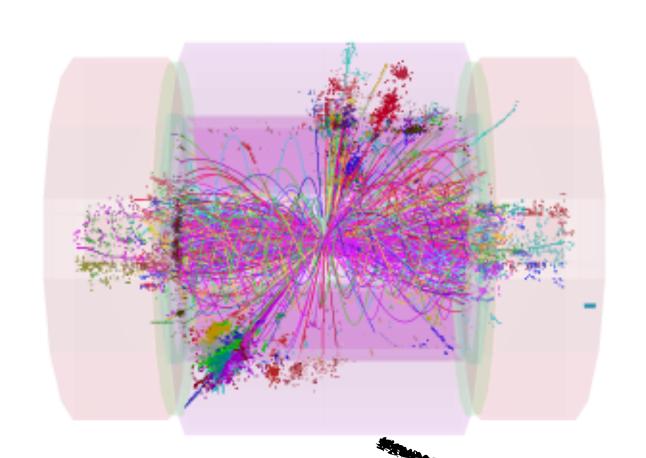

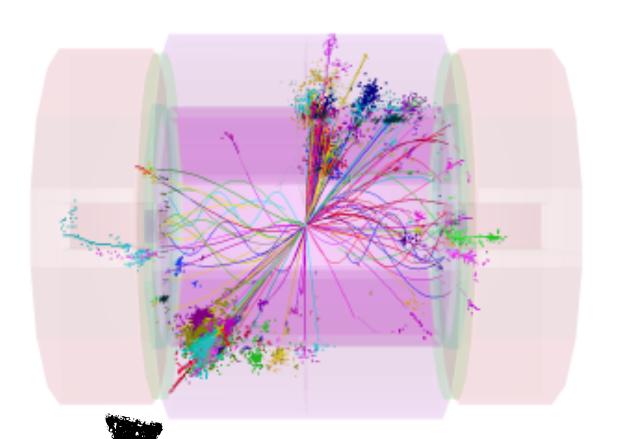

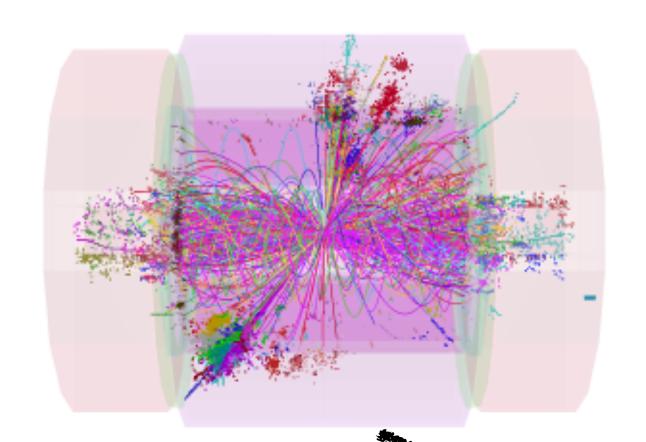

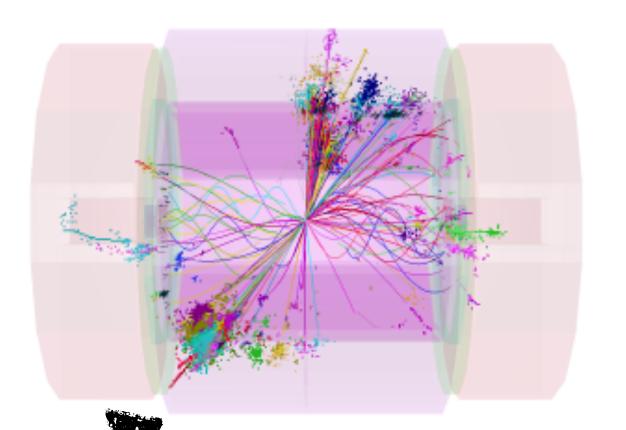

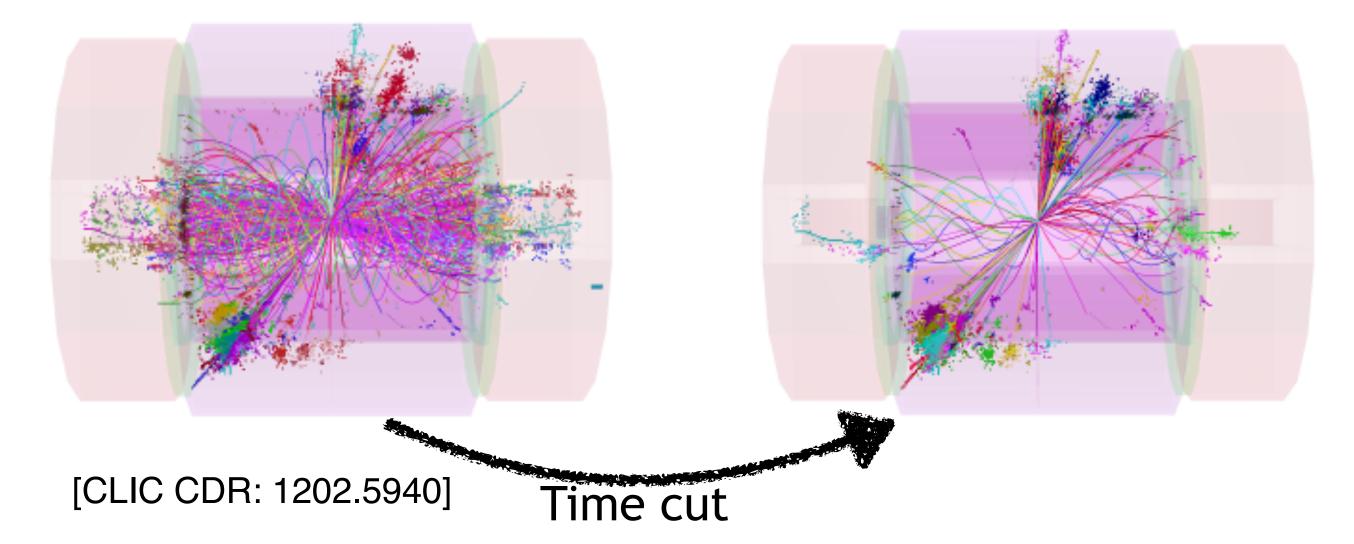

Why do we need time information?

Reject background

[CLIC CDR: 1202.5940]

Time cut

#### Why do we need time information?

- Reject background

- Improve clustering

[CLIC CDR: 1202.5940]

Time cut

#### Why do we need time information?

- Reject background

- Improve clustering

- Use in software compensation to identify components of hadronic showers?

Absorber ~10ns to 50ns

Instant

Instant

Instant

> 50ns

Scint. EM HAD (rel.) Neutrom inelastic Neutron elastic Neutron capture

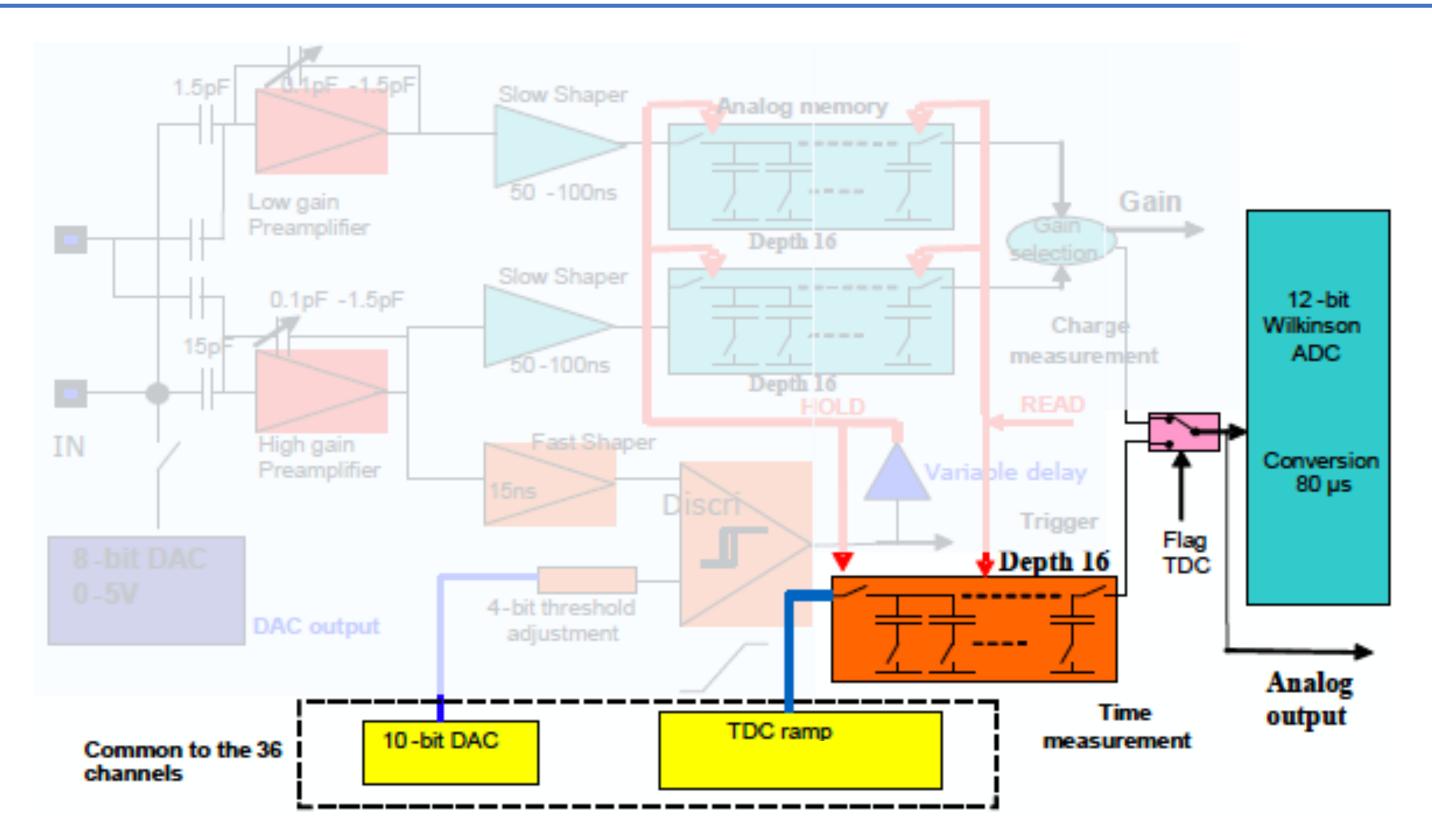

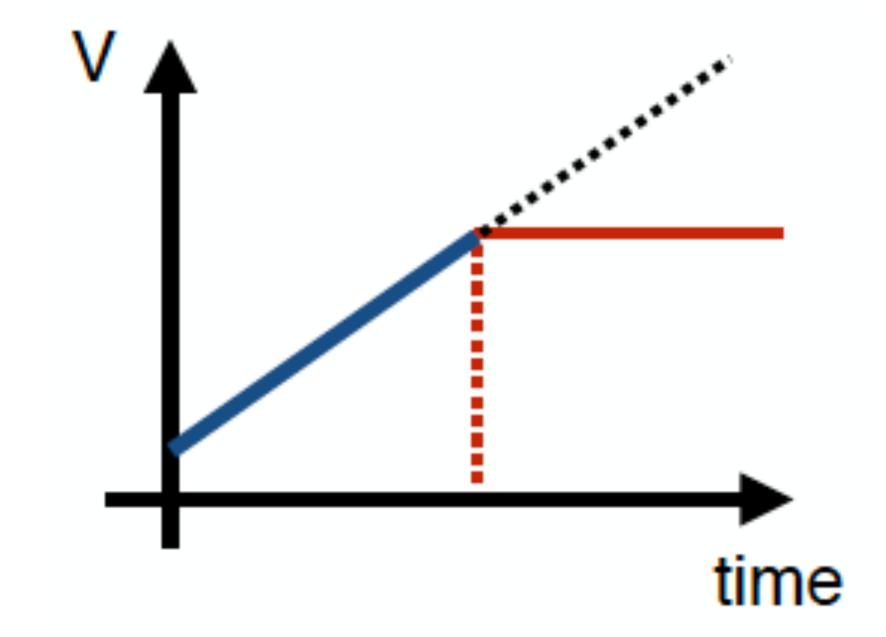

Time measurement with Spiroc2E: TDC (time to digital converter)

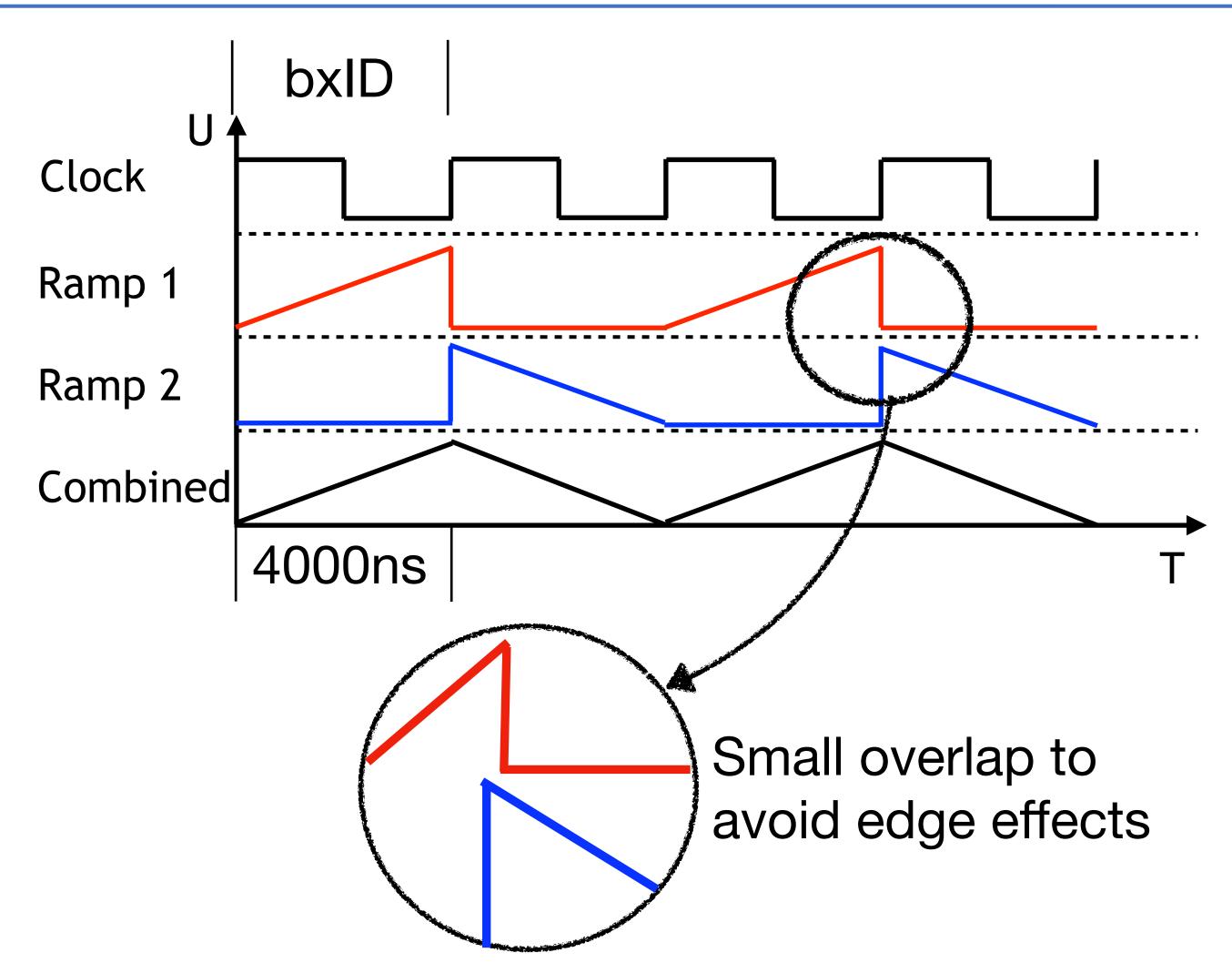

1. Common BIF clock with ~1ns bins

Time measurement with Spiroc2E: TDC (time to digital converter)

- 1. Common BIF clock with ~1ns bins

- 2. Ramp up voltage for maximum 3920ns (4000ns - deadtime)

Time measurement with Spiroc2E: <u>TDC</u> (time to digital converter)

- 1. Common BIF clock with ~1ns bins

- 2. Ramp up voltage for maximum 3920ns (4000ns deadtime)

- 3. On hit, the current voltage is stored in one of 16 memory cells

Time measurement with Spiroc2E: <u>TDC</u> (time to digital converter)

- 1. Common BIF clock with ~1ns bins

- 2. Ramp up voltage for maximum 3920ns (4000ns deadtime)

- 3. On hit, the current voltage is stored in one of 16 memory cells

- 4. Memory cells are digitized

- 5. Resulting TDC value needs to be related to hit time in ns → Calibration

Pedestal

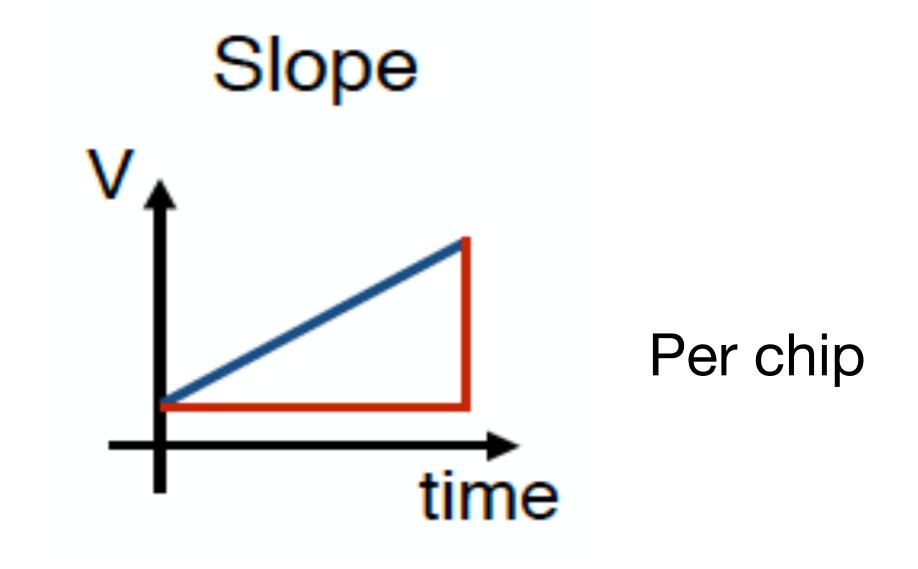

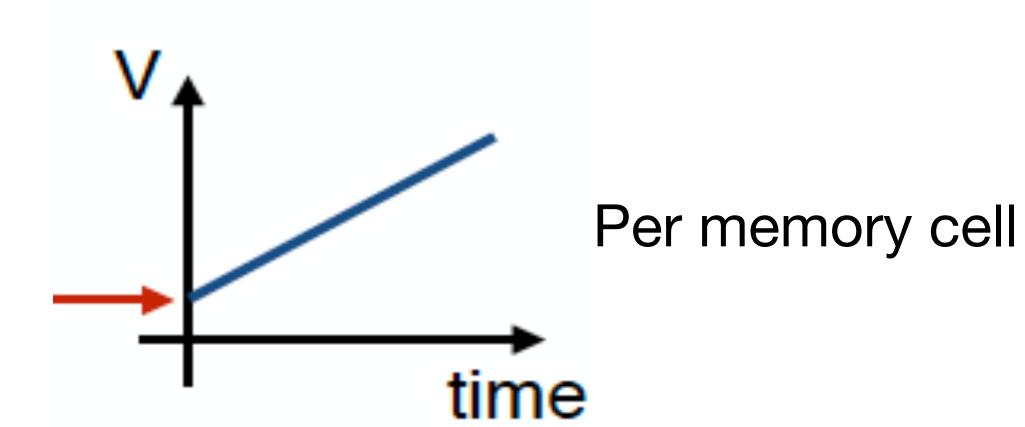

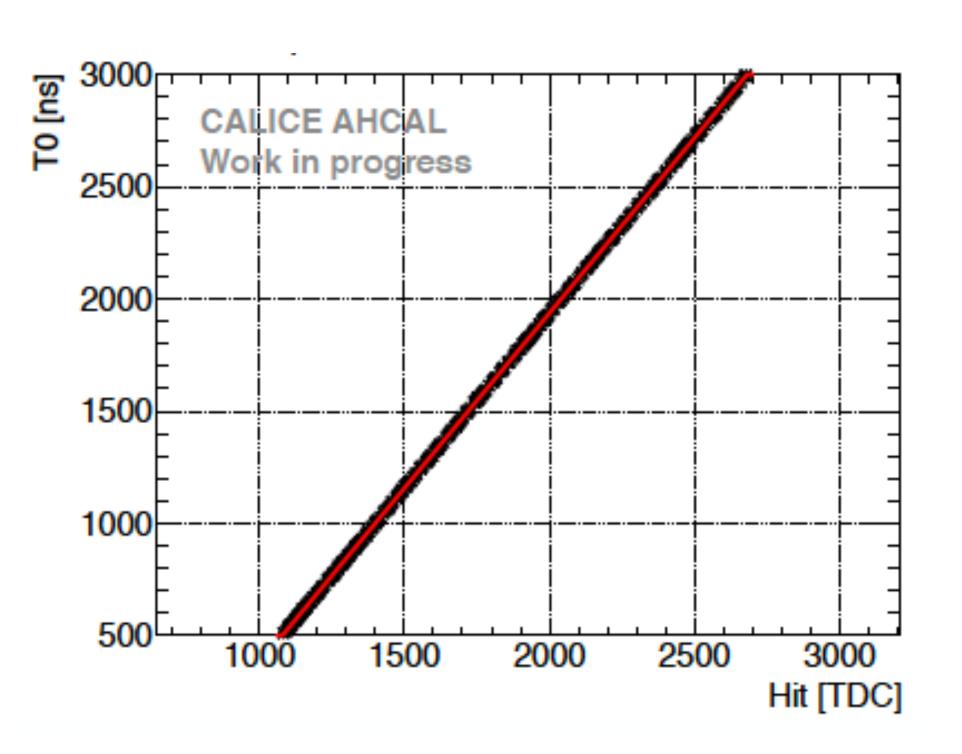

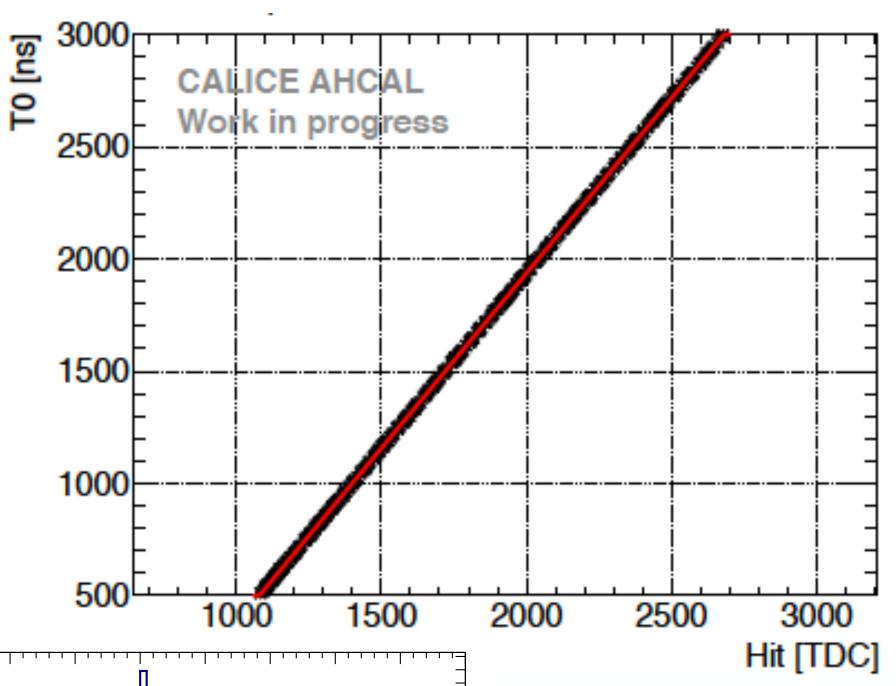

### Time Calibration: Software

All memory cells to be calibrated against common clock (T0[ns]):

- 1. Extract TDC slope by plotting T0 vs TDC

- Fit slope for even and odd bxID per chip

## Time Calibration: Software

All memory cells to be calibrated against common clock (T0[ns]):

- 1. Extract TDC slope by plotting T0 vs TDC

- Fit slope for even and odd bxID per chip

- 2. Extract offset for every memory cell (576 per chip)

- 3. Calculate hit time by

$$t_{hit}[\text{ns}] = \text{TDC}_{\text{hit}} \cdot \text{Slope}\left[\frac{\text{ns}}{\text{TDC}}\right] + \text{Offset}\left[\text{ns}\right] - T_0$$

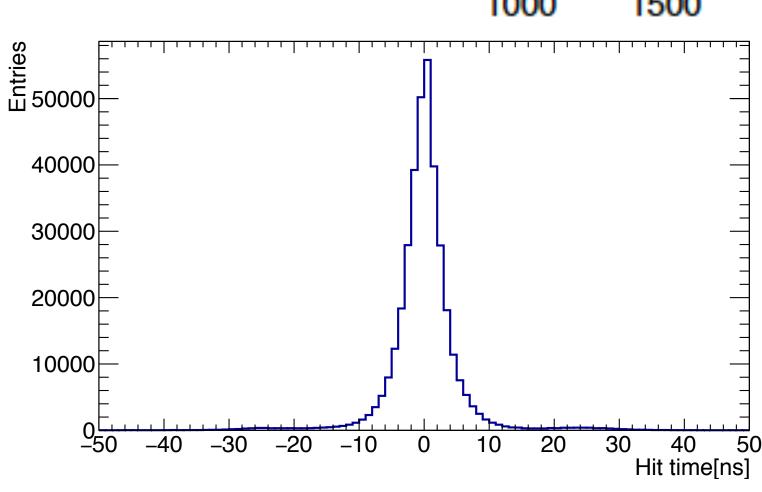

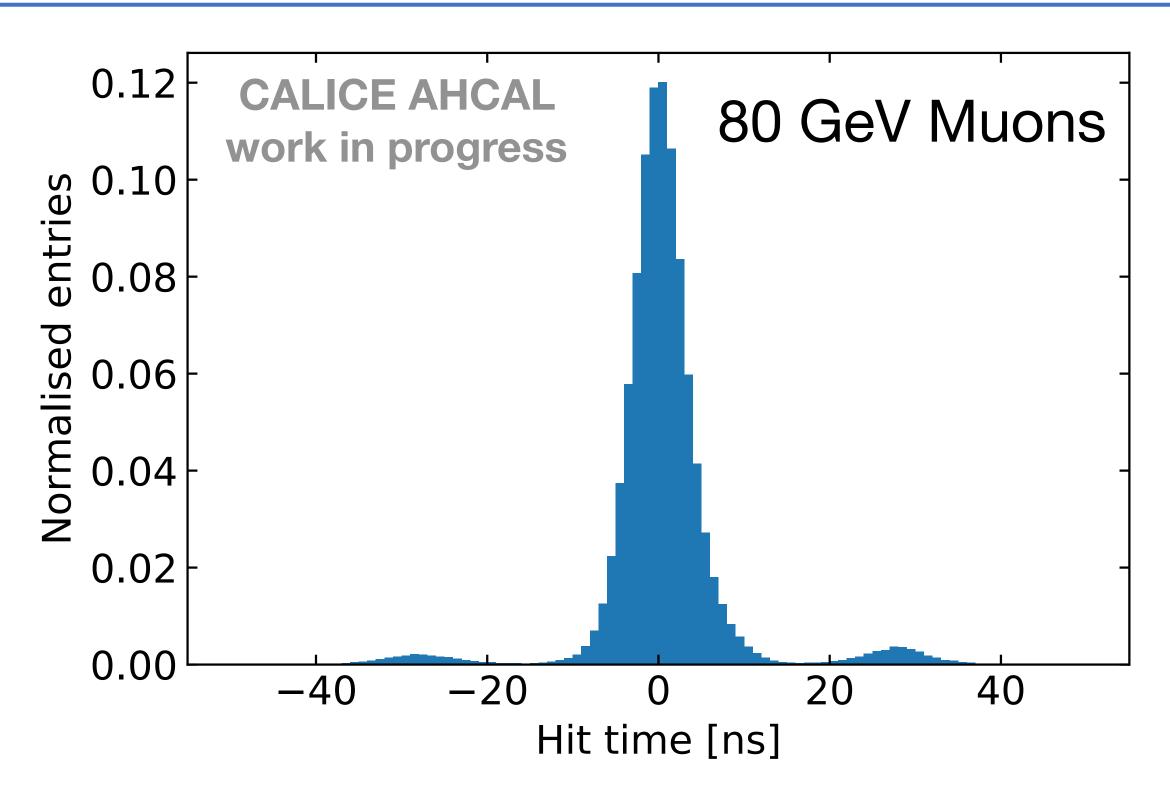

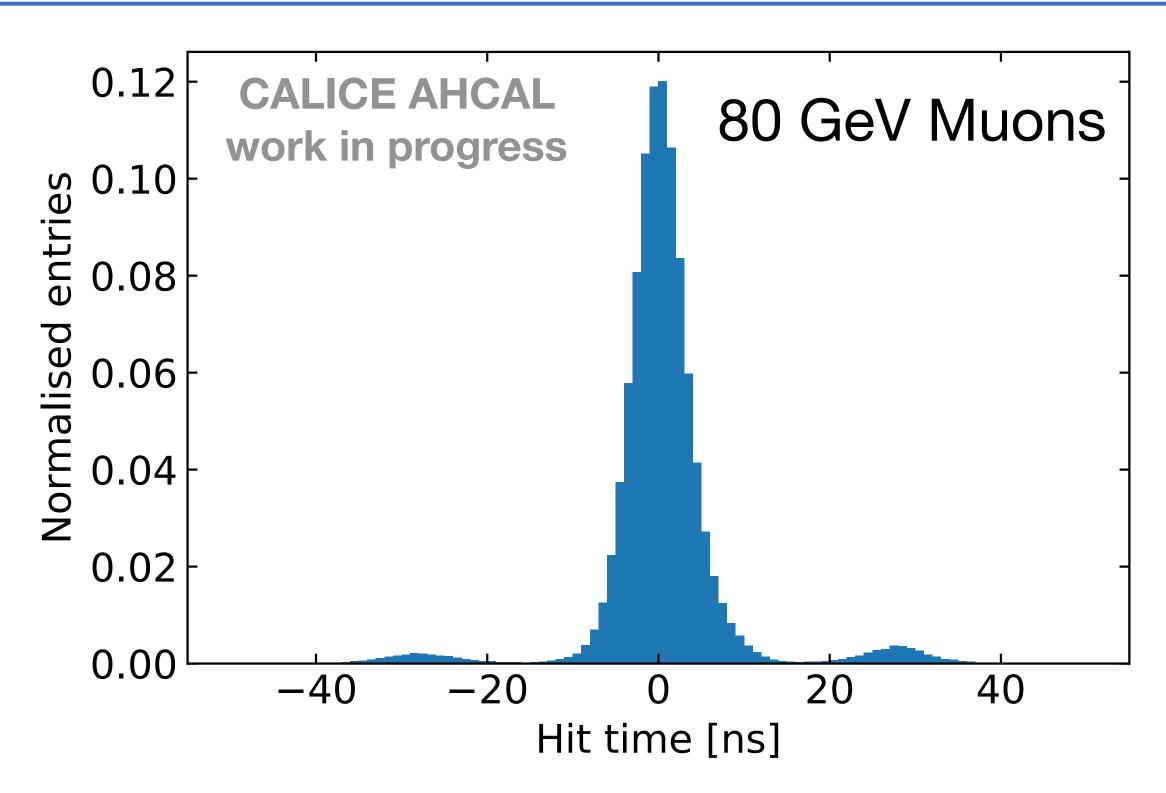

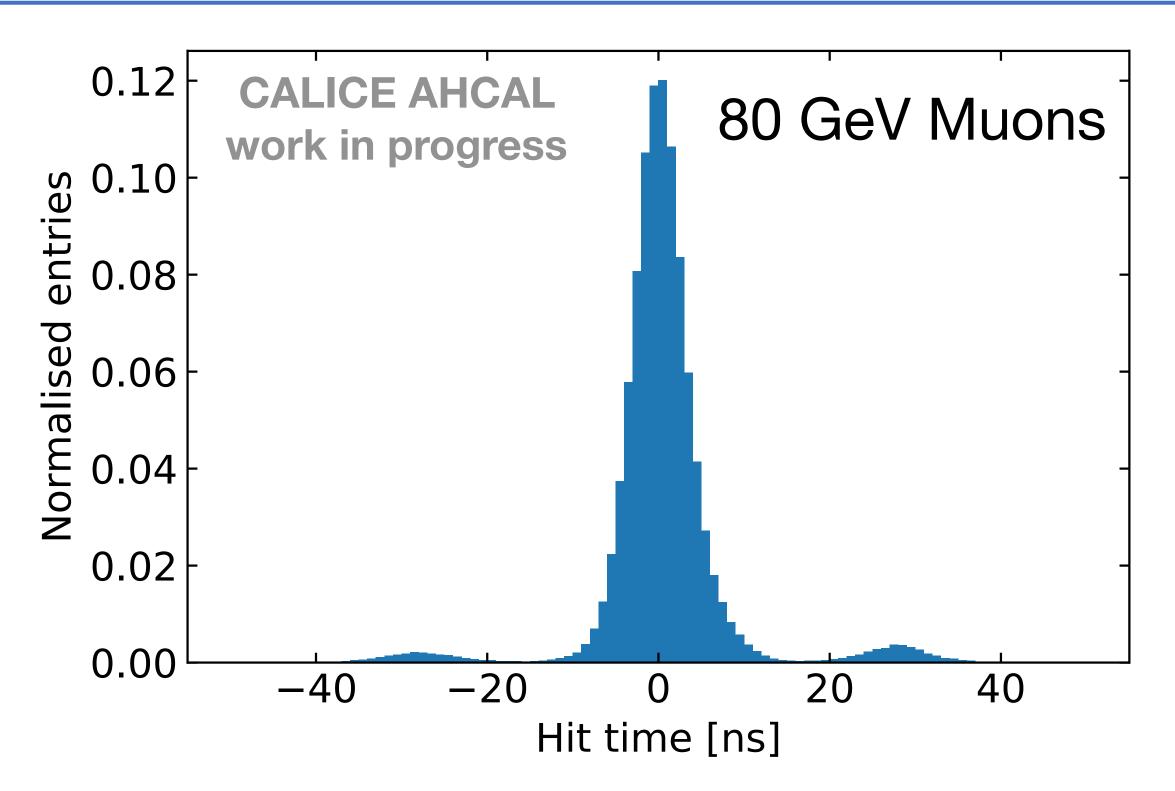

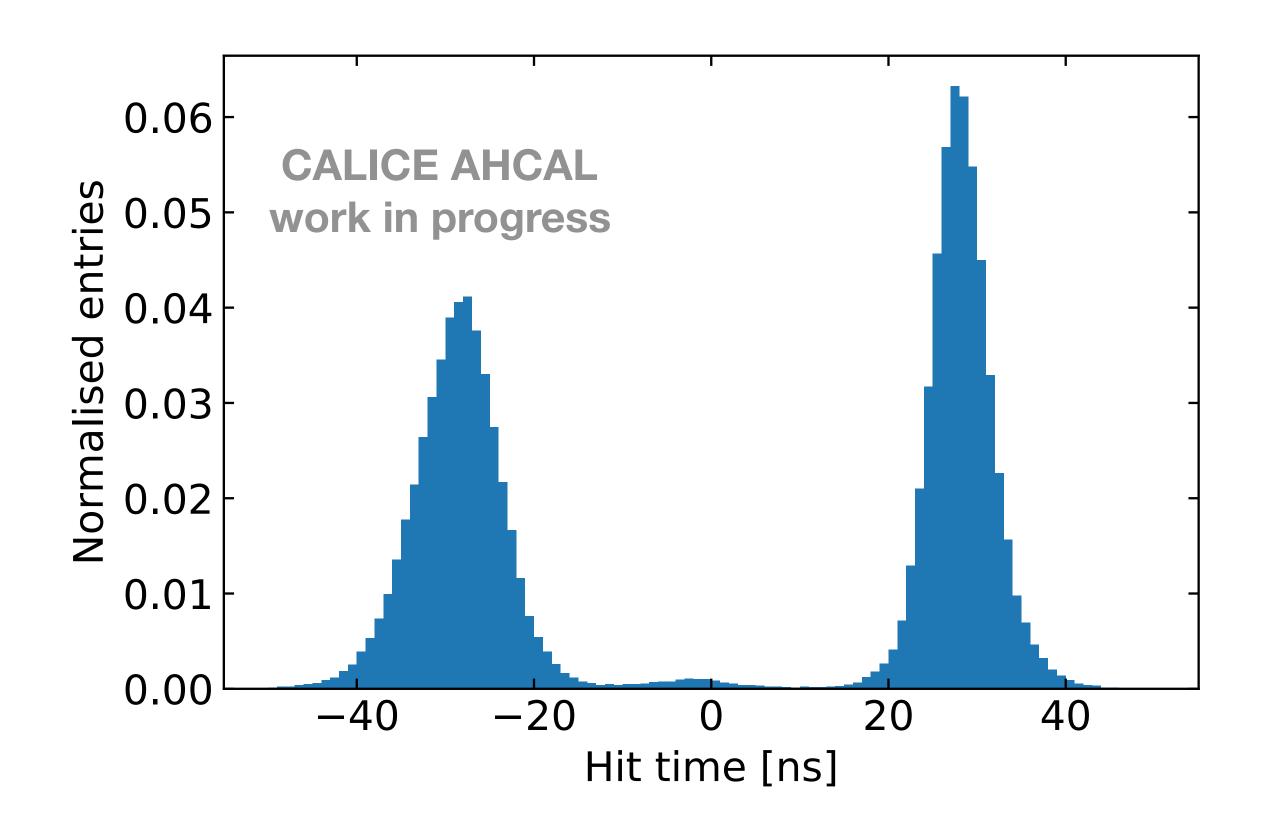

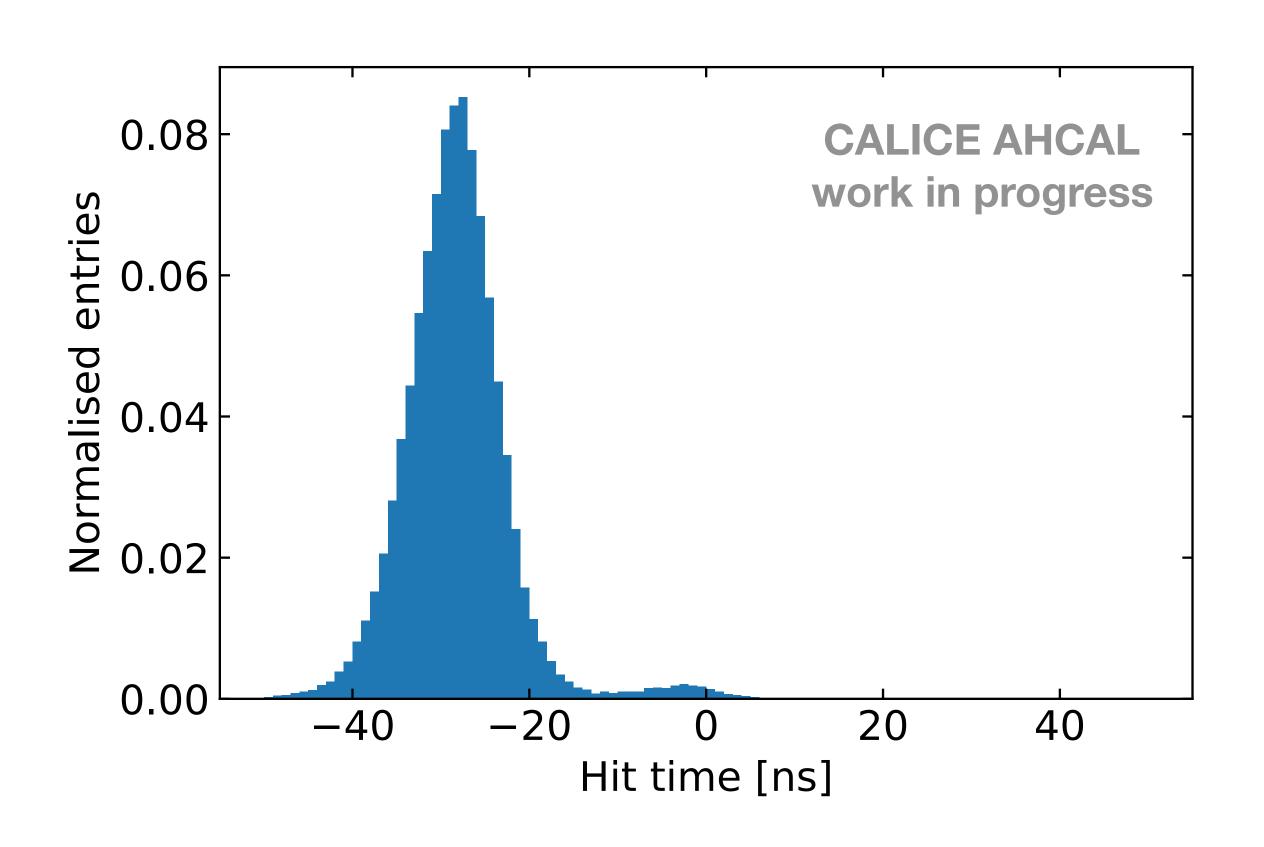

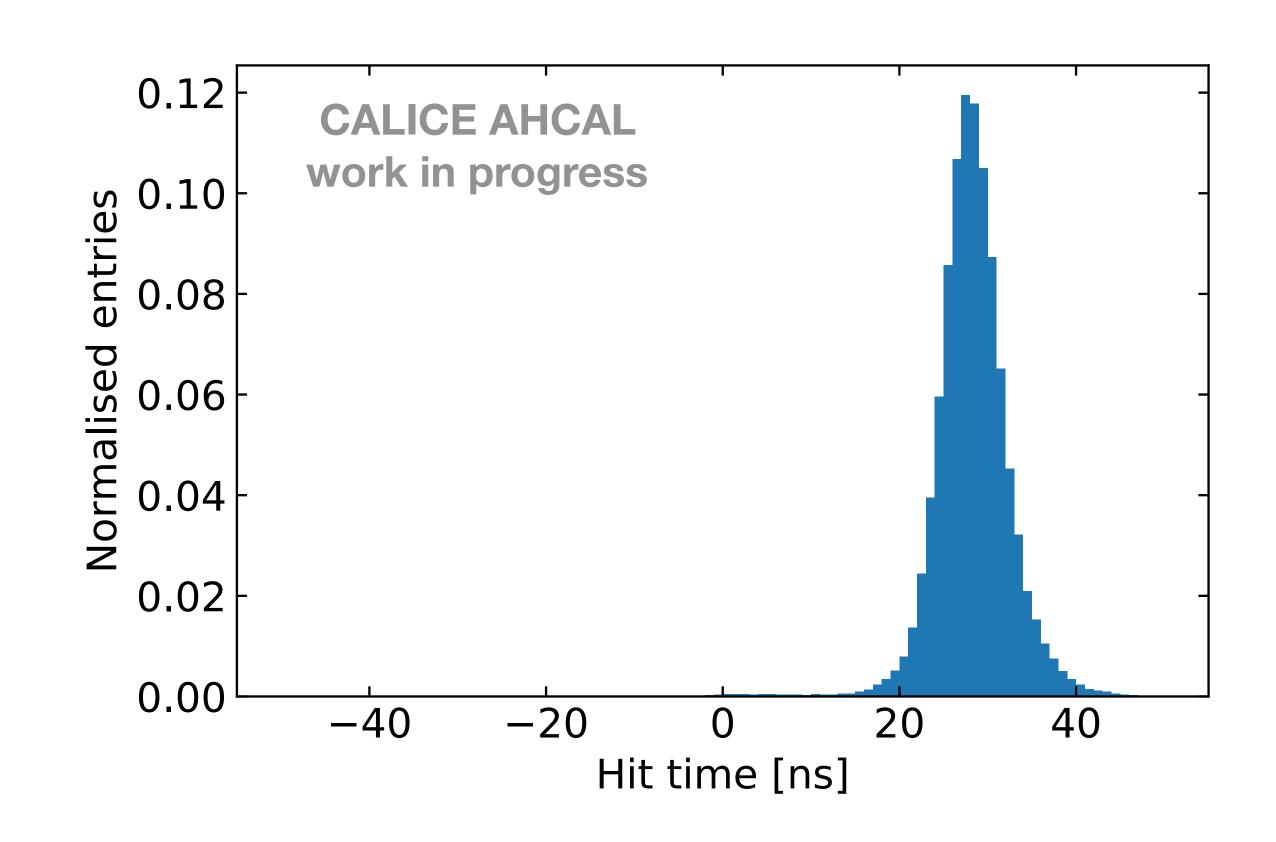

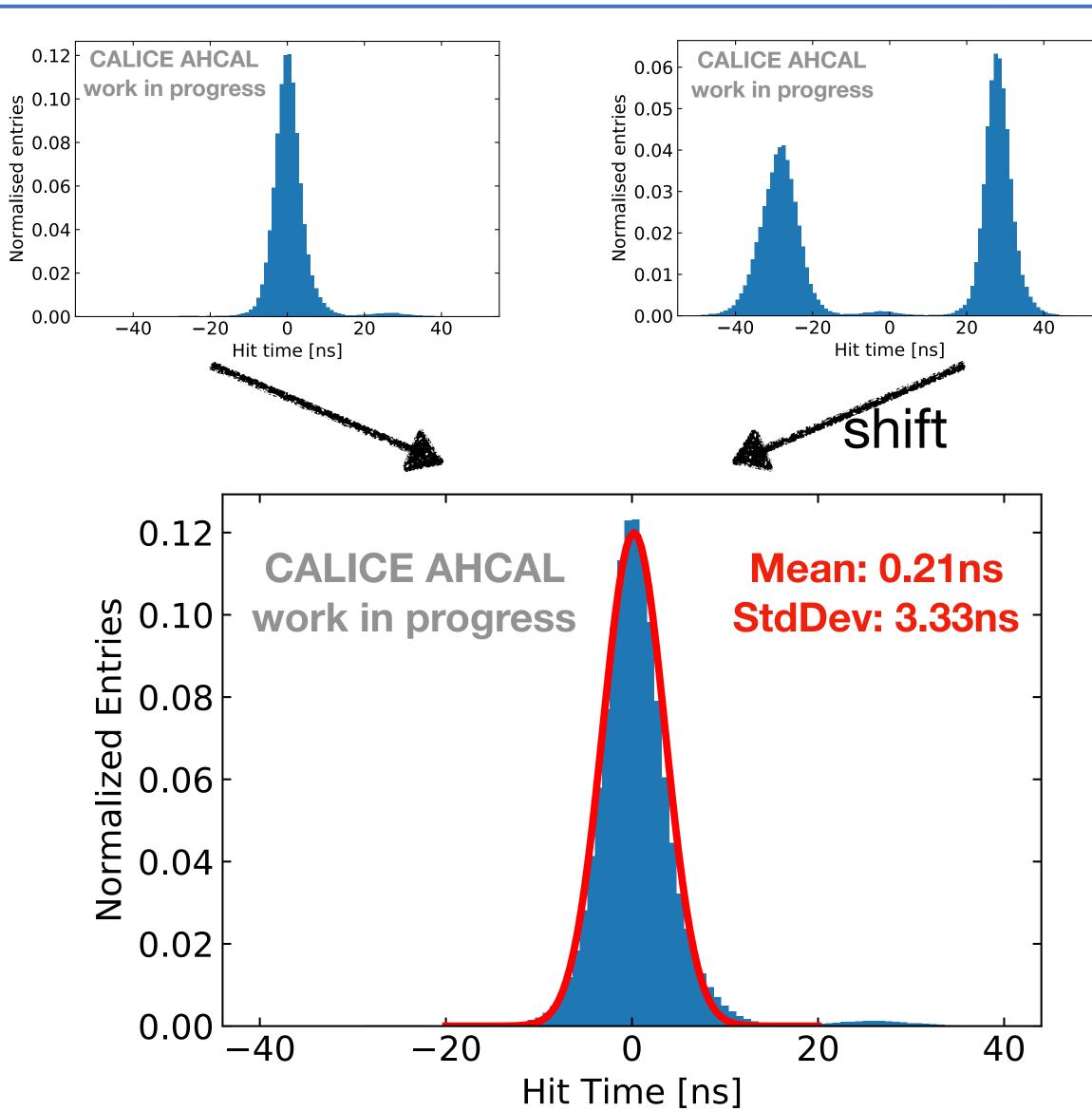

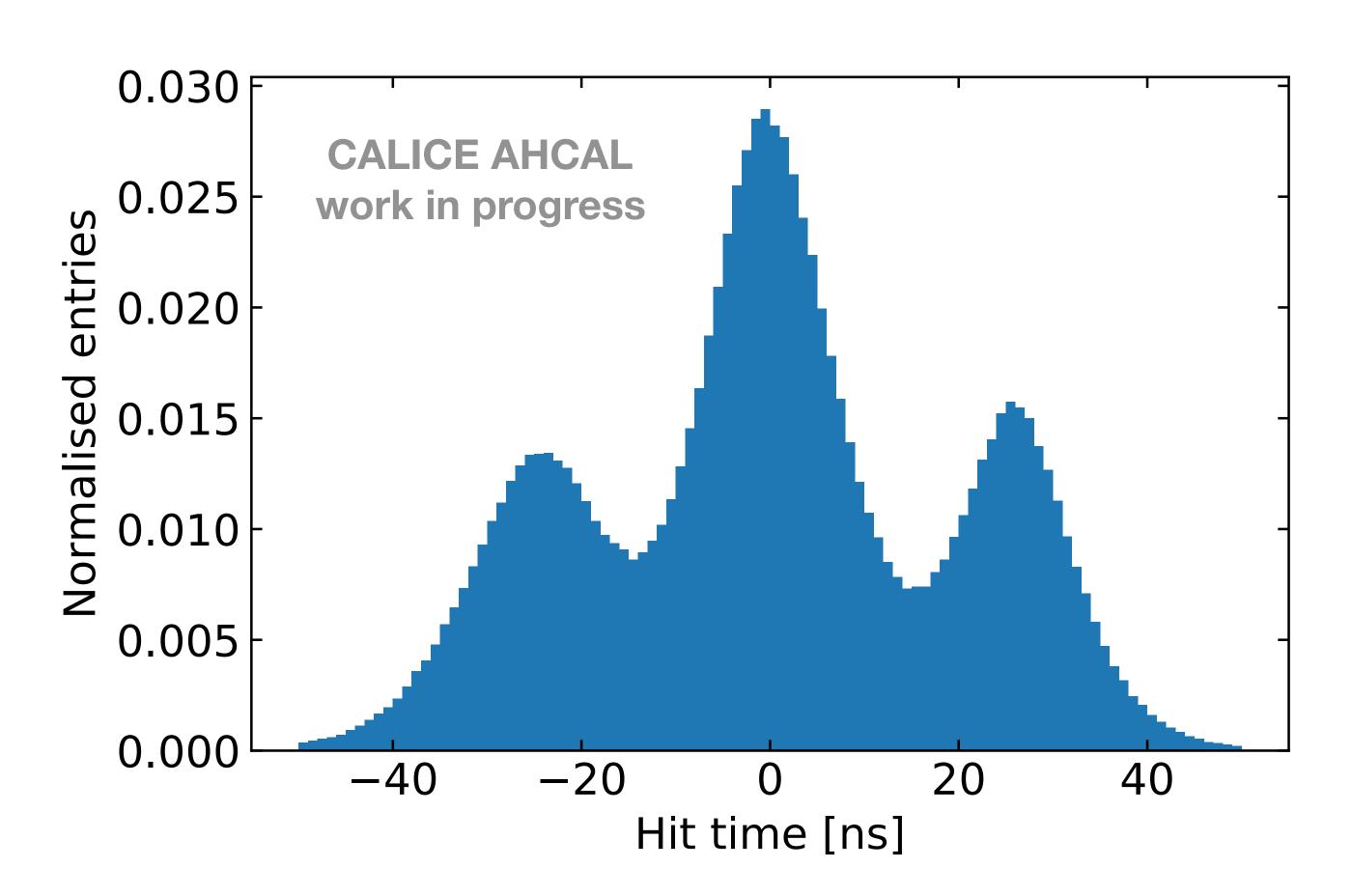

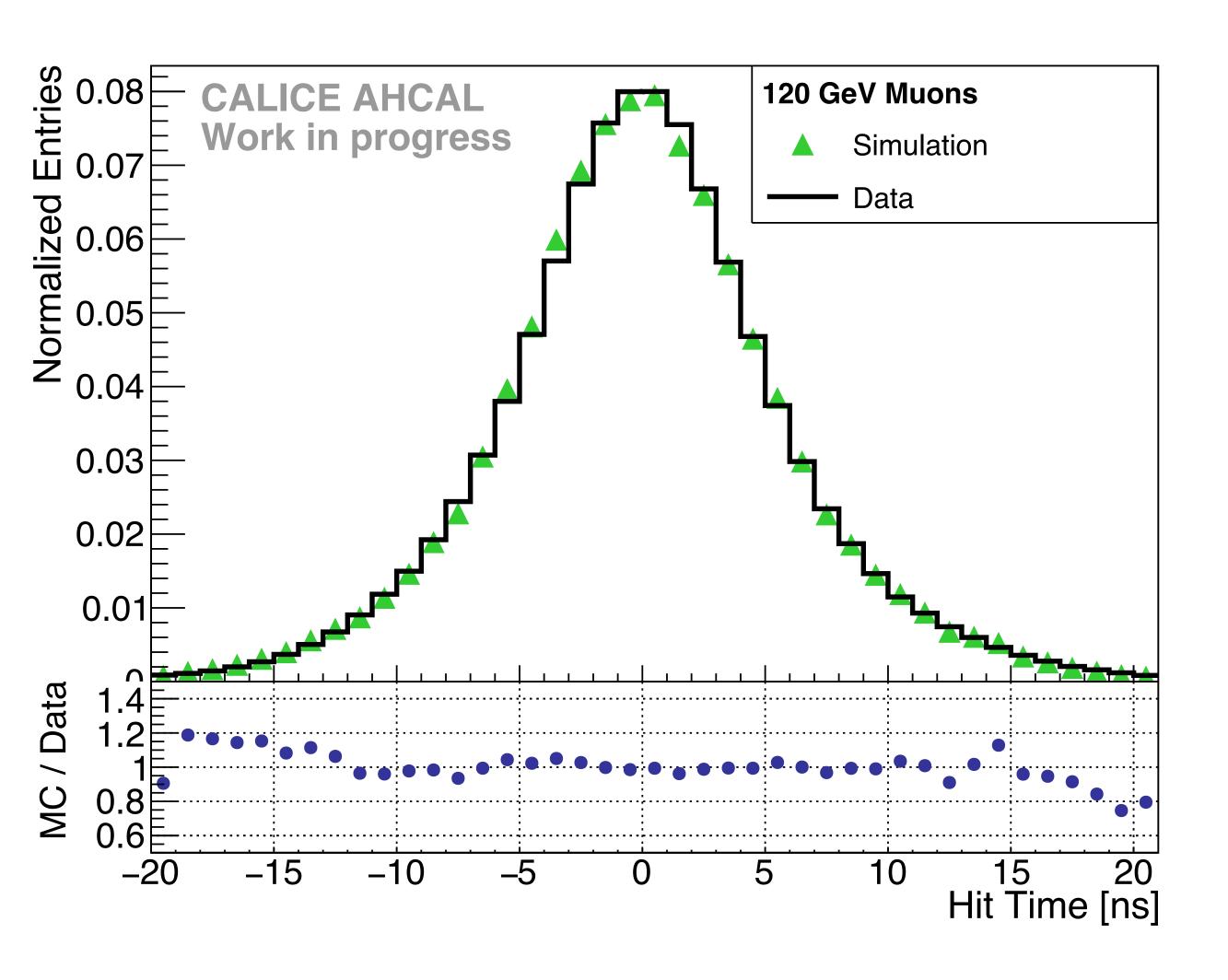

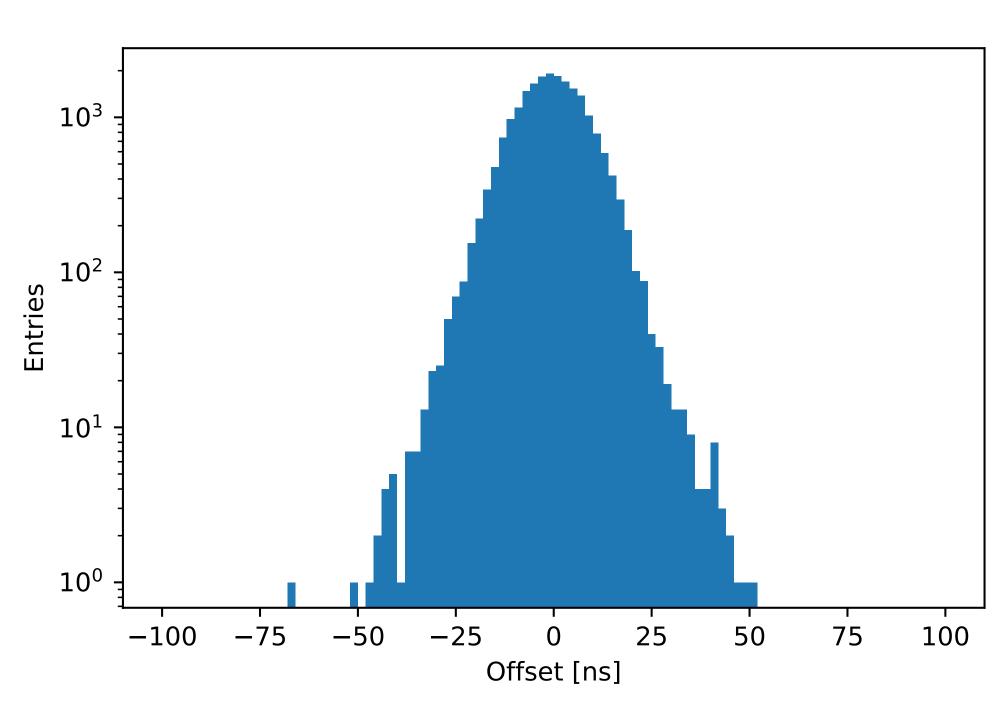

Hit time distribution

Main peak at 0ns Satellite Peaks at ±28ns

Tried to correct by cuts and event categorisation (shown at the AHCAL Main Meeting 2018)

Main peak at 0ns Satellite Peaks at ±28ns

Tried to correct by cuts and event categorisation (shown at the AHCAL Main Meeting 2018)

Achieved time resolution:

- ~3.3ns for Muons

- ~7ns for Electrons

11

Main peak at 0ns Satellite Peaks at ±28ns

Tried to correct by cuts and event categorisation (shown at the AHCAL Main Meeting 2018)

Hypothesis: Problem connected with stopping condition of readout cycle

- Shift depends on BxID parity of ASIC with full memory cells

- Direction depends on the BxID parity of the event

Achieved time resolution:

~3.3ns for Muons

~7ns for Electrons

New approach

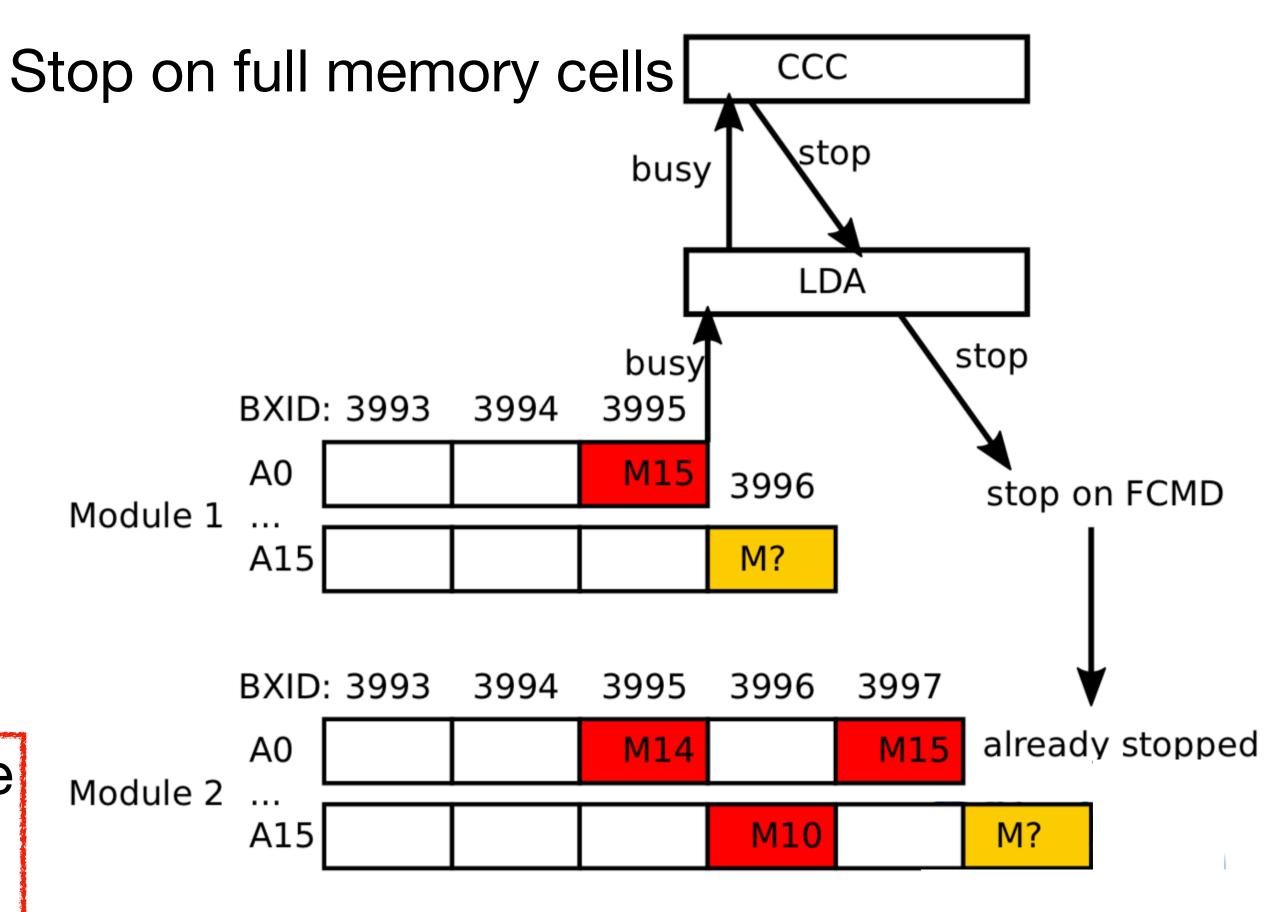

## Stopping of the Acquisition

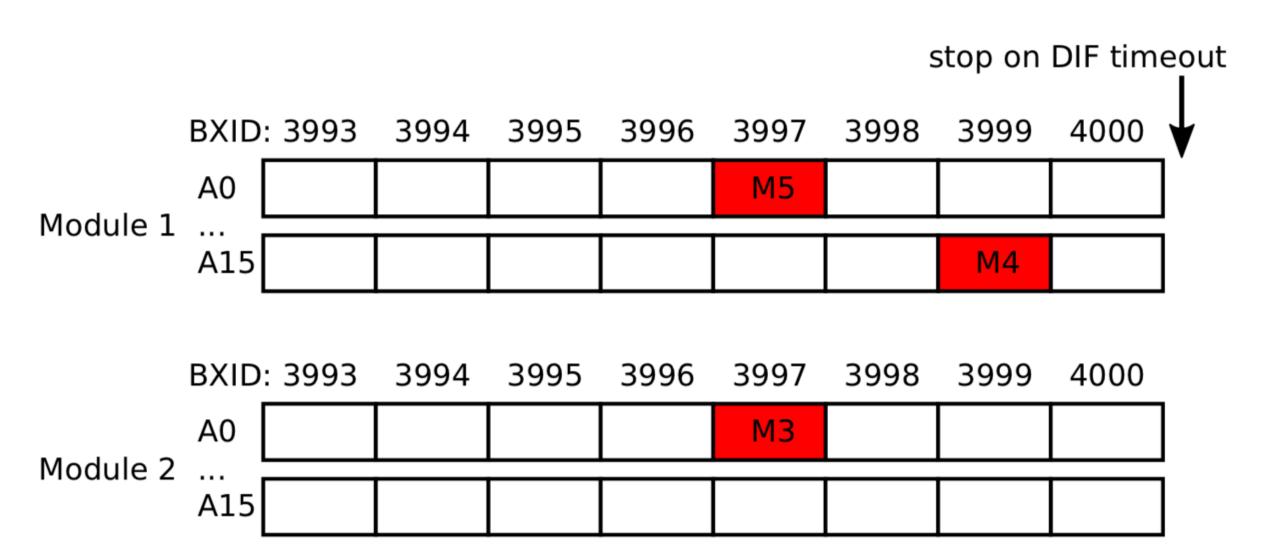

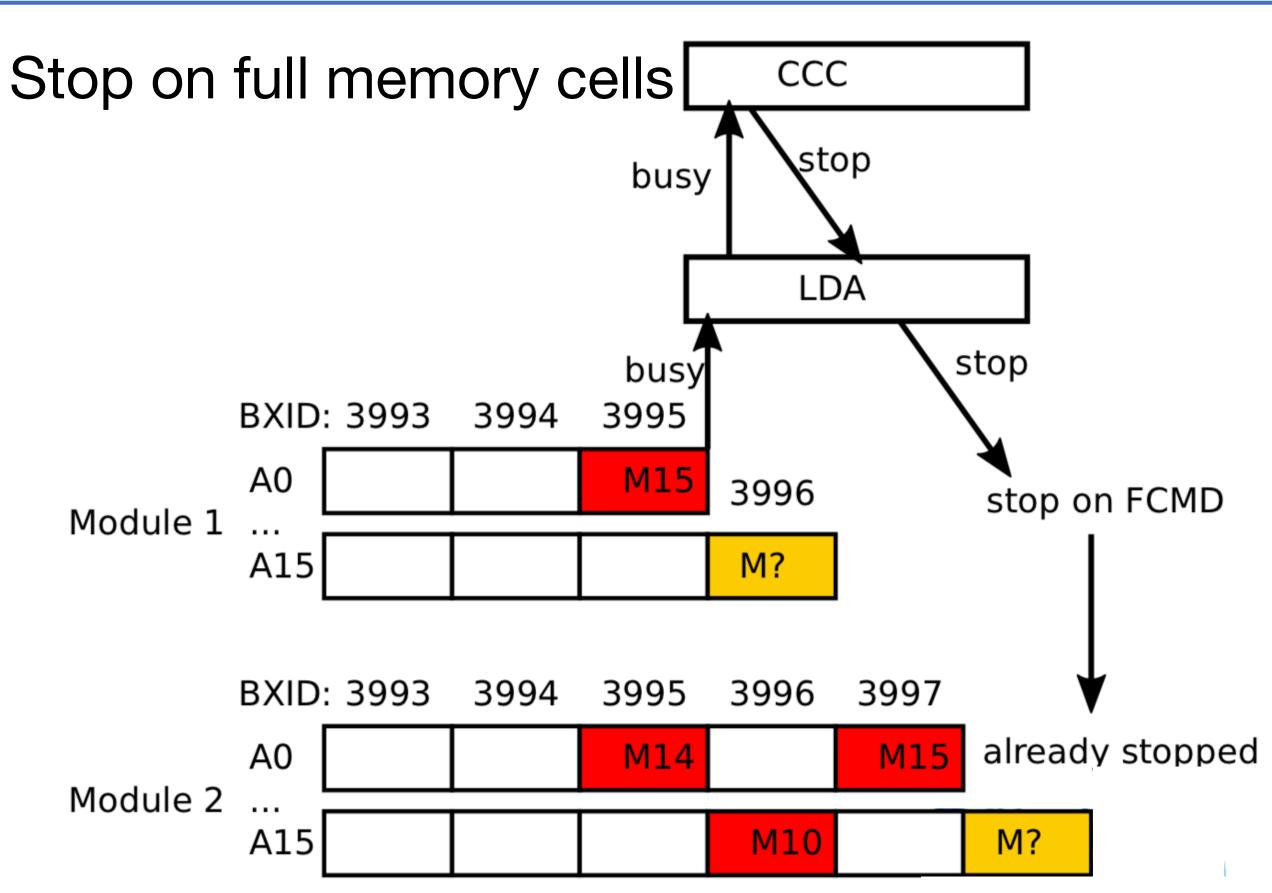

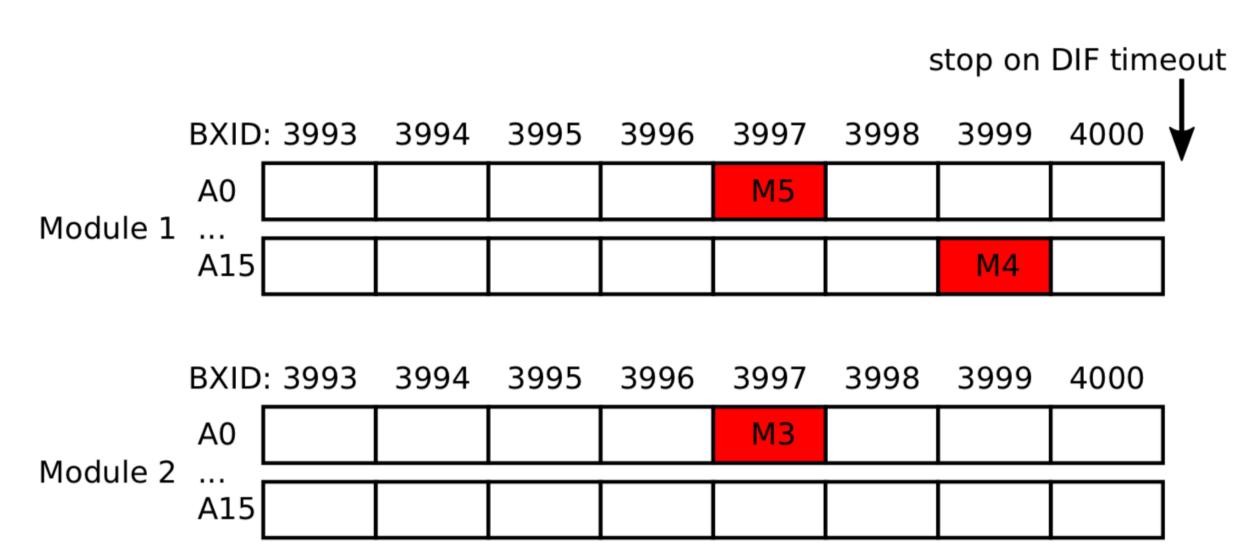

#### Stop after predefined timeout

## Stopping of the Acquisition

#### Stop after predefined timeout

Figures taken from J. Kvasnicka AHCAL Main Meeting 2018

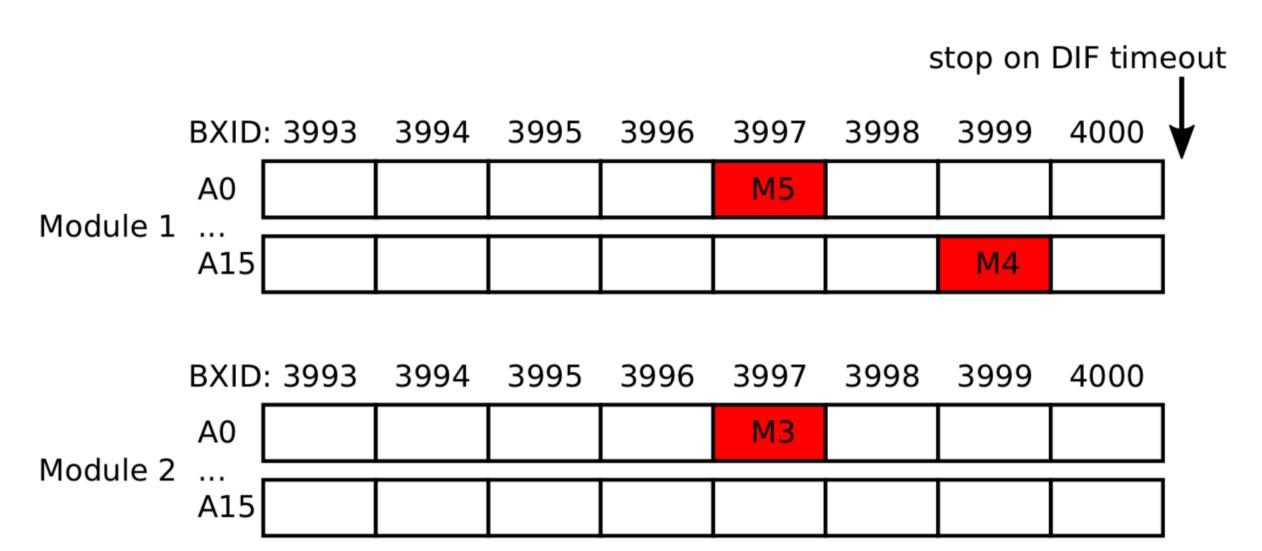

### Stopping of the Acquisition

#### Stop after predefined timeout

Information on termination of the read out cycle in .slcio files:

- time out / <u>full memory cell</u>

- First filled ASIC and corresponding BxID

Figures taken from J. Kvasnicka AHCAL Main Meeting 2018

13

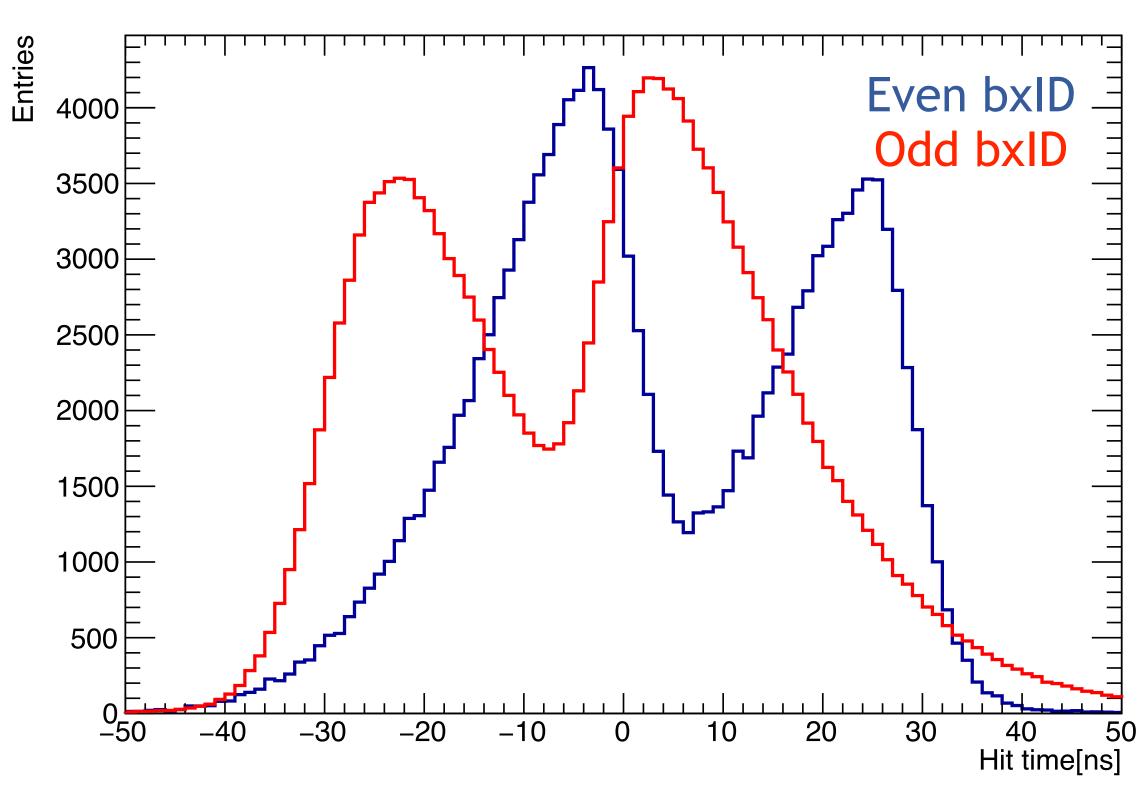

Shift depends on the parity of last bxID in read out cycle ended by full memory cell:

• If odd  $\Longrightarrow$  no shift

Shift depends on the parity of last bxID in read out cycle ended by full memory cell:

- If odd  $\Longrightarrow$  no shift

- If even ⇒ shift of ±28ns

Shift depends on the parity of last bxID in read out cycle ended by full memory cell:

- If odd  $\Longrightarrow$  no shift

- If even  $\Longrightarrow$  shift of  $\pm 28$ ns

Sign of the shift depends on the BxID parity of the event

• If odd  $\Longrightarrow$  -28ns

Shift depends on the parity of last bxID in read out cycle ended by full memory cell:

- If odd  $\Longrightarrow$  no shift

- If even  $\Longrightarrow$  shift of  $\pm 28$ ns

Sign of the shift depends on the BxID parity of the event

- If odd  $\Longrightarrow$  -28ns

- If even  $\Longrightarrow$  +28ns

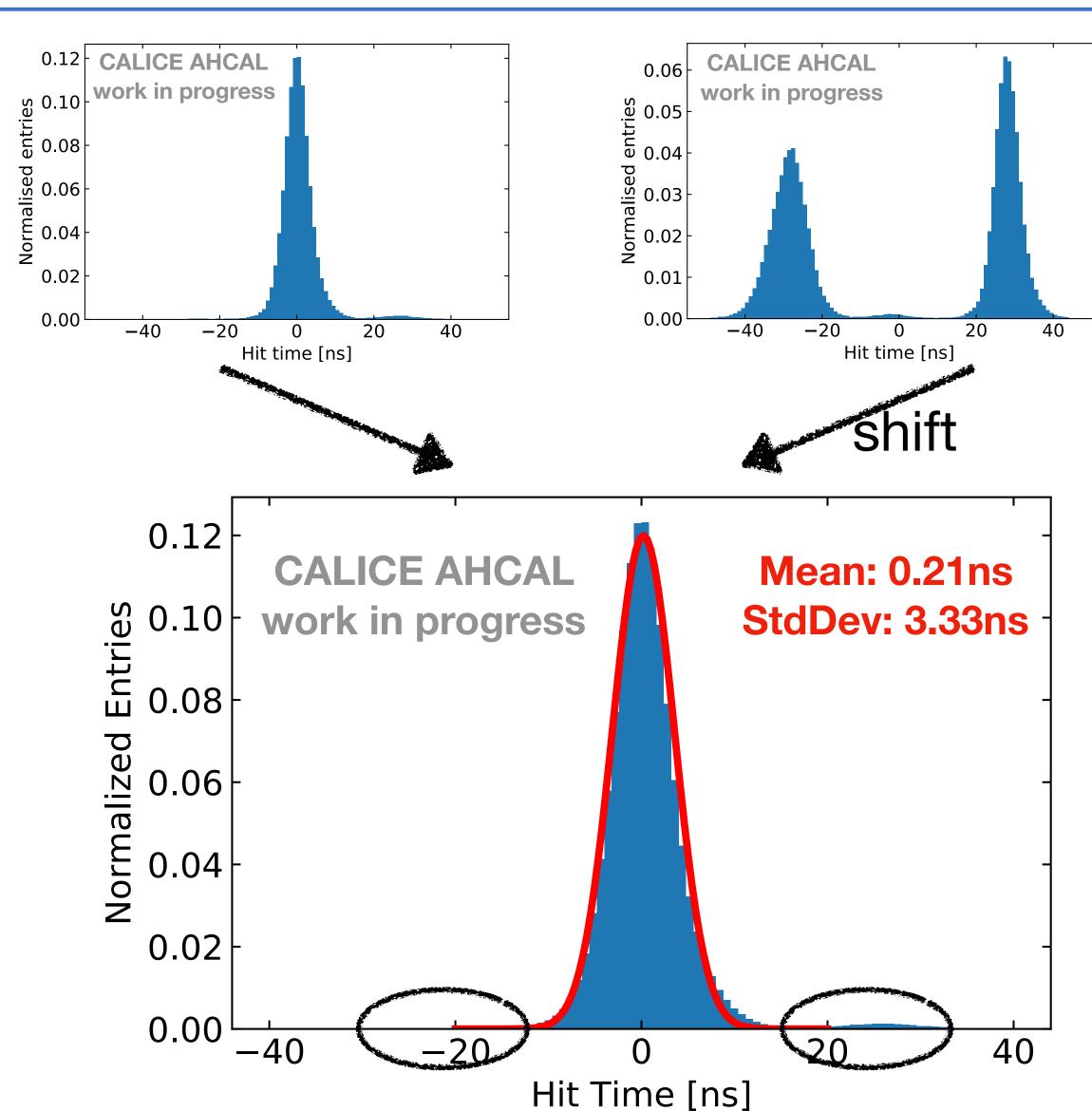

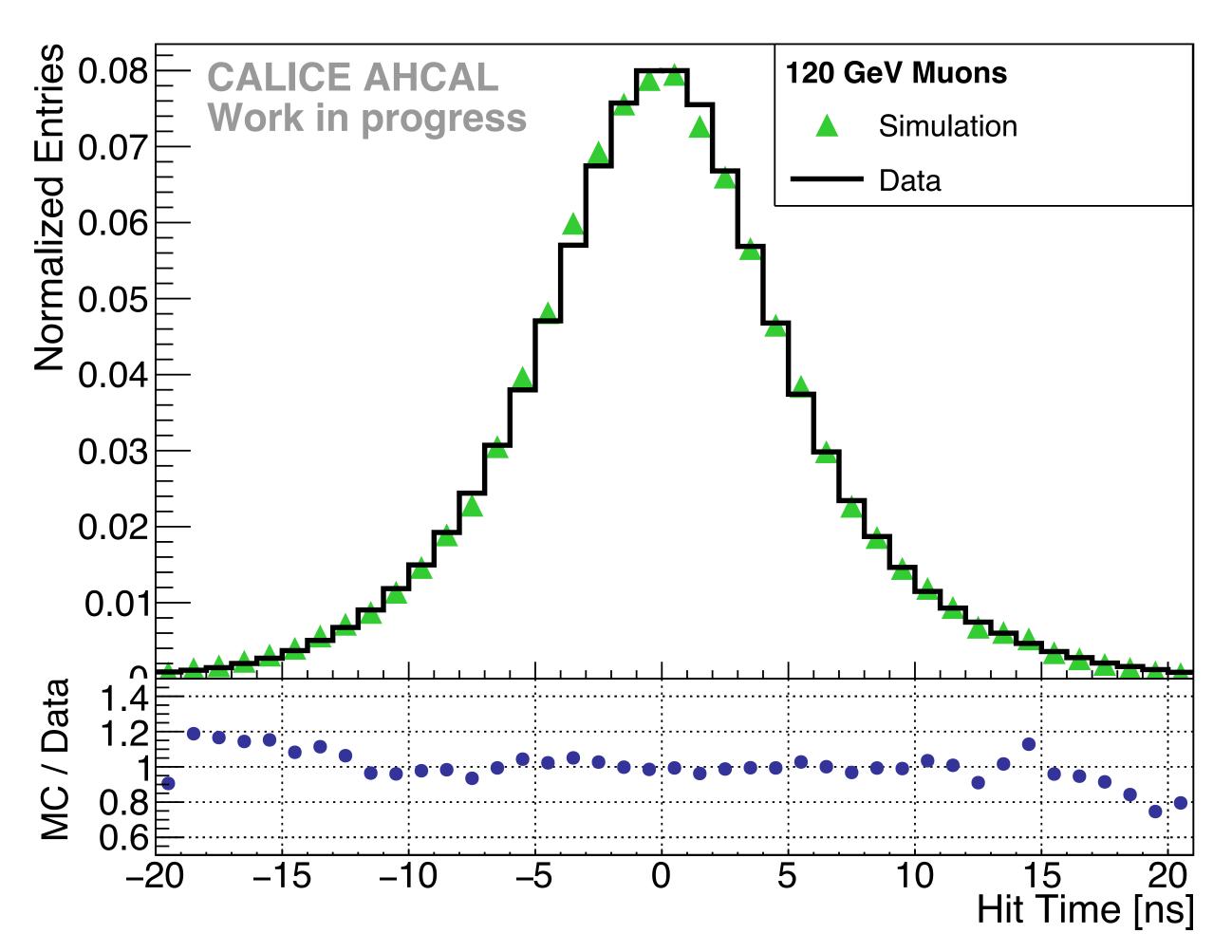

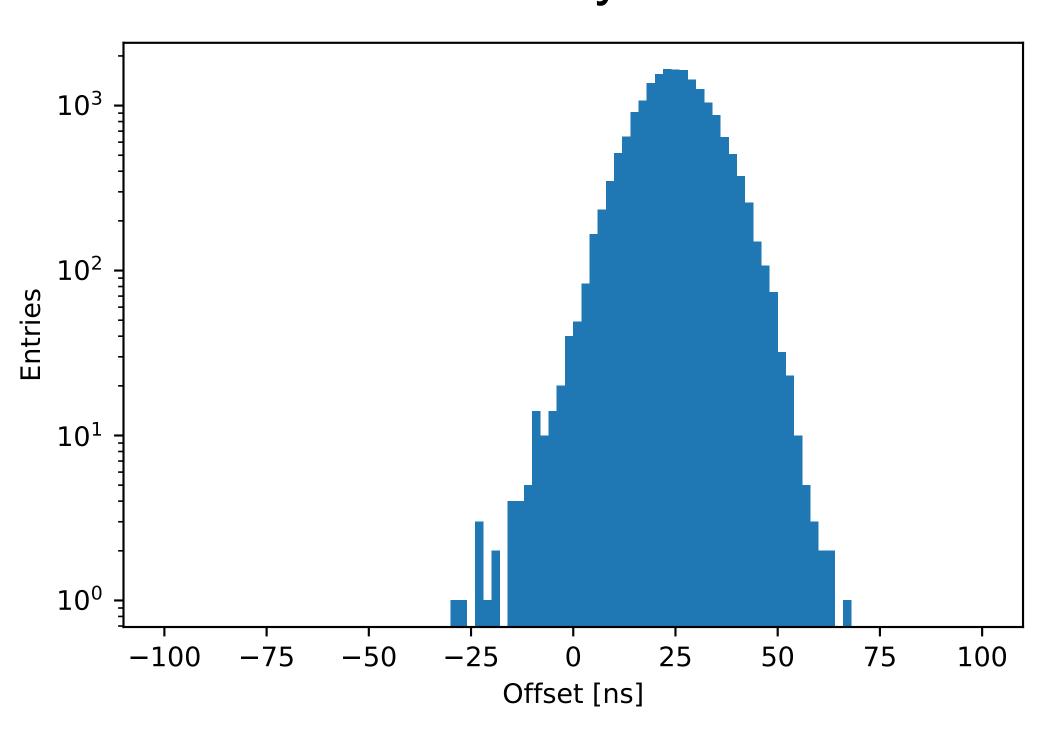

Shift depends on the parity of last bxID in read out cycle ended by full memory cell:

- If odd  $\Longrightarrow$  no shift

- If even ⇒ shift of ±28ns

Sign of the shift depends on the BxID parity of the event

- If odd  $\Longrightarrow$  -28ns

- If even  $\Longrightarrow$  +28ns

Deterministic chip effect, can be corrected

Shift depends on the parity of last bxID in read out cycle ended by full memory cell:

- If odd  $\Longrightarrow$  no shift

- If even ⇒ shift of ±28ns

Sign of the shift depends on the BxID parity of the event

- If odd  $\Longrightarrow$  -28ns

- If even  $\Longrightarrow$  +28ns

Remaining bumps due to shifted calibration constants  $\Longrightarrow$  under investigation

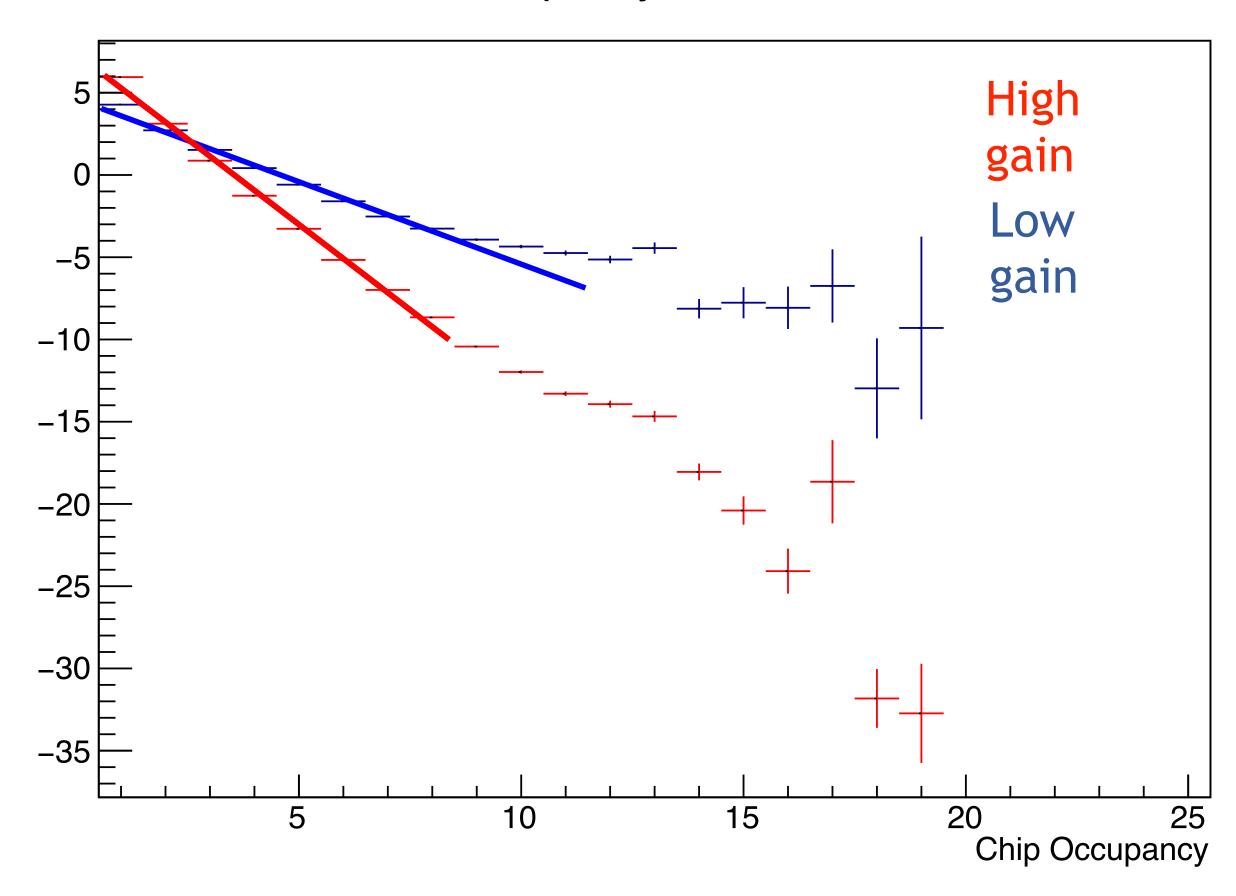

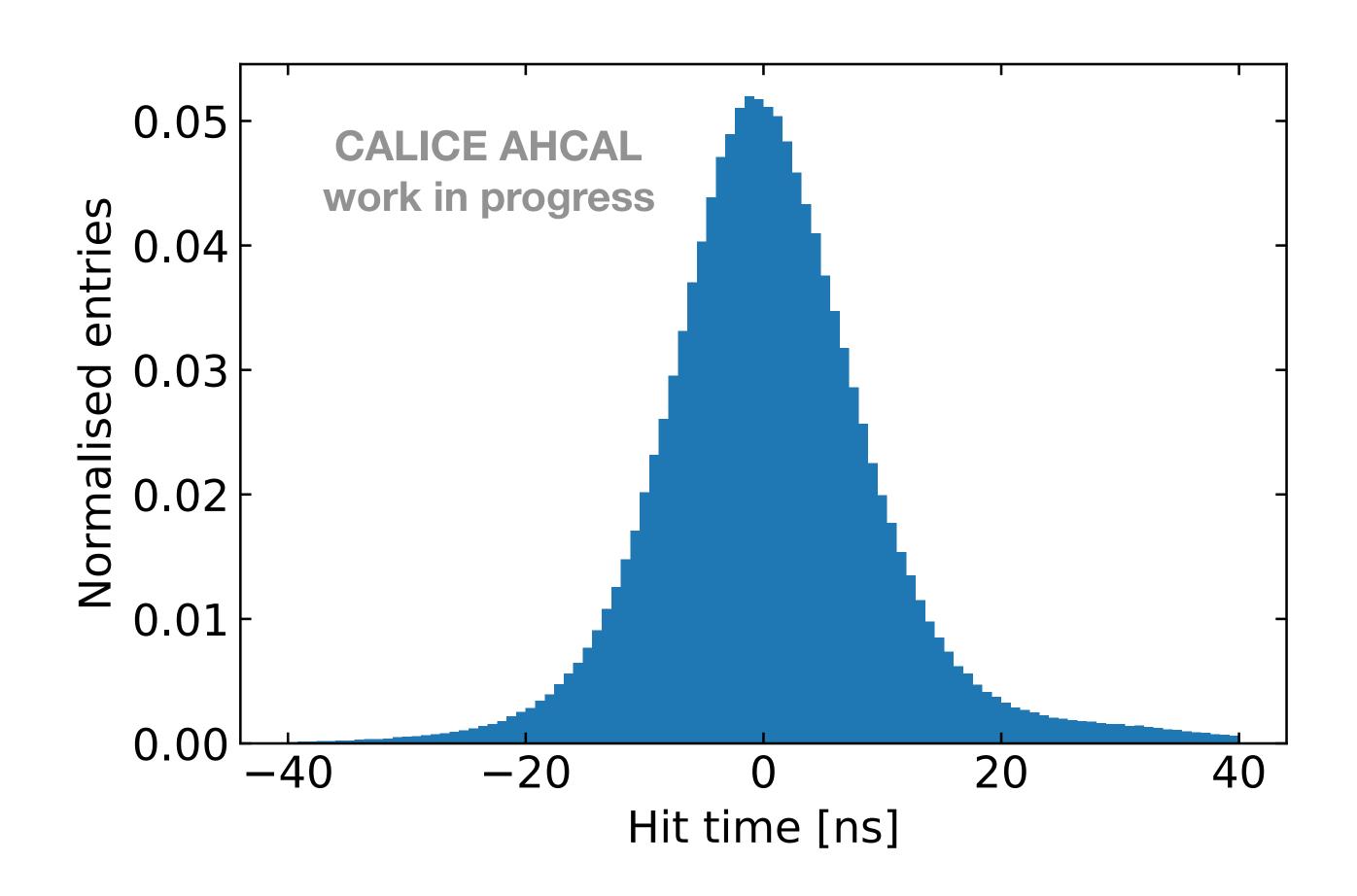

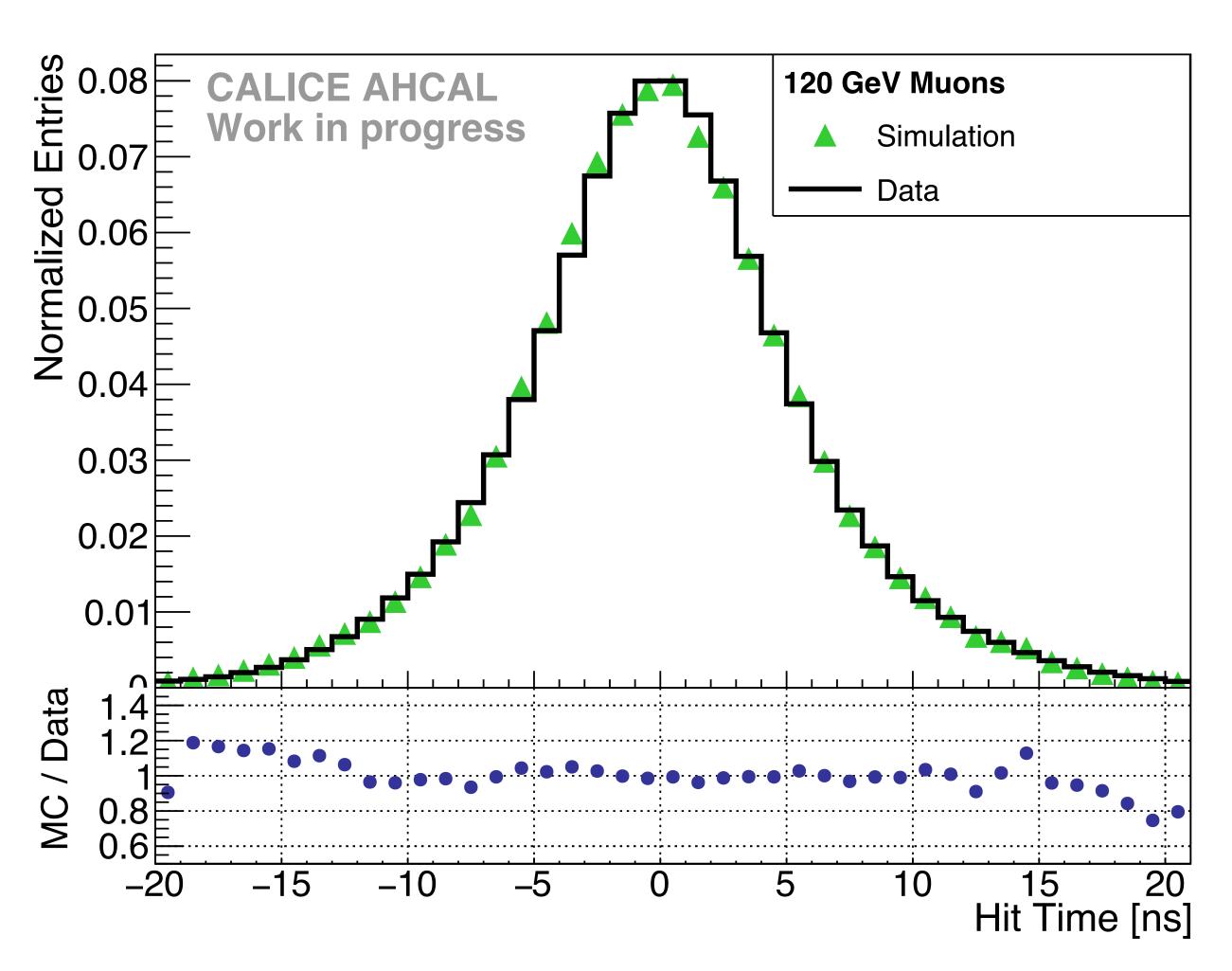

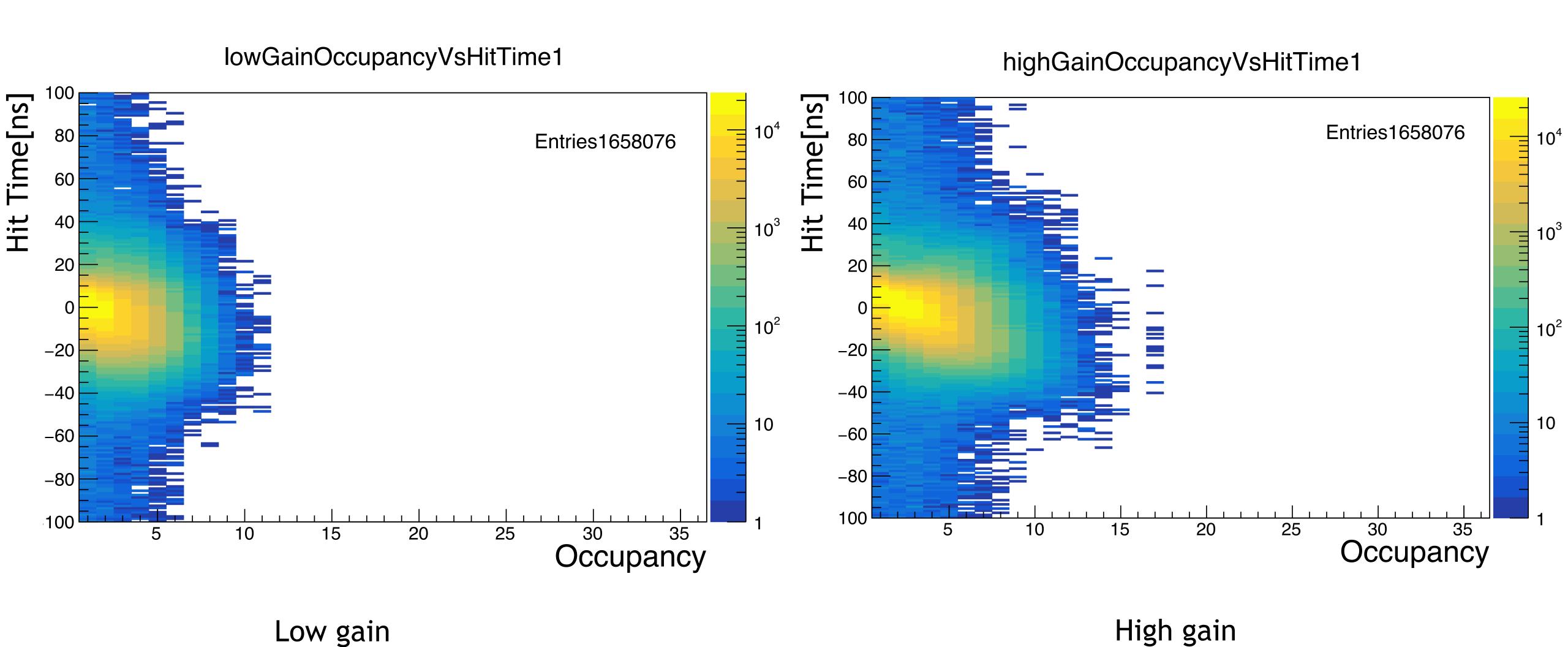

### Electron Time Resolution - CERN 2018

#### Time resolution deteriorates:

- Broadening of the hit time distribution with rising chip occupancy

- Preliminary occupancy correction applied

## Electron Time Resolution - CERN 2018

#### Time resolution deteriorates:

- Broadening of the hit time distribution with rising chip occupancy

- Preliminary occupancy correction applied

Shift correction identical to muons

Time resolution at 6-7ns

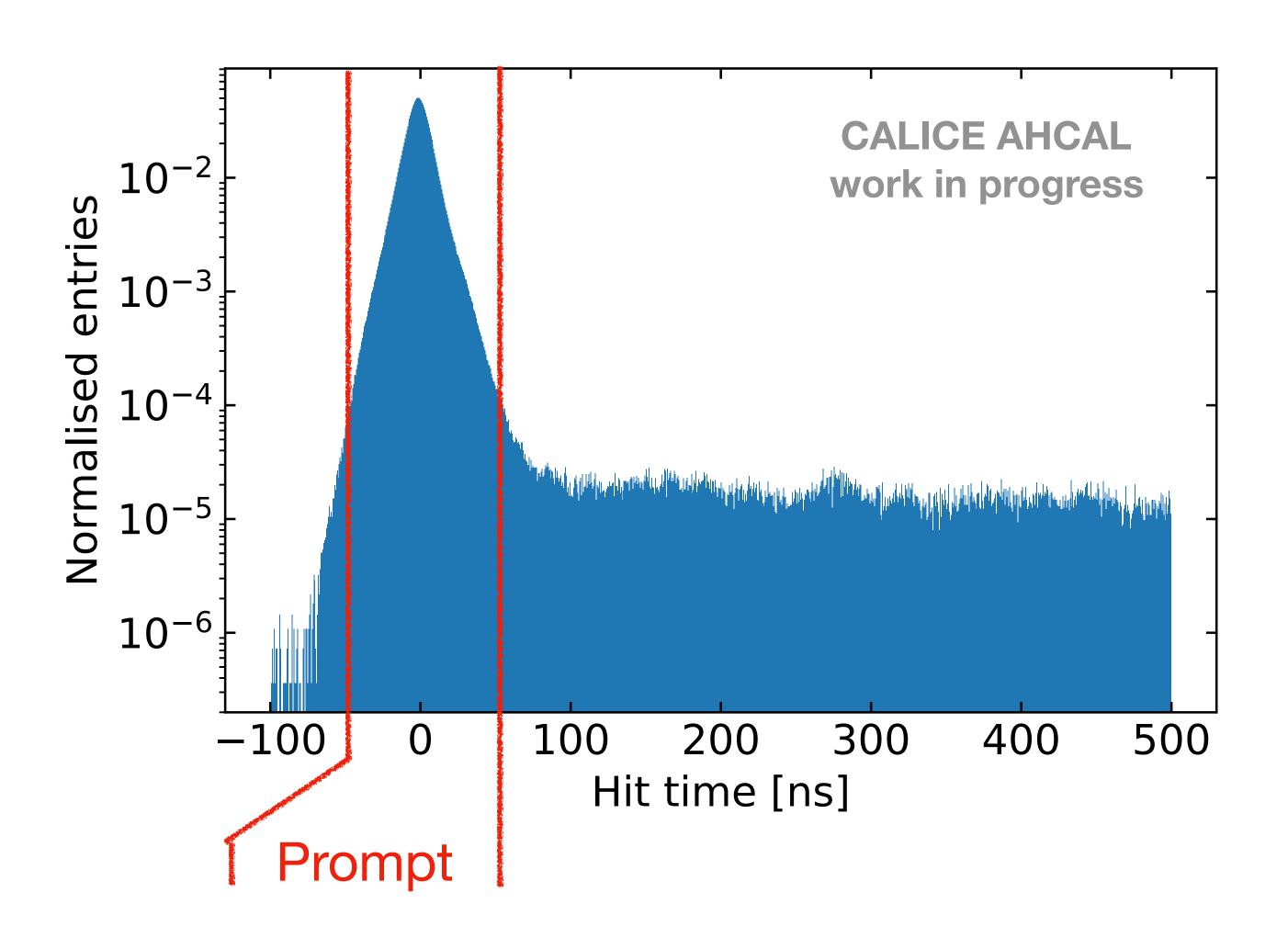

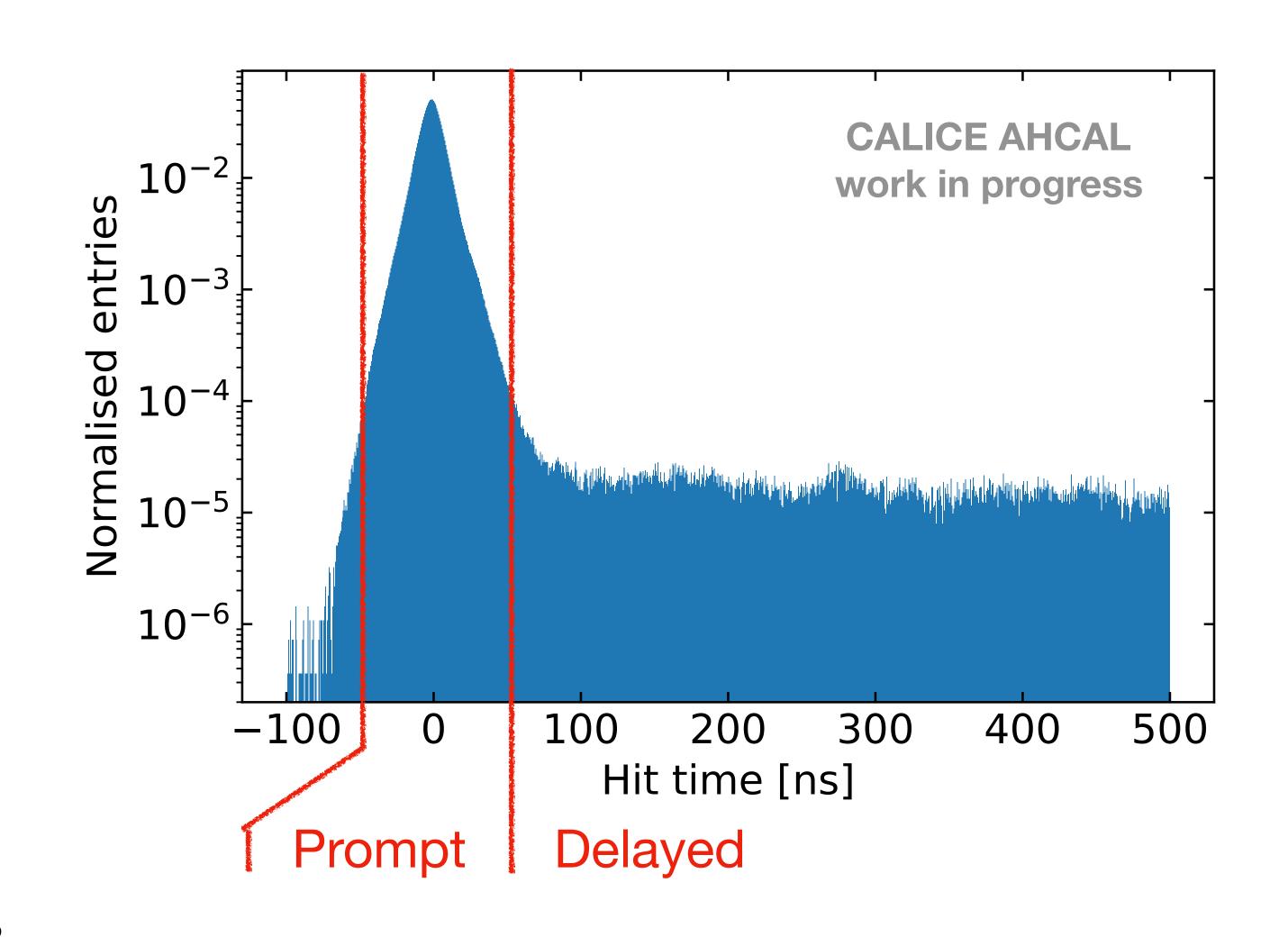

#### Subjected to same chip effects:

Time resolution of main peak comparable to electrons

#### Subjected to same chip effects:

Time resolution of main peak comparable to electrons

#### Visible "physics tail":

- Delayed energy depositions from:

- Elastic neutron scattering

⇒ Use to identify shower components

#### Chip effects observed in hit time distribution:

- Connected to state of detector at the end of a read out cycle

- Shift only occurs if one chip issued busy in an even BxID

- Positive shift for even BxID events, negative shift for odd

Achieved muon time resolution: ~3.3 ns without time walk correction

Achieved electron time resolution: ~6 - 7ns after occupancy correction, without time walk

Calibration constants picked up chip effects  $\Longrightarrow$  expect improvement after recalibration with corrected data

⇒ reprocessed muon scan from May 2018 with new information currently under investigation

# Backup

Tungsten absorber

Time reference given by T0 channels:

Trigger scintillator connected to normal AHCAL channel

Time resolution: 5-6ns

Tungsten absorber

Time reference given by T0 channels:

Trigger scintillator connected to normal AHCAL channel

Time resolution: 5-6ns

2017: Implemented Beam Interface Module (BIF) → provides external clock

### Shift in Calibration Constants

#### Memory cell 14

## Occupancy

# Occupancy Correction

#### occupancyVsHitTime