### ILD Cabling – What we "know" today

Roman Pöschl,

ILD Integration Meeting, February 2019, DESY/Hamburg, Germany

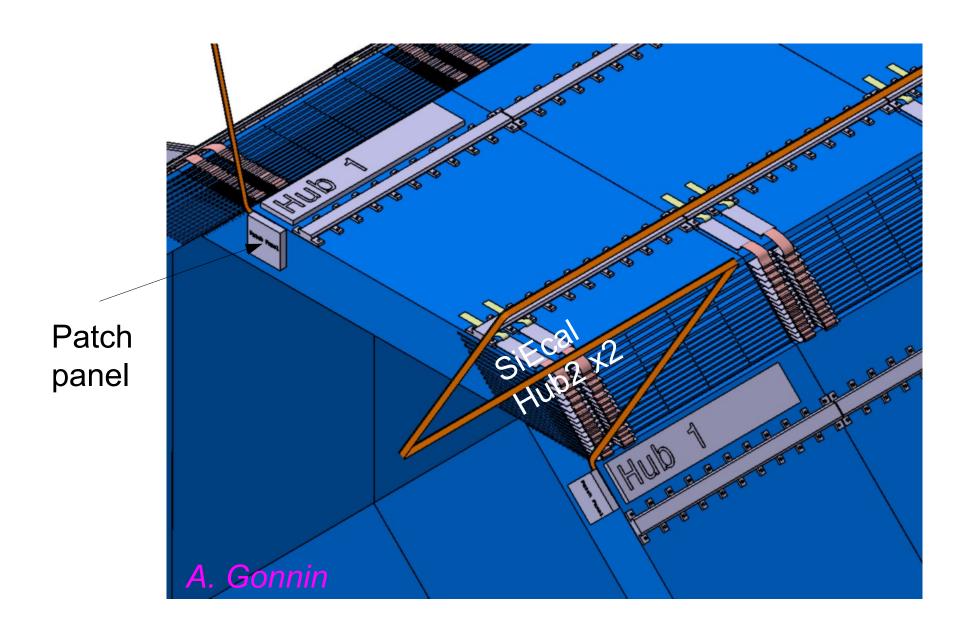

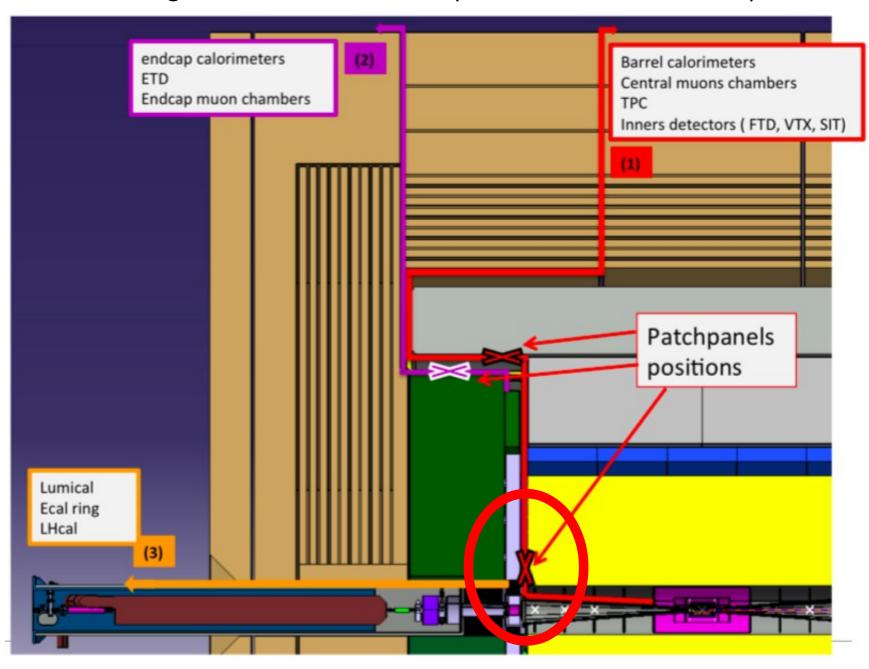

#### **SiEcal – Electrical interfaces**

- SiEcal Patch Panel

- Connection to external supplies and DAQ New since Arlington!!!!

- 1 per barrel stave (octant)

- SiECal internal components

- SiEcal Hub 1

1 per barrel module

=> 5 per barrel stave (octant)

- SiEcal Hub2

10 per barrel module

=> 50 per barrel stave (octant)

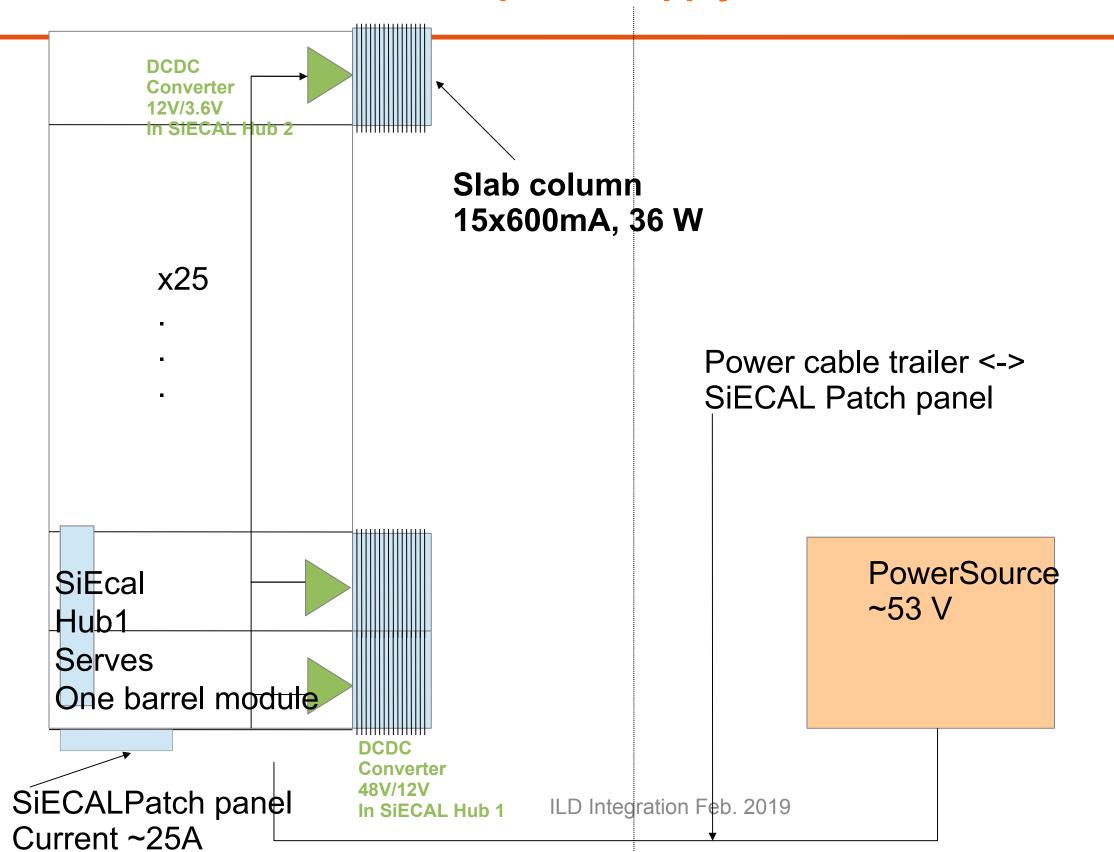

### Scheme of PV power supply for one stave

#### SiEcal - Some numbers

- 0) Prologue: Specific Resistance of Copper rho = 0.0171 [Ohm x mm<sup>2</sup>/m]

- 1a) The (continous) current consumption of a column of slabs is driven

- i) by the consumption of the SL-Boards is (at approx. 4V):  $I_{SI} = 200 \text{ mA} => 400 \text{ mA/slab}$

- ii) by the charging current for the capacitances. The inrush current will be limited to  $I_{C,max} = 100 \text{mA/layer}$ . However, at t>t<sub>0</sub> the current will drop progressively according to  $I=(U_B/R)xexp(-t/RC)$  with  $U_B = Voltage$  of power source and R=Resistance to limit the inrush current, e.g for  $U_B = 4V$ ,  $I_{C,max} = 100 \text{mA} => R=500 \text{hm}$

- 1b) In this scenario it follows that the <u>maximal</u> consumption of a slab is Current:  $I_{S,max} = 2x(200\text{mA} + 100\text{mA}) = 600\text{ mA}$ Power:  $P_{slab} = P_{SL} + P_{RC} = 2x(4Vx0.2A + 4Vx0.1A) =$ **2.4W**(again this drops as the capacitances get charged)

Power consumption of a column of slabs = 15x2.4 W = 36 W

1c) The 4V for SL-Board and capacitance charging is provided by 12V/4V DCDC Converters that sit in Hub2. This hub hosts also the data concentrator cards and by itself consumes around 5 W.

There are two hubs of type Hub2 per column of slab => Total consumption of Hubs/column 10W

These 10 W add to the 36 W above, leading to a total power consumption of a slab column of 46 W.

#### SiEcal - Some numbers cont'd

1) The total power consumption of a stave (=25 columns) is about 25 x 46W =1150 W

To this one has to add the 5x10 W of the 5 hubs of type Hub1

=> Total consumption of a stave 1200 W

There are eight staves in the barrel => Total consumption of barrel 8x1.2kW ~ 10kW

(Endcap will also add ~5kW each but needs to be calculated)

2) These 1200W/stave have to be provided by the main power supply of 48 W from which it follows that current drawn from the power supply is 1200W/48V = 25 A

These 25 A arrive at the SiECAL Patch Panel and will have to distributed to the hubs

3) According to a survey on the web 25 A require a cable with a cross section of about 1.5 mm<sup>2</sup> maybe 2.5 mm<sup>2</sup>. The voltage drop per meter on such a cable at 25 A is

```

\Delta U = (0.0171/1.5)Ohm x 25A = 0.29 Volt => ~6 Volt after 20m in case of 1.5 mm² with a thermal dissipation of 0.29Vx25A ~ 7.5W/m \Delta U = (0.0171/2.5)Ohm x 25A = 0.17 Volt => ~3.4 Volt after 20m in case of 2.5 mm² with a thermal dissipation of 0.17Vx25A ~ 4.3W/m \Delta U = (0.0171/4)Ohm x 25A = 0.11 Volt => ~2.2 Volt after 20m in case of 4 mm² with a thermal dissipation of 0.11Vx25A ~ 2.7W/m

```

Concerning the cable thickness we need to find a compromise between material budget and thermal dissipation

=> Propose to choose 2.5 mm² for the time being (requires coordination with other detector components)

## **Intermezzo – Utility services**

| 05/09/18 | <u> </u>                                   |               |      |                                                                                                                                           |

|----------|--------------------------------------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|          | Sub-detector name                          | ECAL          |      | $Q_{BE}$ $Q_{LV}$ $Q_{PC}$                                                                                                                |

| P_FE     | Power consumption of Front-end Electronics | 17            | kW 🚤 | =20kW                                                                                                                                     |

| Q_PC     | Heat loss in Power Cables                  | 1             | kW < |                                                                                                                                           |

| е        | Efficiency of low voltage power supply     | 90%           |      | 1.5kW 0                                                                                                                                   |

| P_BE     | AC Power input to Back-end Electronics     |               | kW   | Q <sub>D</sub> Cooling line                                                                                                               |

| P_CS     | ectric power to drive Cooling System       | 8             | kW   | Sub-det. Data/HV cable                                                                                                                    |

|          | Type of cooling water for cooling system   | Chilled water |      | Q <sub>CS</sub> Cooling Cooling Cooling                                                                                                   |

|          |                                            |               |      | system Back-end elec./                                                                                                                    |

| P_LV     | AC Power input to Low Voltage power supply | 20            | kW   | HV PS LV power cable                                                                                                                      |

| Q_LV     | Heat loss in Low Voltage power supply      | 2             | kW   |                                                                                                                                           |

| Q_BE     | Heat loss in Back-end Electronics          | 0             | kW   | Low voltage                                                                                                                               |

| Q_CS     | Heat to be extracted from cooling system   | 25            | kW   | PS                                                                                                                                        |

|          |                                            |               |      |                                                                                                                                           |

|          |                                            |               |      | P <sub>LV</sub>                                                                                                                           |

|          |                                            |               |      |                                                                                                                                           |

|          |                                            |               |      | P <sub>FE</sub> : Power consumption of sub-detector Front-end Electronics     Q <sub>D</sub> : Heat loss in sub-det. (= P <sub>FE</sub> ) |

|          |                                            |               |      | Q <sub>PC</sub> : Heat loss in power cables                                                                                               |

|          |                                            |               |      | P <sub>LV</sub> : AC power input to LV PS                                                                                                 |

|          |                                            |               |      | <ul> <li>ε : Efficiency of LV PS (P<sub>LV</sub>*ε= P<sub>FE</sub> +Q<sub>PC</sub>)</li> </ul>                                            |

|          |                                            |               |      | <ul> <li>Q<sub>LV</sub>: Heat loss in the LV PS (=(1-ε)*P<sub>LV</sub>)</li> </ul>                                                        |

|          |                                            |               |      | P <sub>BE</sub> : AC power input to back-end elec./HV power supply                                                                        |

|          |                                            |               |      | Q <sub>BF</sub> : Heat loss in the BE/HV PS (=P <sub>BF</sub> )     P <sub>CS</sub> : Electric power to drive the cooling system          |

|          |                                            |               |      | Q <sub>CS</sub> : Heat to be extracted from cooling system (= Q <sub>D</sub> +P <sub>CS</sub> )                                           |

|          |                                            |               |      |                                                                                                                                           |

|          |                                            |               |      |                                                                                                                                           |

|          |                                            |               |      |                                                                                                                                           |

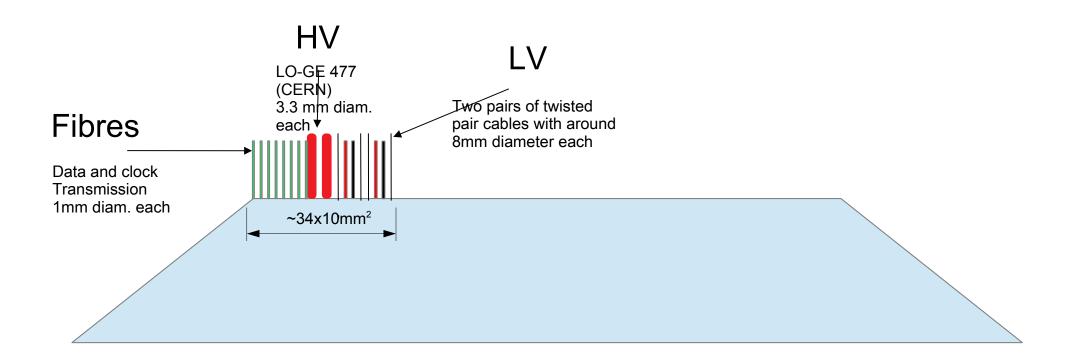

#### SiEcal – Considerations on cables

#### Cables arriving at SiECAL Patch Panel

1) A copper cable of 2.5mm<sup>2</sup> has a diameter of about 1.8mm The cables for LV will be twisted pair cables with an overall diameter of about 4mm Shielding and outer insulation may add another 2mm say 4mm to be generous

=> Including isolation and shielding a cable that includes one twisted pair may have a diameter of up to 8mm We need two of these cables for redundancy

Remark: The radiation length of copper is 14.36 mm

- 2) HV will be brought in a cable of about 3.3mm in diameter, e.g. of type LO-GE No. 477 (CERN Catalogue)

- 3) There will be also optical fibres for data transfer and clock distribution Let's assume eight unidirectional fibres including redundancy The additional material budget is however negligible

While I believe that the dimensions of the cables are about right we need a professional study to identify the correct type of cables and connectors

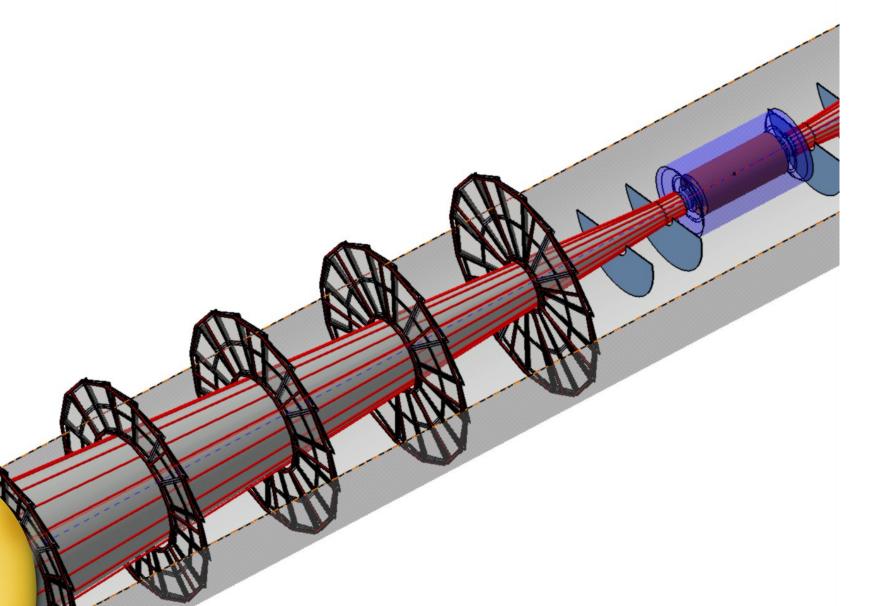

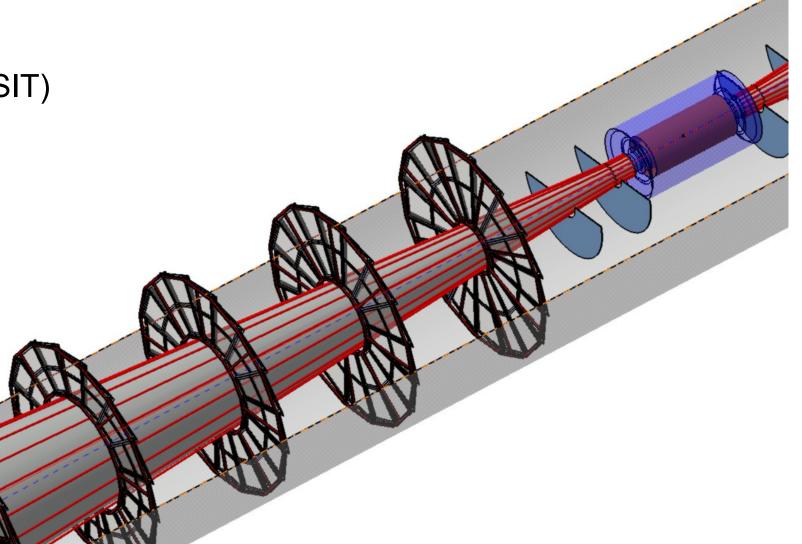

## SiEcal cables – Simple drawing

- Not to scale!!!

- More professional drawing see above and on the following slide

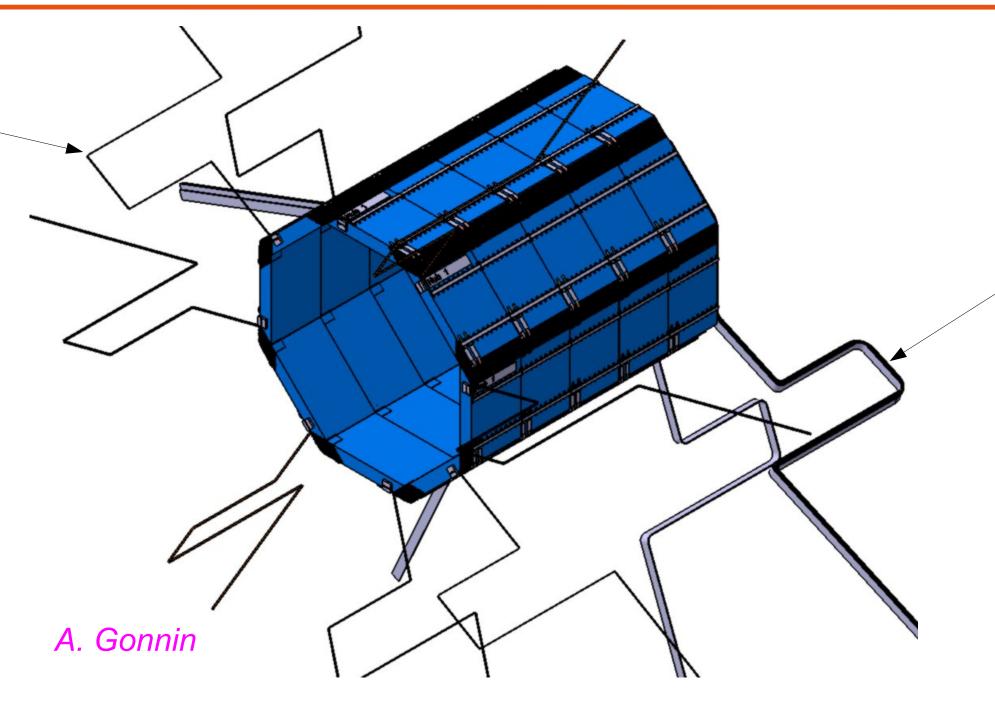

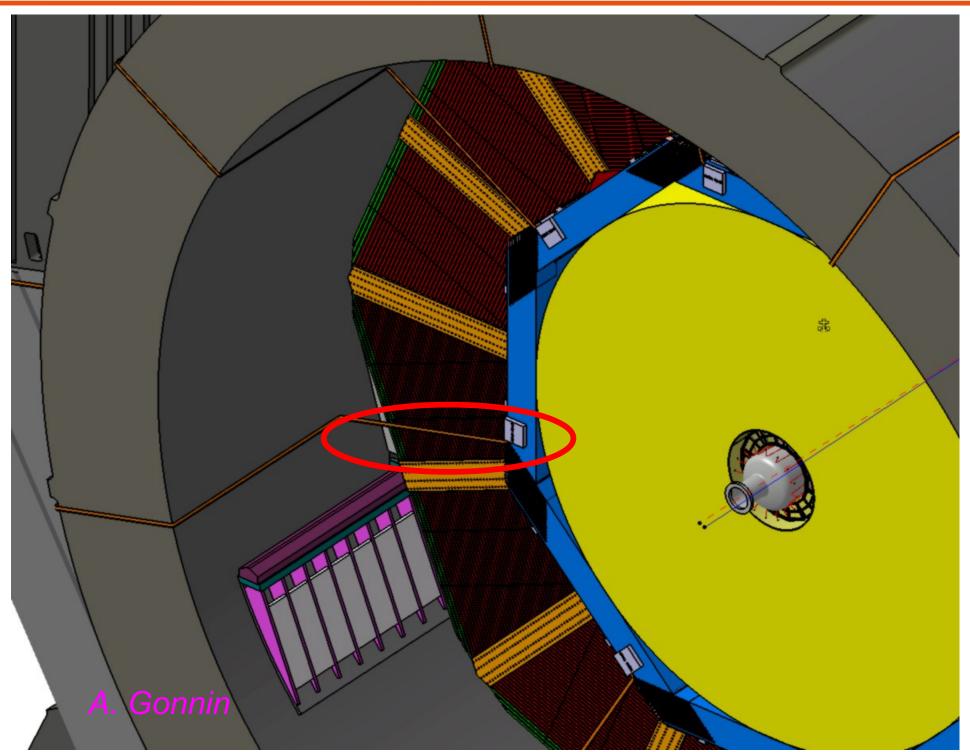

#### SiEcal external cables – In ILD CAD Model

SiEcal

Cooling pipes

(modulo validation

by LPSC Group)

Message SiEcal external cables now in ILD CAD Model

=> Homework done: Can now twist arms of other detectors

ILD Integration Feb. 2019

## Passage of SiEcal cables in front of Hcal - AHCAL

- Conflict with AHCAL electronics

- Will Felix and Katja simply just kill me or is there another solution?

- In ideal case

- SiEcal Cables should arrive Close to Patch Panel

- ... but Patch Panel in conflict with

- TPC Fixation

# Passage of SiEcal cables in front of Hcal - SDHCAL

Cable tray

for inner

detectors

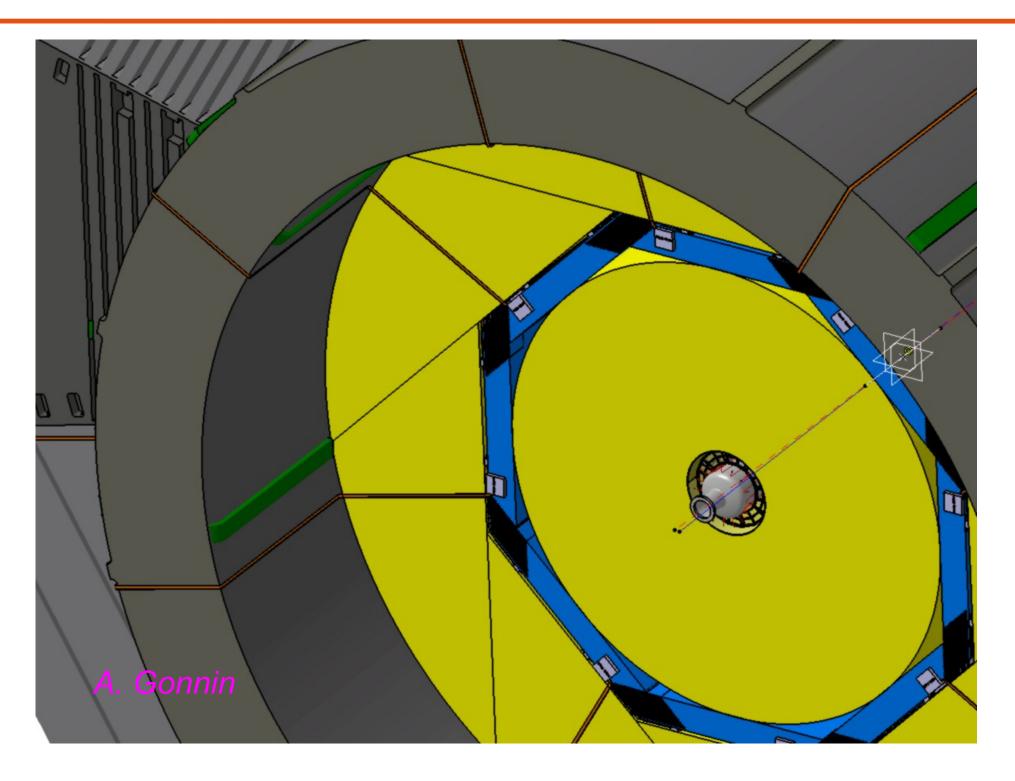

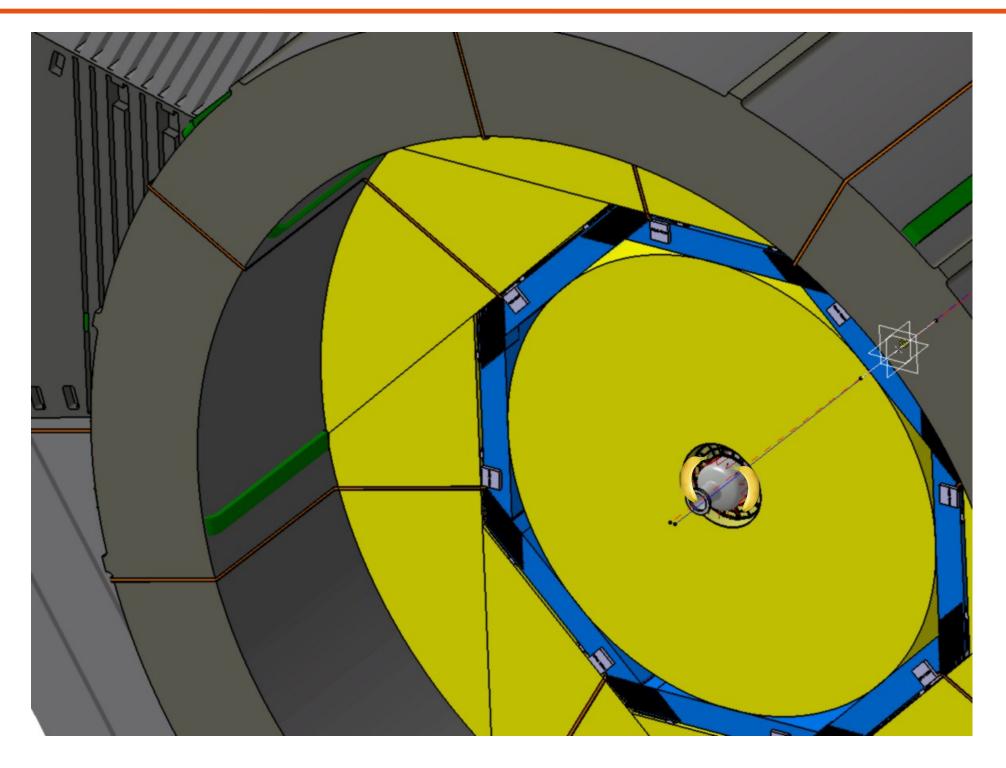

### TPC cables, inner detector cables and SiEcal cables

Good News!!!

No obvious conflict between

Cables from/to inner detectors

TPC cables

SiEcal cables

Caveat: This is a view on the side Where according to the drawings Before the cooling system sits

Need to repeat the exercise with full set of SiEcal cooling pipes

# **Cabling - Inner detectors**

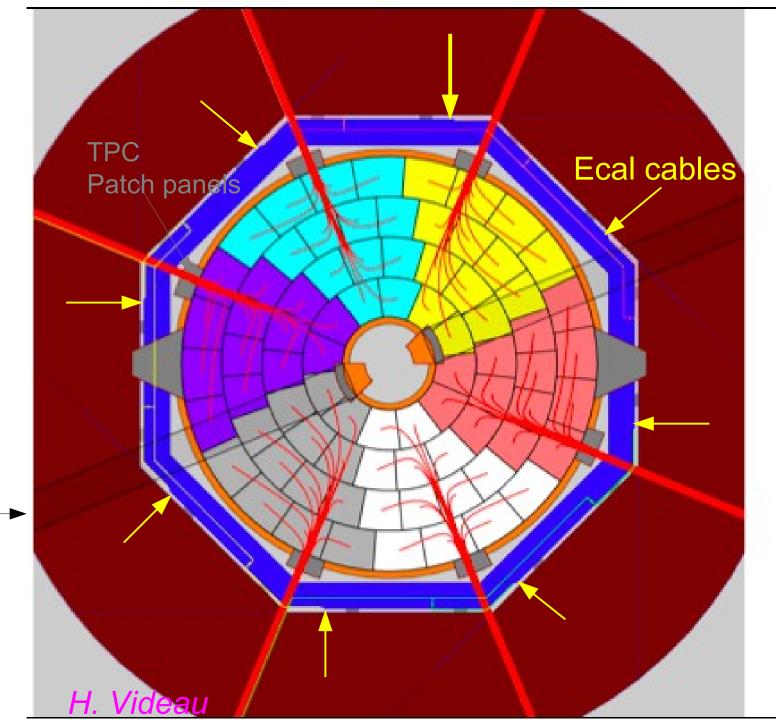

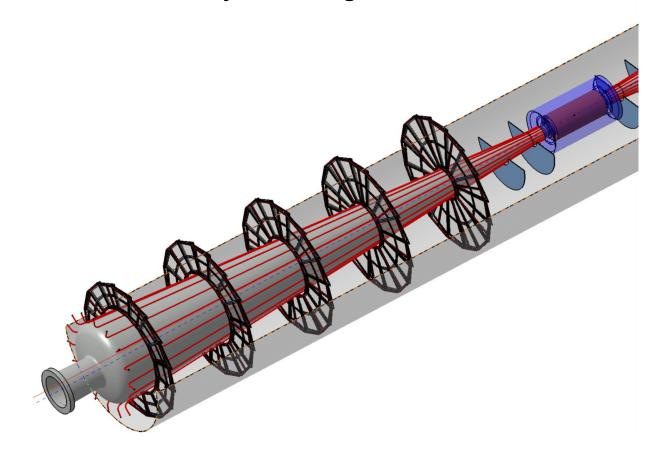

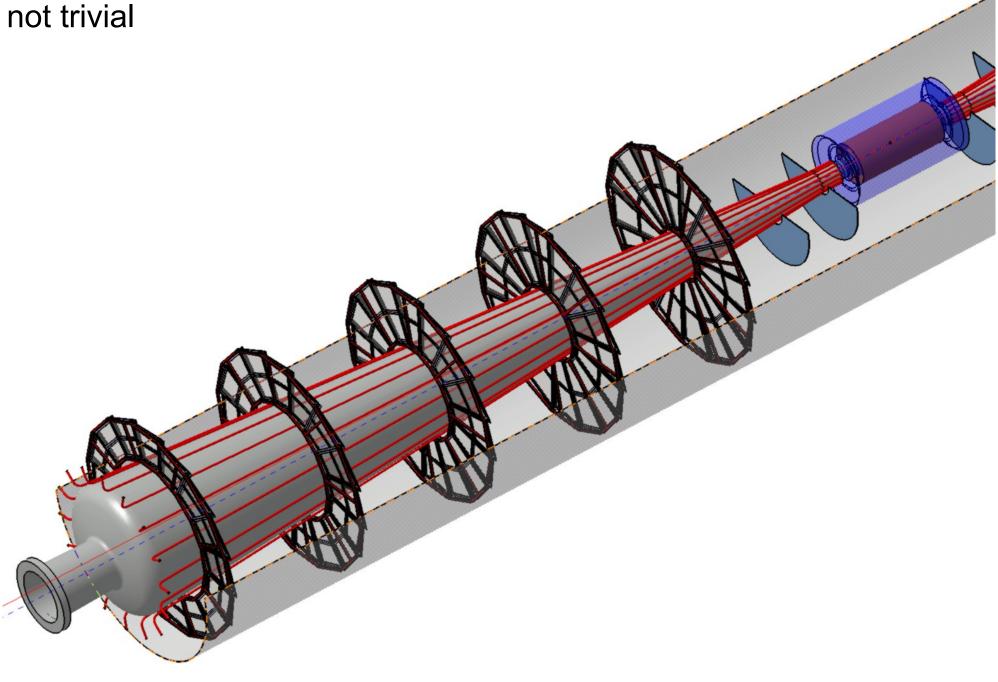

### Cabling scheme à la DBD (Clerc/Cornat/Videau)

# **Cabling - Inner detectors**

### Cabling scheme à la DBD (Clerc/Cornat/Videau)

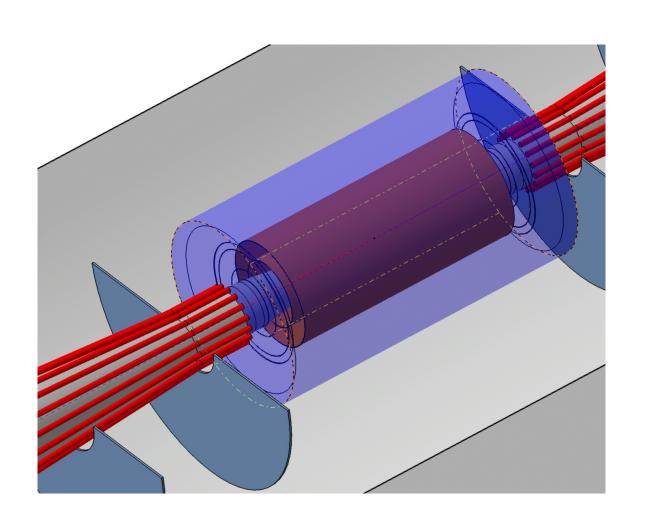

### Cabling inner detectors – State of the art

"Review" by A. Besson, H. Videau, A. Gonnin and R.P. Yesterday evening

A. Gonnin

- Cables (or their place holders) are equally distributed around beam pipe

- For connection with patch panel regrouping into two strands around 3h and 9h positions

• The inner detector patch panel is not trivial

The inner detector patch panel is not trivial

- The inner detector patch panel is not trivial

- It has to serve all inner detectors

- Has to comply with TPC inner radius

- What kind of connections

- In principle everything is too bulky

- Has to provide power and readout

- How active e.g. Copper/fibre transitions?

- Today we can still joke but after 8<sup>th</sup> of March have to stop joking ;-)

Requires dedicated study (meeting)

• The inner detector patch panel is not trivial

• It has to serve all inner detectors (VDET, FTD, SIT)

Has to comply with TPC inner radius

What kind of connections

In principle everything is too bulky

Has to provide power and readout

• How active e.g. Copper/fibre transitions?

• Today we can still joke but after 8<sup>th</sup> of March have to stop joking ;-)

Requires dedicated study (meeting)

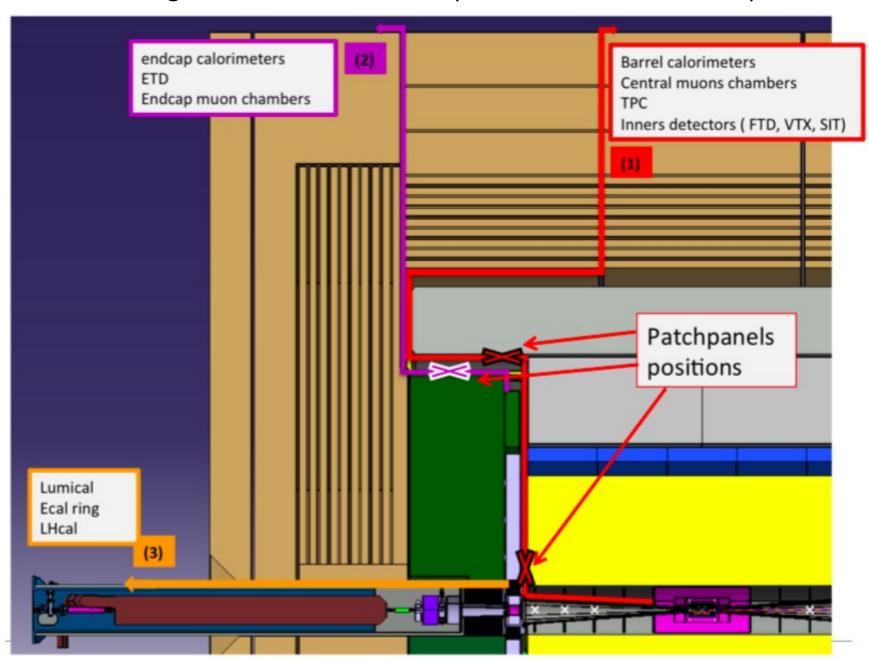

# Cabling inner detectors – Patch panel – Global view

## **Summary and outlook**

- Review of cabling takes slowly shape (Sorry for being slow)

- No major issues with central detector

- Have to look closer at end with SiEcal cooling system

- Closer look at Hcals needed

- Inner detectors are critical

- Significant amount of cables

- Patch panel will be extremely complicated and requires dedicated engineering design

- This is maybe true for all patch panels but here in particular

- For all detectors: Survey on required connectors and specifications/constraints on/from bending

- As far as you have it please send CAD Drawings of your cabling to Alexandre

- The best way to identify and solve unspotted conflicts