#### Study for Retriggers of SiW-ECAL

Yu Kato

The University of Tokyo

CALICE Analysis Meeting 20th May 2020

## What are Retriggers?

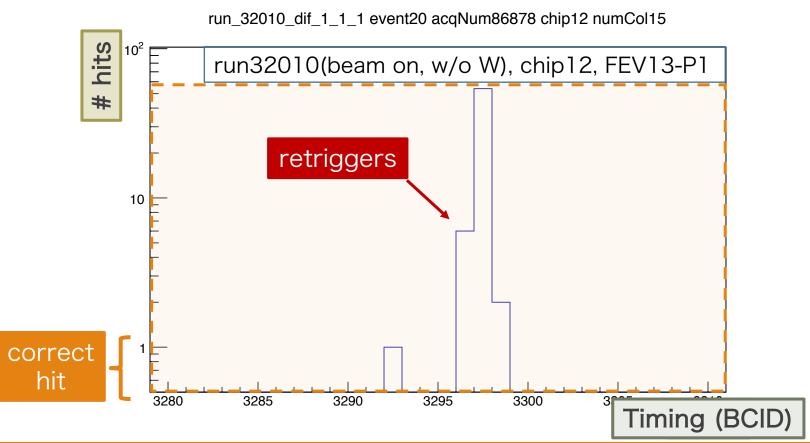

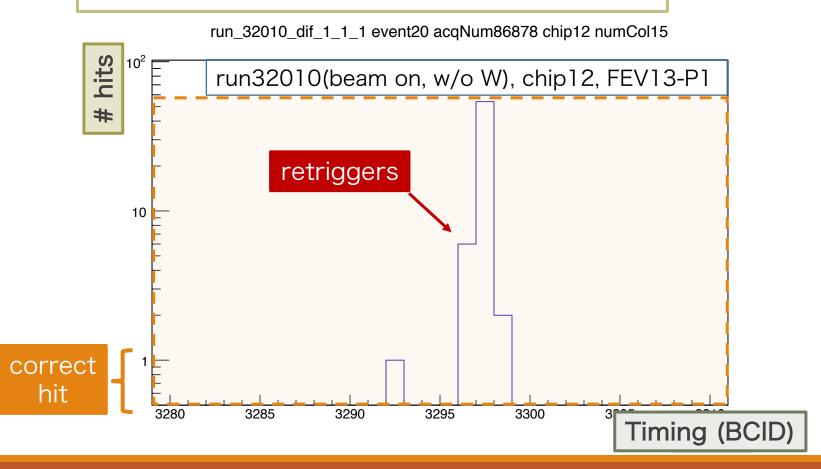

- SiW-ECAL technological prototype has an issue called "retriggers".

- many fake hits just after correct hit(s)

- consecutive BCIDs

- Memory cells are occupied by retriggers and may fail to store normal events.

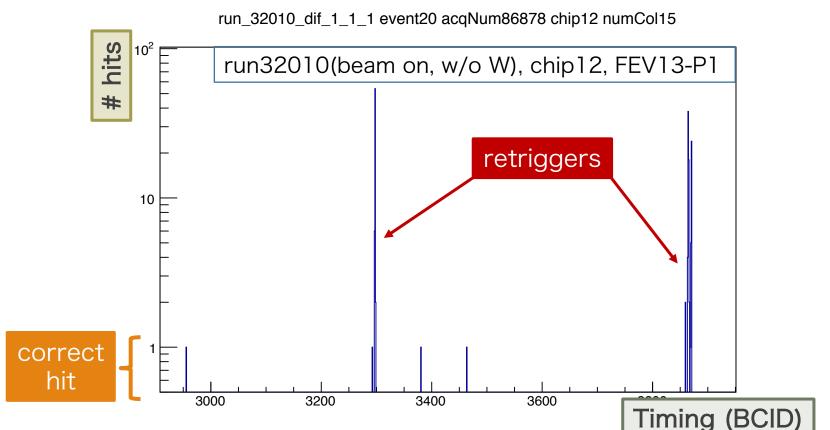

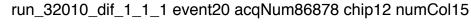

## What are Retriggers?

- SiW-ECAL technological prototype has an issue called "retriggers".

- many fake hits just after correct hit(s)

- consecutive BCIDs

- Memory cells are occupied by retriggers and may fail to store normal events.

## What are Retriggers?

- SiW-ECAL technological prototype has an issue called "retriggers".

- many fake hits just after correct hit(s)

- consecutive BCIDs

- Memory cells are occupied by retriggers and may fail to store normal events.

## Target of this study

- > Develop retrigger discrimination method

- Evaluate retriggers

- Consider its cause

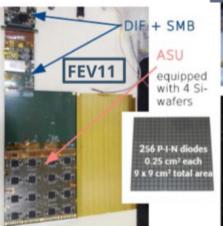

#### Data acquisition mechanism of SiW-ECAL

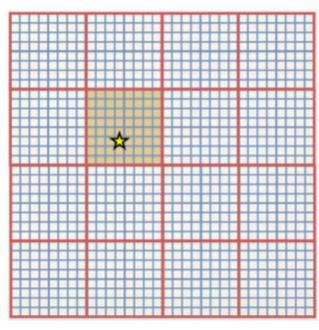

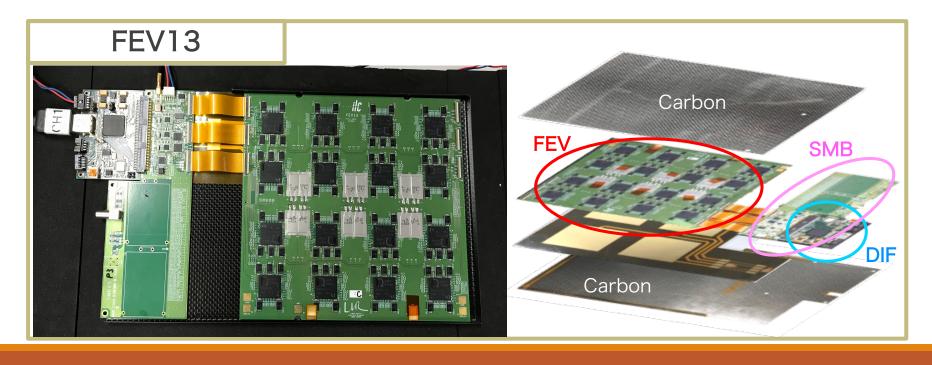

#### Geometrical structure

- Si pixel: 5.5 × 5.5 mm<sup>2</sup>

- $\cdot 32 \times 32 = 1024 \text{ ch / slab}$

- 16 ASICs / slab

- 4 Si wafers / slab

#### Readout information

- Bunch Crossing ID (BCID)

f = 5 MHz, Δt = 0.2 μs

- Hit bit

- self-triggered by each channel

- Analogue output (Any two of the three)

- Charge <sup>1</sup>High/<sup>2</sup>Low gain, <sup>3</sup>Timing

#### Readout mechanism

- independently on each ASIC

- 1. Some tracks are triggered within one BCID interval (0.2 µs).

- 2. Analogue outputs from all channels are stored in memory cells (15 SCAs).

- 3. After the acquisition phase(5 Hz, ~ 2.5 ms), all stored data is read out.

## Studies for retriggers

#### Setup

- We used following data in this talk.

- The data used for evaluation was obtained in TB2019 @ DESY.

- All the results are based on FEV13-K2 so far.

| run   | beam             | Output mode | W absorber |

|-------|------------------|-------------|------------|

| 32010 | On<br>(e- 3 GeV) | ADC         | None       |

ADC mode: Charge High(×10) & Low(×1)

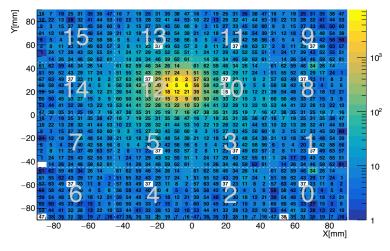

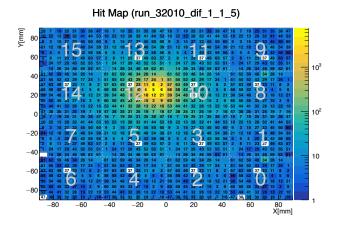

Hit Map (run\_32010\_dif\_1\_1\_5)

run32010(beam on, w/o W), chip12, FEV13-K2

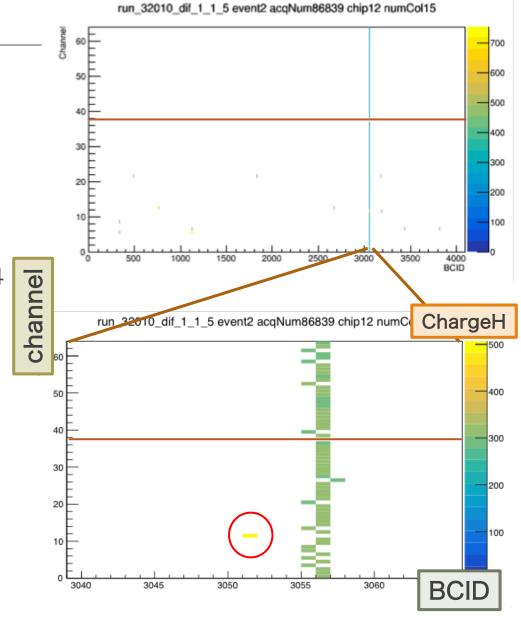

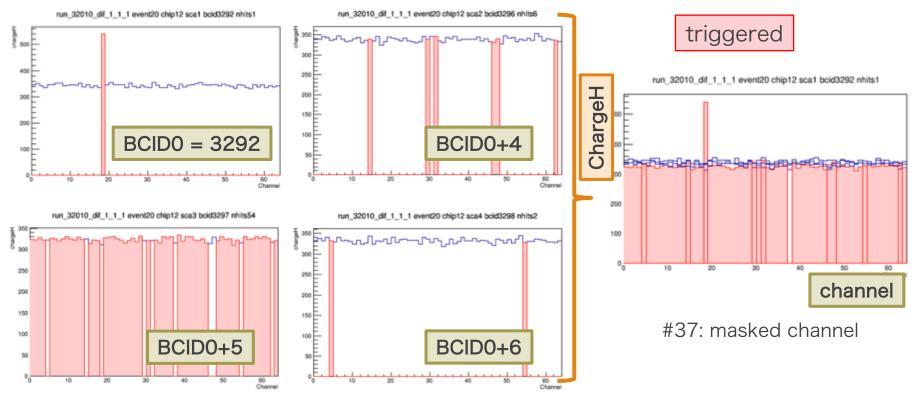

### Retriggers: Structure

#### BCID vs Triggered channels

- The retriggers looks "line".

- Almost all channels are triggered.

- except <u>masked channel</u> (ch. 37)

- sometimes one or two channels do not triggered.

- Many consecutive hits occur after 4

- 6 BCIDs from the hit that looks normal. → "Induction"

#### Discrimination Method

- Previous one

- $\triangleright \Delta$  boid is less than 15 (adjustable) in 3 consecutive events

- To extract only normal hits undoubtedly

- Exclude even the induction events

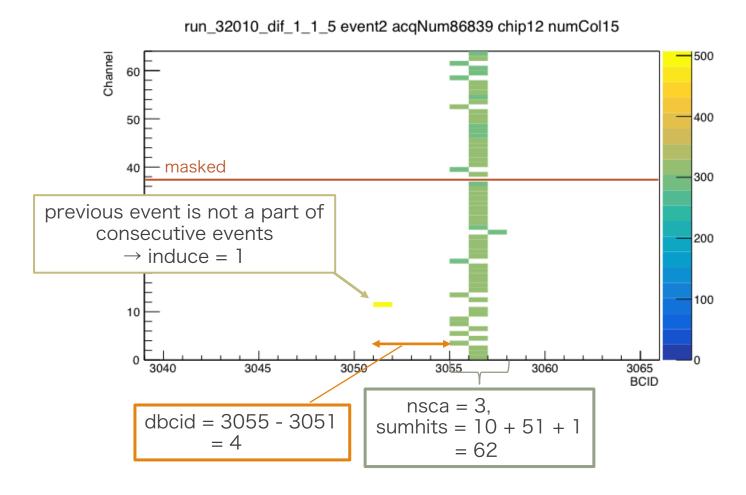

- Developing one

- To identify retriggers

- 1. Merge triggers recorded by consecutive boid

- 2. Make the variables below to evaluate whether retrigger

- nsca: Number of merged memory cells

- sumhits: Total number of hits

- dbcid: bcid interval between the induction and the start of the merged triggers

- 3. Set some condition to discriminate normal / induction / retrigger

- currently: dbcid < 10</li>

- work in progress

#### Discrimination Method

- Example:

- The variables are saved in each time consecutive boids are found.

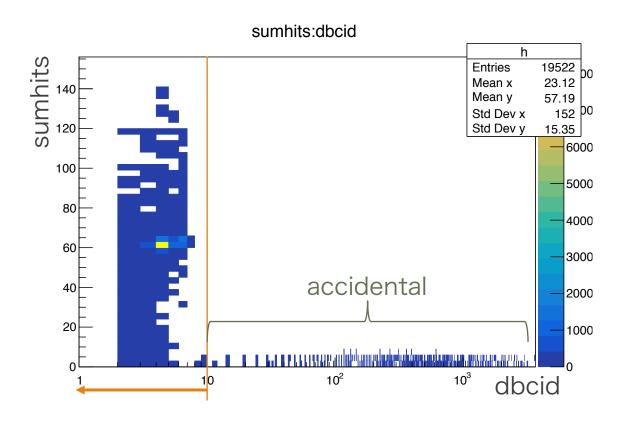

#### dbcid vs sumhits

- Cut by dbcid is necessary to exclude accidentally consecutive events.

- dbcid < 10 ( preliminary )</li>

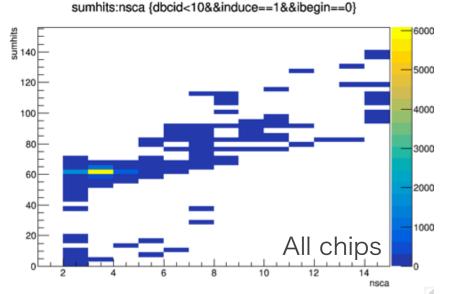

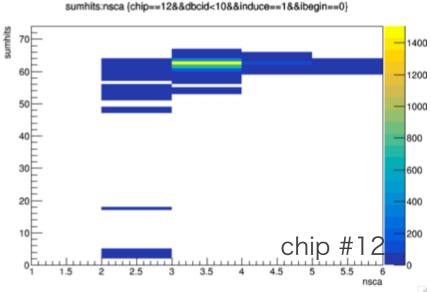

#### nsca vs sumhits

- Basic cut is applied.

- dbcid < 10, induce = 1, not the begin of acquisition</li>

- In all chips result, there are a few events in which both variables are large.

- > They would be multi-retriggers.

- In only the irradiated chip, almost all the entry is [nsca = 3 & sumhits =62].

### Retrigger Rate

run\_32010\_dif\_1\_1\_5\_retrigger.txt

RESULT

Triggered = Empty + Retriggers + Normal Normal ⊃ Induction

| IVEDUE                               | 1          |        |             | L          |         |          |                                   |  |

|--------------------------------------|------------|--------|-------------|------------|---------|----------|-----------------------------------|--|

| Acq Cycle: 14469, Acq Recorded: 7068 |            |        |             |            |         |          |                                   |  |

| Chip,                                | Triggered, | Empty, | Retriggers, | Induction, | Normal, | FullSCA, | <pre>Rate(Induction/Normal)</pre> |  |

| 0                                    | 2819       | 70     | 1907        | 297        | 842     | 93       | <b>0.</b> 353                     |  |

| 1                                    | 3225       | 59     | 2224        | 350        | 942     | 84       | 0.372                             |  |

| 2                                    | 2928       | 66     | 2007        | 322        | 855     | 77       | 0.377                             |  |

| 3                                    | 5421       | 154    | 3567        | 653        | 1700    | 104      | 0.384                             |  |

| 4                                    | 2855       | 73     | 1984        | 305        | 798     | 76       | 0.382                             |  |

| 5                                    | 5288       | 175    | 3230        | 667        | 1883    | 83       | 0.354                             |  |

| 6                                    | 2439       | 76     | 1661        | 238        | 702     | 80       | 0.339                             |  |

| 7                                    | 3319       | 87     | 2274        | 374        | 958     | 89       | 0.390                             |  |

| 8                                    | 3763       | 361    | 2249        | 425        | 1153    | 87       | 0.369                             |  |

| 9                                    | 2905       | 83     | 1938        | 286        | 884     | 87       | 0.324                             |  |

| 10                                   | 18520      | 788    | 10149       | 1895       | 7583    | 196      | <b>0.</b> 250                     |  |

| 11                                   | 4809       | 123    | 3215        | 521        | 1471    | 107      | 0.354                             |  |

| 12                                   | 61283      | 2635   | 13688       | 3805       | 44960   | 1769     | 0 <b>.</b> 085                    |  |

| 13                                   | 5280       | 172    | 3288        | 635        | 1820    | 93       | 0.349                             |  |

| 14                                   | 4116       | 96     | 2778        | 488        | 1242    | 74       | 0.393                             |  |

| 15                                   | 2642       | 86     | 1666        | 309        | 890     | 78       | 0.347                             |  |

- Many retriggers are occurred in the irradiated chips.

- > The electron tracks should induce the retriggers.

- The rate of induction/normal seems to be higher in chips far from beam spot.

- > Is there any causes other than the tracks?

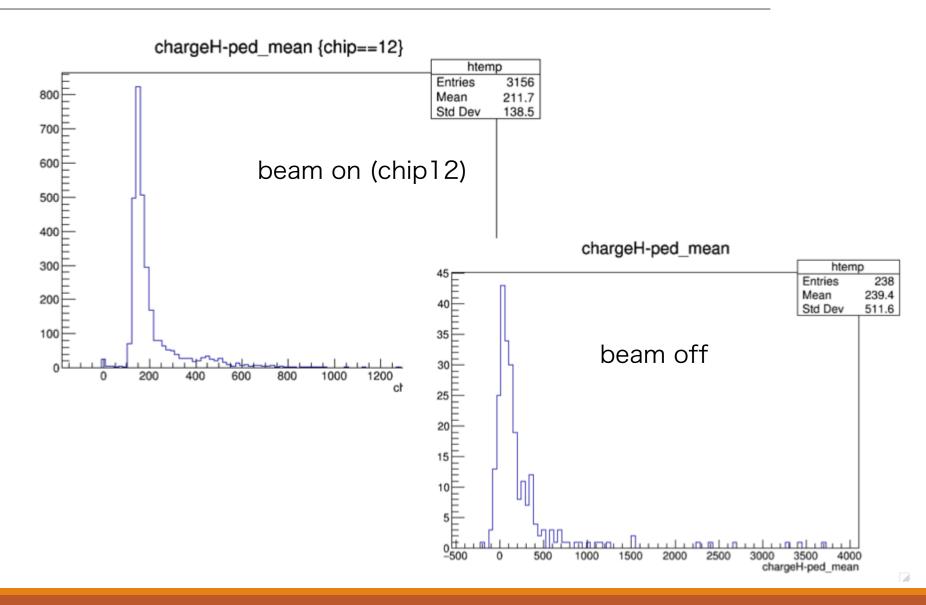

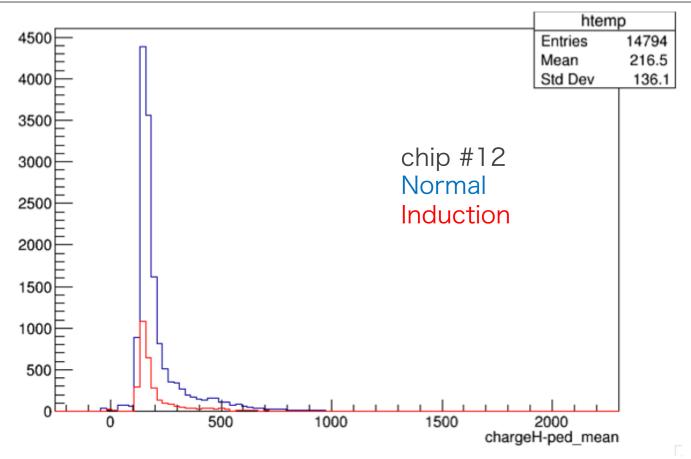

## Comparison of triggered charge

- No significant difference between normal and induction distribution.

- Induction can be treated as a normal hit? ( Previously excluded. )

## Summary

- New method to discriminate the retriggers is under developing.

- The retrigger rate is evaluated using current method.

- Many retriggers are occurred in the irradiated chips.

- > The electron tracks should induce the retriggers.

- The rate of induction/normal seems to be higher in chips far from beam spot.

- Is there any causes other than the tracks?

- No significant difference of charge distribution between normal and induction.

- Induction can be treated as a normal hit? (Previously excluded.)

#### To do

- □ Update the method which can identify the multi-retriggers.

- Comparison of the pedestal between normal and induction.

- □ Check the effect between each chips in the board.

- Verification using a test board

- after the situation of COVID-19 calms down.

# additional

## SiW-ECAL technological prototypes

Vincent Boudry, LCWS2019 Sendai

#### ASU: 12+ years of R&D

#### Most complex element: electro-mechanical integration

- Distrib / Collect signals from VFE (ASICs),

Analog & Digital with dyn. range ≥ 7500

- Mechanical placer & holder for Wafers → precision

- Thickness constraints

#### 3 versions working

- with S/N<sub>Trig</sub> ≥  $\sim$ 12 (for 320µm)

ILD SIW-ECAL Adaptative design | LCWS

| Milestone                             | Date | Object Details                                               |                                          | REM                                               |

|---------------------------------------|------|--------------------------------------------------------------|------------------------------------------|---------------------------------------------------|

| 1 <sup>st</sup> ASIC proto            | 2007 | SK1 on FEV4                                                  | 36 ch, 5 SCA                             | proto, lim @ 2000<br>mips                         |

| 1 <sup>st</sup> ASIC                  | 2009 | SK2                                                          | 64ch, 15 SCA                             | 3000 mips                                         |

| 1 <sup>st</sup> prototype of a<br>PCB | 2010 | FEV7                                                         | 8 SK2                                    | СОВ                                               |

| 1 <sup>st</sup> working PCB           | 2011 | FEV8                                                         | 16 SK2 (1024<br>ch)                      | CIP (QGFP)                                        |

| 1 <sup>st</sup> working ASU<br>in BT  | 2012 | FEV8                                                         | 4 SK2 readout<br>(256ch)                 | best S/N ~ 14<br>(HG), no PP<br>retriggers 50–75% |

| 1st run in PP                         | 2013 | FEV8-CIP                                                     |                                          | BGA, PP                                           |

| 1 <sup>st</sup> full ASU              | 2015 | FEV10                                                        | 4 units on test<br>board<br>1024 channel | S/N ~ 17–18 (High<br>Gain)<br>retrigger ~ 50%     |

| 1st SLABs                             | 2016 | Slab:FEV11                                                   | 10 units, 320μm                          |                                                   |

| pre-calo                              | 2017 | FEV 11                                                       | 7 units                                  | S/N ~ 20 (12) <sub>Trig.</sub> 6–<br>8 % masked   |

| 1 <sup>st</sup> technological<br>ECAL | 2018 | 10 SLAB:<br>5 FEV11 320µm<br>5 FEV13 650*µm<br>Compact stack | SK2 & SK2a<br>(⊃timing)                  | Improved S/N<br>(1/64 masked ch.)<br>Timing       |

| 1 <sup>st</sup> COB                   | 2019 | FEV12-COB                                                    | 1 wafer, 500µm                           | S/N ~ 22                                          |

|                                       |      |                                                              |                                          |                                                   |

Vincent.Boudry@in2p3.fr

## Major changes in FEV11→13

- ➤ ASIC: SKIROC2 → 2A

- individual threshold control

- improvement on TDC resolution

- Separation of power layers

- power supply for analogue and digital

- improvement on noise level

- Capacitor for Power Pulsing

- 0.4 mm thickness, 40 mF x 6

- Carbon fiber frame/cover

- Smaller SMB footprint

#### Analogue core: SKIROC2A

Outputs

ADC mode: Charge High(x10) & Low(x1) 15 cells Analog TDC mode: Timing & Charge (High or Low or Auto) memories Time feedback 12 bit-ADC Ramp tagging capacitance 64 channels Sel ADC test? Analog signal (slow control) C2=1.6pF Preamp Slow Sh. G1 R2=100k R1=4k C1=45pF READ Signal W-I out\_tdc Depth=15 ssh\_G1, ssh G10 out ssh G1 C2=3pF conversion out ssh G10 ~w Slow Sh. G10 R1=22k C1=8pF READ Gain\_selection Vth gs TDC\_on? (slow control) Gain10 Fast Shaper ~~ 5p.10p. 15p or 20pF HOLD Auto Gain ? Forced Gain ? (slow control) 8-bit Delay Box: vref fs Test Vth\_trigge Sel FlagTDCb Ext ? Forced FlagTDCb ? pulse Trigger 4-bit DAC (slow control) out\_trigger FLAG TDC fine tuning individual trigger 10-bit DAC 10-bit DAC (from Digital ASIC) threshold adjustment

arXiv:1801.02024

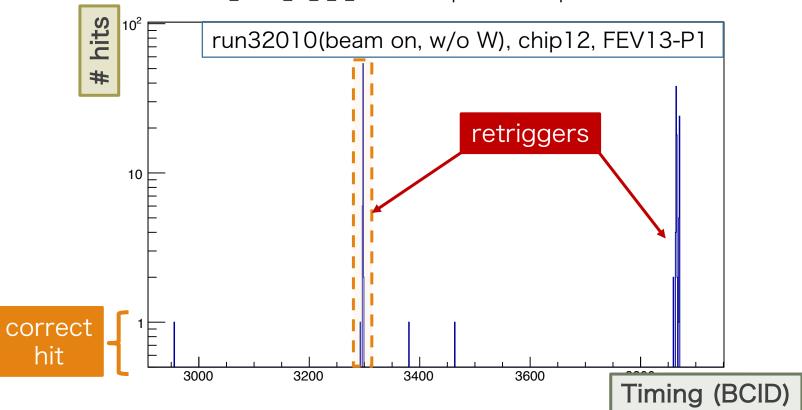

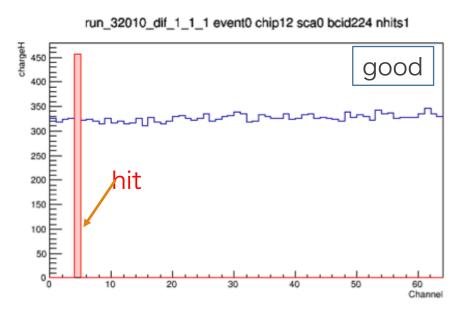

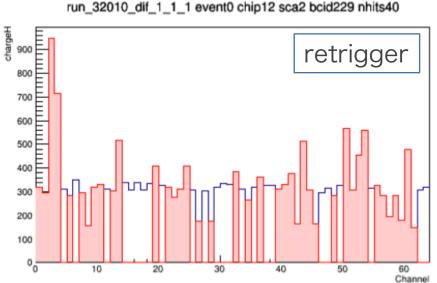

### Retriggers: Structure

#### Trigger & Charge

run32010(beam on, w/o W), chip12, FEV13-P1

- Even the channels which charge is around pedestal level are triggered.

- Fast shaper (trigger line) is presumed to be affected by retriggers.

## Retriggers

- trigger vs charge

- Which shaper has problems that cause retriggers?

- The charges and hits are compared between good/retrigger events.

- Even the channel which charge is lower than pedestal is triggered.

- > Fast shaper has some problems in retrigger?

## Charge of Induction hits